FPGA实训报告.docx

《FPGA实训报告.docx》由会员分享,可在线阅读,更多相关《FPGA实训报告.docx(27页珍藏版)》请在冰豆网上搜索。

FPGA实训报告

1.FPGA硬件系统设计

1.1功能要求

利用所给器件:

一个8位拨码开关(见图1-1),排针40×1,芯片DAC0832×1,芯片LM358×1,一个电位器构成硬件电路,实现与FPGA相连,输出正弦波,三角波,锯齿波,方波。

(图1-1)

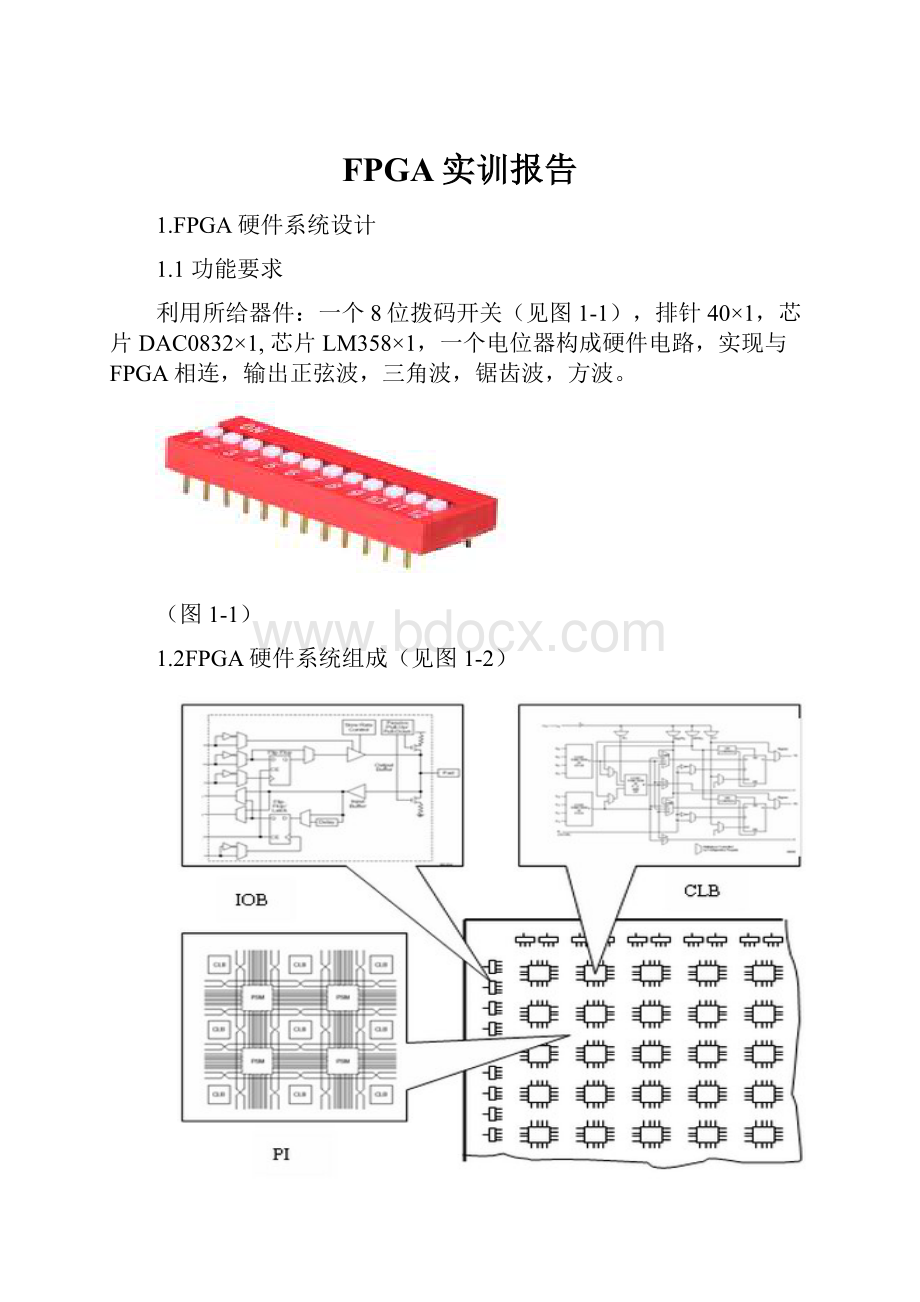

1.2FPGA硬件系统组成(见图1-2)

(图1-2)

FPGA框架结构由三部分组成:

可编程输入/输出模块I/OB(I/OBlock)——I/OB:

位于芯片内部四周,主要由逻辑门、触发器和控制单元组成。

在内部逻辑阵列与外部芯片封装引脚之间提供一个可编程接口。

可配置逻辑模块CLB(ConfigurableLogicBlock)——CLB:

是FPGA的核心阵列,用于构造用户指定的逻辑功能,不同生产厂商的FPGA器件其不同之处主要在核心阵列。

每个CLB主要由查找表LUT(LookUpTable)、触发器、数据选择器和控制单元组成。

可编程内部连线PI(ProgrammableInterconnect)——PI:

位于CLB之间,用于传递信息。

编程后形成连线网络,提供CLB之间、CLB与I/OB之间的连线。

1.3FPGA最小系统简介(见图1-3)

(图1-3)

1.3.1FPGA最小系统板(见图1-4)

(图1-4)

1.3.2下载接口

Alter提供常用的编程连接电缆有4种:

(1)ByteBlaster配置电缆

(2)ByteBlasterMV配置电缆

(3)MasterBlaster/USB配置电缆(USB–Blaster)

(4)BitBlaster配置电缆

串口连接时编程电缆选择:

可以选择BitBlaster或MasterBlaster配置电缆;

并口连接时编程电缆选择:

可以选择ByteBlaster或ByteBlasterMV配置电缆;

USB连接时编程电缆选择:

选择MasterBlaster配置电缆。

ByteBlasterMV配置:

下载电缆通过PC机并口将编程数据配置到FPGA中,与PC机并口相连的是25针插头,与PCB板相连的是10针插头。

提供APS方式和JTAG方式两种下载方式,APS方式用于Cyclone、APEXⅡ、APEX20K、APEXlK、Mercury、Excalibur、FLEXl0K、FLEX8000和FLEX6000等器件的配置;JTAG方式用于编程或配置含有JTAG接口的芯片。

本次实验验选择APS口(如图1-5)

(图1-5)

1.4FPGA外围电路设计

1.4.1拨码开关电路设计(如图1-6)

(图1-6)

共有8个开关,K1,K2控制波形(正弦波,三角波,锯齿波,方波),K3~K8控制频率变换。

本实验中开关一端与FPGA相连,另一端与电源相连,但是这样做不安全,会影响FPGA,因而在开关与电源之间接一个电阻,实验中用了一个330*8的排阻,电源脚

(1)接+3.3V。

每个开关流过电流为3.3÷330=10mA。

1.4.2DAC0832电路设计

1.4.2.1DAC0832芯片简介

DAC0832是采用CMOS/Si-Cr工艺实现的8位D/A转换器,转换周期为1μs。

该芯片包含8位输入寄存器、8位DAC寄存器、8位D/A转换器。

DAC0832中有两级锁存器,第一级即输入寄存器,第二级即DAC寄存器,可以工作在双缓冲方式下。

1.4.2.2DAC0832芯片框图与引脚图

(如图1-7)

(图1-7)

引脚特性:

1.D7~D0:

8位数据输入端

2.ILE:

输入寄存器锁存允许信号

3.CS#:

芯片选择信号

4.WR1#:

输入寄存器写信号

5.XFER#:

数据传送信号

6.WR2#:

DAC寄存器写信号

7.VREF:

基准电压,-10V~+10V

8.Rfb:

反馈信号输入端

9.IOUT1:

电流输出1端

10.IOUT2:

电流输出2端

11.VCC:

电源

12.AGND:

模拟地

13.DGND:

数字地

1.4.2.2DAC0832的三种工作方式

(如图1-8)

双缓冲单缓冲直通

(图1-8)

本实验DAC0832的工作方式为直通。

1.4.2.3FPGA与DAC0832接口电路原理图

(如图1-9)

(图1-9)

分析:

D7~D0:

与FPGA对应接口相连;CS#、WR1#、WR2#、XFER#、AGND、DGND相连接地,构成直通工作方式;VREF、VCC、ILE接+5V;IOUT1,IOUT2分别接运放负端,正端;Rfb加一电位器与运放输出相连,作为输出。

DAC0832是电流型输出器件,因此需要加一个运放,实验中用到LM358。

1.4.3LM358电路介绍

1.4.3.1LM358芯片简介

LM358内部包括有两个独立的、高增益、内部频率补偿的双运算放大器,适合于电源电压范围很宽的单电源使用,也适用于双电源工作模式,在推荐的工作条件下,电源电流与电源电压无关。

它的使用范围包括传感放大器、直流增益模块和其他所有可用单电源供电的使用运算放大器的场合。

1.4.3.2LM358芯片引脚图(如图1-10)

(图1-10)

1.4.3.3LM358的工作方式

LM358内部有2个运算放大器,因此可以使用单运放,也可以使用双运放,本实验中采用单运放。

1.5硬件电路调试及结果分析

结果如图(1-11)

(图1-11)

分析:

设计了一个正弦波,但是调试后发现有非常大的毛刺,之后检查发现时由于相位控制字未锁定造成,后已解决。

2.基于DDS技术的信号发生器设计

2.1功能要求

利用频率合成技术,使某一(或多个)基准频率,通过一定的变换与处理后,形成一系列等间隔的离散频谱;根据特定公式取点,在QuartusⅡ软件进行仿真,经过USB–Blaster在APS口下载到FPGA板上,再与硬件连接,在示波器观察波形及其参数的过程。

2.2整体设计

如图(2-1)

(图2-1)

2.3DDS技术的基本原理

2.3.1频率合成技术

频率合成技术:

利用频率合成的方法,使某一(或多个)基准频率,通过一定的变换与处理后,形成一系列等间隔的离散频谱。

2.3.2DDS技术简介

直接数字频率合成器(DDS)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术,它是目前最为典型、应用最广泛的一种频率合成技术。

它工作频率范围很宽;极短的频率转换时间;极高的频率分辨力;有任意波形输出能力;数字调制性能好等优点。

2.3.3DDS基本结构

如图(2-2)

(图2-2)

2.4程序设计

2.4.1正弦波产生程序设计及仿真

(1)程序的功能:

实现正弦波输出

(2)编程方式

用c语言编程,导出1024个点,形成.mif文件,正弦波的公式为

,其中

C程序为:

#include

#include

main()

{inti;

floats;

for(i=0;i<1024;i++)

{s=sin(atan

(1)*8*i/1024);

printf("%d:

%d;\n",i,(int)((s+1)*1023/2));

}

}

(3)结构图或实体图

如图(2-3)

(图2-3)

(4)仿真波形及分析

如图(2-4)

(图2-4)此图为每个点的数据

具体波形图如图(2-5)

(图2-5)

2.4.2三角波产生程序设计及仿真

(1)程序的功能:

实现三角波输出

(2)结构图或实体图

如图(2-6)

(图2-6)

(3)仿真波形及分析

如图(2-7)

此图为每个点的数据(图2-7)

具体波形图如图(2-8)

(图2-8)

2.4.3锯齿波产生程序设计及仿真

(1)程序的功能:

实现锯齿波输出

(2)结构图或实体图

如图(2-9)

(图2-9)

(3)仿真波形及分析

如图(2-10)

此图为每个点的数据(图2-10)

具体波形图如图(2-11)

(图2-11)

2.4.4方波产生程序设计及仿真

(1)程序的功能:

实现方波输出

(2)编程方式

mif文件手动输入,0,-1……………输入

(3)结构图或实体图

如图(2-12)

(图2-12)

(4)仿真波形及分析

如图(2-13)

此图为每个点的数据(图2-13)

具体波形图如图(2-14)

(图2-14)

2.4.5顶层程序设计及仿真

(1)程序的功能

拨动开关1,2,输出四种不同波形,分别为正弦波(K1=0,K2=0),三角波(K1=0,K2=1),锯齿波(K1=1,K2=0),方波(K1=1,K2=1);剩下六个开关控制频率,频率范围为50Hz~3000Hz,每个开关控制50Hz频率。

(2)结构图或实体图

如图(2-15)

(图2-15)

(3)VHDL程序及注释

DDS顶层设计

LIBRARYIEEE;--DDS顶层设计

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDDS_VHDLIS

PORT(CLK:

INSTD_LOGIC;

sel:

INSTD_LOGIC_VECTOR(1DOWNTO0);

FWORD:

INSTD_LOGIC_VECTOR(7DOWNTO0);--频率控制字

PWORD:

INSTD_LOGIC_VECTOR(7DOWNTO0);--相位控制字

FOUT:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

END;

ARCHITECTUREoneOFDDS_VHDLIS

COMPONENTfenpin

PORT(clk:

INSTD_LOGIC;

clk1:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTREG10B

PORT(LOAD:

INSTD_LOGIC;

DIN:

INSTD_LOGIC_VECTOR(9DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCOMPONENT;

COMPONENTADDER10B

PORT(A:

INSTD_LOGIC_VECTOR(9DOWNTO0);

B:

INSTD_LOGIC_VECTOR(9DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCOMPONENT;

COMPONENTmyrom1

PORT(address:

INSTD_LOGIC_VECTOR(9DOWNTO0);

clock:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCOMPONENT;

COMPONENTfangbo

PORT(clock:

INstd_logic;--复位信号reset,时钟信号clk

address:

instd_logic_vector(9DOWNTO0);

q:

OUTstd_logic_vector(9DOWNTO0));

ENDCOMPONENT;

COMPONENTjuchibo

PORT(clock:

INstd_logic;--复位信号reset,时钟信号clk

address:

instd_logic_vector(9DOWNTO0);

q:

OUTstd_logic_vector(9DOWNTO0));

ENDCOMPONENT;

COMPONENTsanjiaobo

PORT(clock:

INstd_logic;--复位信号reset,时钟信号clk

address:

instd_logic_vector(9DOWNTO0);

q:

OUTstd_logic_vector(9DOWNTO0));

ENDCOMPONENT;

COMPONENTchiose

PORT(c1,c2,c3,c4:

INstd_logic_vector(9DOWNTO0);--复位信号reset,时钟信号clk

cho:

instd_logic_vector(1DOWNTO0);

q:

OUTstd_logic_vector(9DOWNTO0)

);

ENDCOMPONENT;

COMPONENTxuanpin

PORT(clk:

INSTD_LOGIC;

clk1:

OUTSTD_LOGIC;

f1:

inSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDCOMPONENT;

COMPONENTsudu

PORT(clk:

INSTD_LOGIC;

out1:

OUTSTD_LOGIC_VECTOR(9DOWNTO0)

);

ENDCOMPONENT;

SIGNALF10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALD10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALDIN10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALP10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALLIN10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALSIN10B:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALcc1:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALcc2:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALcc3:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALcc4:

STD_LOGIC_VECTOR(9DOWNTO0);

SIGNALclk11:

STD_LOGIC;

SIGNALclk12:

STD_LOGIC;

SIGNALout11:

STD_LOGIC_VECTOR(9DOWNTO0);

BEGIN

F10B(9DOWNTO8)<="00";

F10B(7DOWNTO0)<=FWORD;

P10B(1DOWNTO0)<="00";

P10B(9DOWNTO2)<=PWORD;

u1:

ADDER10BPORTMAP(A=>F10B,B=>D10B,S=>DIN10B);

u2:

REG10BPORTMAP(DOUT=>D10B,DIN=>DIN10B,LOAD=>clk11);

u3:

myrom1PORTMAP(address=>SIN10B,q=>cc1,clock=>clk11);

u4:

ADDER10BPORTMAP(A=>P10B,B=>D10B,S=>LIN10B);

u5:

REG10BPORTMAP(DOUT=>SIN10B,DIN=>LIN10B,LOAD=>clk11);

u6:

sanjiaoboPORTMAP(address=>out11,q=>cc2,clock=>clk11);

u7:

fangboPORTMAP(address=>out11,q=>cc3,clock=>clk11);

u8:

juchiboPORTMAP(address=>out11,q=>cc4,clock=>clk11);

u9:

chiosePORTMAP(c1=>cc1,c2=>cc2,c3=>cc3,c4=>cc4,cho=>sel,q=>FOUT);

u10:

fenpinPORTMAP(clk=>CLK,clk1=>clk11);

u11:

xuanpinPORTMAP(clk=>CLK,clk1=>clk12,f1=>FWORD);

u12:

suduPORTMAP(clk=>clk12,out1=>out11);

END;

*附1.LIBRARYIEEE;--10位加法器模块

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDER10BIS

PORT(A,B:

INSTD_LOGIC_VECTOR(9DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDADDER10B;

ARCHITECTUREbehavOFADDER10BIS

BEGIN

S<=A+B;

ENDbehav;

*附2.LIBRARYIEEE;--10位寄存器模块

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYREG10BIS

PORT(Load:

INSTD_LOGIC;

DIN:

INSTD_LOGIC_VECTOR(9DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDREG10B;

ARCHITECTUREbehavOFREG10BIS

BEGIN

PROCESS(Load,DIN)

BEGIN

IFLoad'EVENTANDLoad='1'THENDOUT<=DIN;ENDIF;

ENDPROCESS;

ENDbehav;

*附3.LIBRARYIEEE;--32位加法器模块

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDER32BIS

PORT(A,B:

INSTD_LOGIC_VECTOR(31DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(31DOWNTO0));

ENDADDER32B;

ARCHITECTUREbehavOFADDER32BIS

BEGIN

S<=A+B;

ENDbehav;

*附4.LIBRARYIEEE;--32位寄存器模块

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYREG32BIS

PORT(Load:

INSTD_LOGIC;

DIN:

INSTD_LOGIC_VECTOR(31DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(31DOWNTO0));

ENDREG32B;

ARCHITECTUREbehavOFREG32BIS

BEGIN

PROCESS(Load,DIN)

BEGIN

IFLoad'EVENTANDLoad='1'THENDOUT<=DIN;ENDIF;

ENDPROCESS;

ENDbehav;

*附5.LIBRARYIEEE;--分频模块

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYfenpinIS

PORT(clk:

INstd_logic;

clk1:

OUTstd_logic);--输出信号q

ENDfenpin;

ARCHITECTUREbOFfenpinIS

BEGIN

PROCESS(clk)

VARIABLEtmp:

std_logic_vector(8DOWNTO0);

VARIABLEa:

std_logic;

BEGIN

ifclk'EVENTANDclk='1'THEN

iftmp=500thentmp:

="000000000";a:

=nota;

elsetmp:

=tmp+1;

endif;

endif;

clk1<=a;

ENDPROCESS;

ENDb;

*附6.LIBRARYIEEE;--选频模块

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYxuanpinIS

PORT(clk:

INSTD_LOGIC;

clk1:

OUTSTD_LOGIC;

f1:

inSTD_LOGIC_VECTOR(7DOWNTO0));

END;

ARCHITECTUREoneOFxuanpinIS

signaltmp:

std_logic_vector(7DOWNTO0);

BEGIN

PROCESS(clk)

VARIABLEclk11:

std_logic;

begin

ifclk'eventandclk='1'then

iftmp="11111111"thentmp<="00000000";

elsetmp<=tmp+1;

iff1="00000001"thenclk11:

=tmp(0);

elsiff1="00000010"thenclk11:

=tmp

(1);

elsiff1="00000100"thenclk11:

=tmp

(2);

elsiff1="00001000"thenclk11:

=tmp(3);

elsiff1="00010000"thenclk11:

=tmp(4);

elsiff1="00100000"thenclk11:

=tmp(5);

elsiff1="01000000"thenclk11:

=tmp(6);

elsiff1="10000000"thenclk11:

=tmp(7);

endif;

endif;

endif;

clk1<=clk11;

endprocess;

endone;

*附7.LIBRARYIEEE;--选择模块

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYchioseIS

PORT(c1,c2,c3,c4:

INstd_logic_vector(9DOWNTO0);--复位信号reset,时钟信号c