计组课设实验报告.docx

《计组课设实验报告.docx》由会员分享,可在线阅读,更多相关《计组课设实验报告.docx(10页珍藏版)》请在冰豆网上搜索。

计组课设实验报告

《计算机组成原理与系统结构》课程设计

实

验

报

告

课题:

两个16位二进制数加法计算

班级:

成员:

完成日期:

2013年10月11日

一:

课程设计步骤

1.确定设计目标

综合考虑实验条件及自身能力水平,以及设计功能的可靠性和实用性,我们小组决定将设计目标定为“两个16位二进制数相加”。

分两次分别输入两个加数的低八位和高八位,输出两个16位二进制数相加的结果。

2.确定指令系统

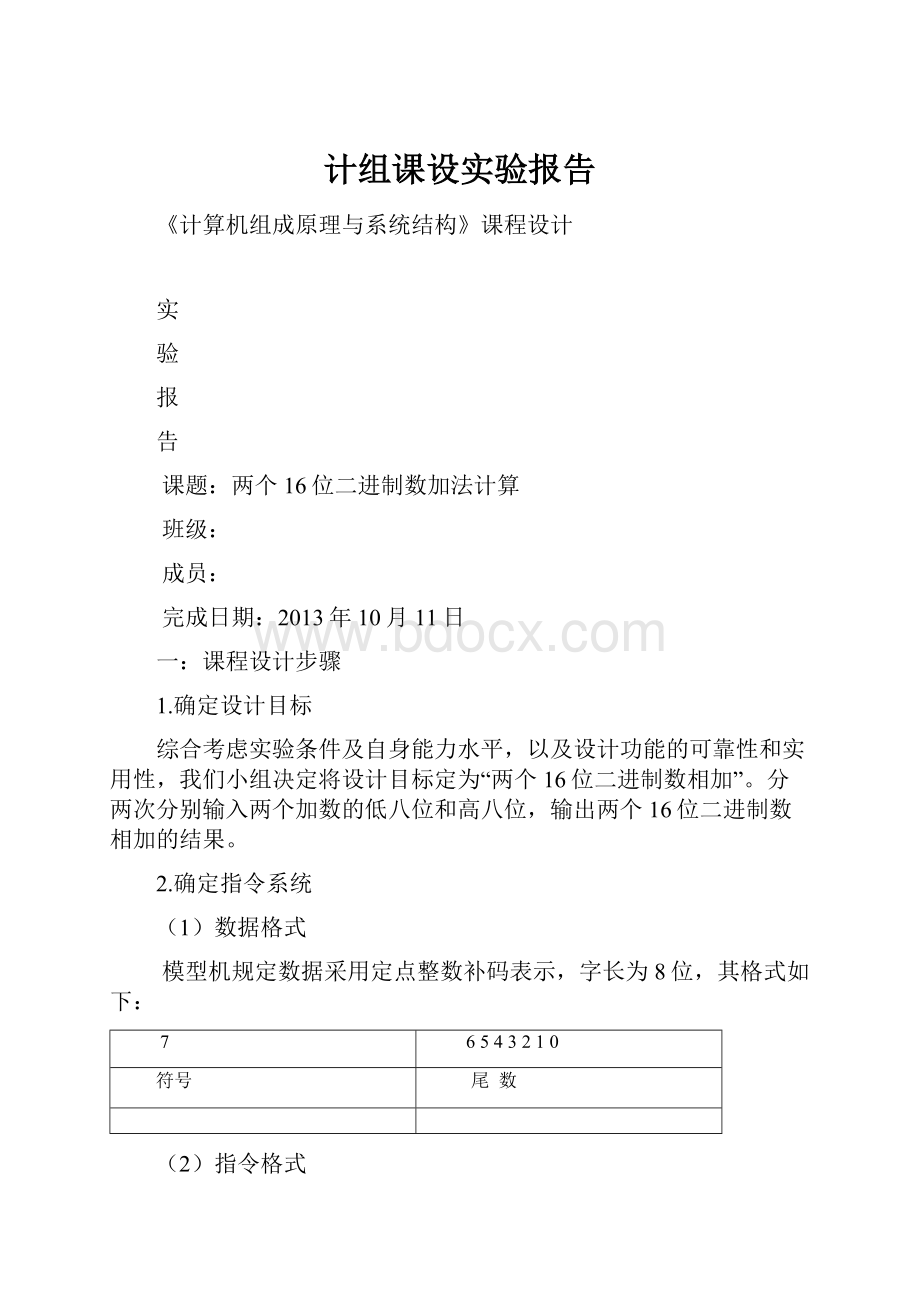

(1)数据格式

模型机规定数据采用定点整数补码表示,字长为8位,其格式如下:

7

6543210

符号

尾数

(2)指令格式

模型机设计四大类指令共16条,其中包括算术逻辑指令、I/O指令、访问及转移指令和停机指令。

算术逻辑指令

设计九条算术逻辑指令并用单字节表示,寻址方式采用寄存器直接寻址,其格式如下:

7654

32

10

OP-CODE

RS

RD

其中,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器,并规定:

RS或RD

选定的寄存器

00

01

10

R0

R1

R2

I/O指令

输入(1N)和输入(OUT)指令采用单字节指令,其格式如下:

7654

32

10

OP-CODE

addr

RD

其中,addr=01时,选中“INPUTDEVICE”中的开关组作为输入设备,addr=10时,选中“INPUTDEVICE”中的数码块作为输入设备。

访问指令及转移指令

模型机设计两条访问指令,即存数(STA)、取数(LDA),两条颛臾指令,即无条件转移(JMP)、结果为零或有进位转移(BZC),指令格式如下:

76

54

32

10

00

M

OP-CODE

RD

D

其中,OP-CODE为操作码,rd为目的寄存器地址(LDA、STA指令使用)。

D为位移量(正负均可),M为寻址模式,其定义如下:

寻址模式

有效地址E

说明

00

01

10

11

E=D

E=(D)

E=(RI)+D

E=(PC)+D

直接寻址

间接寻址

RI变址寻址

相对寻址

本模式机规定变址寄存器RI指定为寄存器R2

停机指令

停机指令格式如下:

7654

32

10

OP-CODE

00

00

HALT指令,用于实现停机操作。

(3)指令系统

在这次模型机设计中,为了实现两个16位二进制数相加的功能,我们一共使用了XOR(新设计指令),ADC,INC,LDA,STA,JMP,BZC,IN,OUT,HALT共10个机器指令,其助记符、功能和具体指令格式如下:

助记符号

指令格式

功能

XORRS,RD

1010

RS

RD

RS⊕RD

ADCRS,RD

1001

RS

RD

RS+RD+CY->RD

INCRD

1011

RS

RD+1->RD

LDAM,D,RD

00

M

00

RD

E->RS

D

STAM,D,RD

00

M

01

RD

RD->E

D

JMPM,D

00

M

10

00

E->PC

D

BZCM,D

00

M

11

00

当CY=1或Z=1;E->PC

D

INADDR,RD

0100

01

RD

ADDR->RD

OUTADDR,RD

0101

10

RD

RD->ADDR

HALT

0110

00

00

停机

3.总体结构和数据通路:

总体结构和数据通路图请参见附录1。

4.微程序流程图:

微程序流程图请参见附录2。

5.机器码及微程序:

机器码及微程序请参见附录3。

二.课程设计总结

这门课程是一门对综合能力和基础知识要求非常高的课程。

成功完成实验内容,需要熟悉《汇编语言》,《计算机组成原理》,《离散数学》和《数字逻辑》各门课程的基础知识,并且要加以拓展和熟练运用,这对我们整个小组来说是一个不小的挑战。

实验刚刚开始的阶段,我们参考了高年级同学的实验报告和设计过程,起初觉得束手无策,很多内容都不知道其中的含义和思考及设计的过程。

不过从第一节课开始,陈老师指导我们一步步地完成整个设计过程,每节课对应设计中的一个步骤,化整为零,个个击破,实验进行的过程中,随着进度的加深,我们的信心也越来越饱满,渐渐看到了整体的思路和方向。

出现问题时,我们首先进行小组讨论,小组讨论无法解决的问题,我们选择向更有经验和基础知识更加牢固的同学请教,再无法解决时,便向老师求助,陈老师在整个实验过程中提供了非常大的帮助。

整个实验过程中,除了对设计步骤和各种图表工具的陌生带来的困难以外,最大的困难来自于实验硬件条件给出的限制。

对于只有三个寄存器的实验电路箱来说,分别进行高八位,低八位的输入,相加和输出就已经是个挑战,而更大的挑战在于,怎样储存和取出进位数字。

我们知道,如果产生了进位,那么进位的数字将存储在CF专用寄存器中,但是CF寄存器内保存的数据十分的“脆弱”,稍有不慎,除了加法计算之外,其他的很多操作,只要是经过ALU加法器原件的操作,都有可能改变其中存储的数据。

一度让我们觉得无从下手,甚至怀疑自己一开始设计的目标功能就是错误的,根本无法实现的。

但是后来,我们想到了利用主存来存储进位的想法,翻看教材和上网查阅各种资料之后,我们失望得发现,CF寄存器是一个特殊的专用寄存器,无法向其他寄存器一样将数据随意存取,只会在进行带进位加(ADC)时,才会被带入到存储计算结果的寄存器中。

这给了我们一个启发,我们想到了先将一个寄存器清零(使用我们新设计的XOR指令),然后用这个寄存器自身和自身带进位加的方式将进位数字取出,然后将该寄存器的数据传入到主存中,通过这一特殊的方式,就实现了“将CF寄存器中的数据放入主存”这一原来看似不可能完成的任务。

解决这个问题的过程中,我们充分体会到了团队协作和创新思维的重要性,明白了一个看似困难重重几乎不可能完成的任务,只要勤于思考善于动手,也能通过自己的努力去实现。

我们觉得这一体会是本次试验过程中,除了知识之外最大的收获。

三.小组成员各自的任务和完成情况

张三:

小组核心成员和组长,拥有扎实的计算机组成原理和汇编语言基础,负责确定设计目标,核心程序的编写以及微程序、机器指令的转化,完成实验的理论基础框架。

出色地完成了程序设计的任务,为最终的上机实践提供了保障。

李四:

协调整个团队的合作,在遇到困难时查阅书籍和网上资料,对新的理论知识和操作技术进行吸收和消化,整理记录实验中各项设计笔记,完成实验报告的整合和撰写。

王五:

心思细致缜密,动手能力强,实践经验丰富,负责实验箱的检验,调试和接线部分。

四.实验中的不足

最后一节课进行最终的上机实践检验时,我们遇到了意料之外的问题和困难。

在前一节课中,我们利用已有的程序对试验箱进行了检验和调试,最终确定试验箱可以正常工作。

但是在最后一节课中,首先,我们没有拿到上一节课已经经过检验确定可以正常工作的实验箱,这时我们心中已经有了一丝隐忧,担心因为实验箱存在问题而导致实验无法正常进行,而在有限的时间内,对复杂的实验箱接线全部推倒重来,又是时间不允许的做法。

我们抱着试一试的心态将实验箱与计算机连接,使用已有的程序进行检验,所幸实验箱运行正常。

接着我们满怀希望地载入了自己编写的微程序和机器指令,但是运行之后出现了问题,第一步输入就无法正常工作,虽然INPUT原件中的数据正常显示为我们输入的数据,但是R0和R1寄存器中的数据始终不发生任何变化,我们想到了两个原因:

一是硬件问题,可能是实验箱的接线出现问题或者实验箱与计算机的连接出现问题;二是我们自己设计的程序存在问题。

但是当我们尝试第二次的时候,更奇怪的现象出现了:

载入程序之后,进行运行时,第一次点击单步执行之后,计算机中的“CMPP”程序就出现了无响应卡死的情况。

我们关闭程序和实验箱,重新进行连接和载入之后,再次尝试还是同样的情况。

第三次,我们重启了计算机,再次重复上一次的步骤,并且加入了检查载入程序是否出错这一步骤,但是还是无法正常运行。

反复尝试多次之后,结果还是和以前一样,要么是寄存器数据不发生变化,要么是“CMPP”程序卡死无响应。

进行到这里,我们怀疑是实验箱或者计算机存在问题。

由于反复尝试连接和载入运行耗费了大量的时间,我们决定更换实验设备再进行尝试。

我们使用了后面一排无人使用和管理的实验箱,并且打开了旁边的另外两台电脑,此时我们一共有两台实验箱和三台电脑可以使用了。

我们不停更换实验箱和电脑,三台电脑两台实验箱,一共六种组合方式,我们每种组合都尝试过不下三次,进行了近20次的实验之后,得到了以下几种结果:

1.机箱和计算机无法连接,显示“通讯串口发生错误”;

2.机箱和计算机可以成功连接,但是运行“CMPP”程序是频繁出现卡死无响应的情况;

3.机箱和计算机可以成功连接,“CMPP”程序可以打开运行,但是载入程序之后第一次单步执行便死机,无法继续下面的执行步骤;

4.机箱和计算机可以成功连接,“CMPP”程序可以打开运行,载入程序之后可以正常进行单步执行,但是寄存器中的数据不发生变化,第一步输入就无法正常运行;

5.机箱计算机可以成功连接,“CMPP”程序打开,载入和运行一切正常,输入的数据成功送入寄存器R0和R1,但是进行某些步骤时,“CMPP”程序出现卡死无响应,在程序正常运行到一半时,不得不被迫中断退出。

我们小组对出现的以上五种情况进行了分析,其中出现过数据可以正常输入的情况,说明程序本身在输入方面不会存在问题,但是这种可以正常输入的情况之出现了一次,之后便再也没有出现过,中断了我们继续检验后续步骤的操作。

就在这种不断尝试不断受挫的过程中,下课时间到了,我们遗憾地放弃了实验。

我们认为最大的可能性是机箱和计算机存在不同程度的偶然性问题,所以才会出现如此多种不一样的状况,而当这些偶然性问题某一次运气很好,都没有出现,或者出现的数目最少的时候,我们成功进行了输入,但就在此时,新的问题又再一次出现,让我们失去了继续验证下去的机会。

虽然我们对实验没有成功进行的主要原因归咎于硬件设备的问题,但是我们也没有彻底排除理论设计时就可能存在某些未发现的错误。

但是用纸笔对理论设计进行各种分析讨论之后也没有找到问题出在什么地方,由于时间和条件的限制,我们的实验最后没有圆满完成,也没有查出真正的问题所在,这是本次实验中一个不完美的地方。

我们小组对实验器材可能存在的问题表示遗憾,但是也愿意承认我们的理论设计有潜在的出错隐患,对于实验没有完美结束也愿意承担一定的责任,还希望老师能够谅解我们的不足之处。

附录:

附录1:

总体结构和数据通路图

附录2:

微程序流程图

附录3:

机器码及微程序:

程序

标注

助记符

$P0046

IN01,R2(FE)

$P0106

STA[FF],R2

$P02FF

$P0344

L2:

IN01,R0

$P0445

IN01,R1

$P05AA

XORR2,R2

$P0694

ADCR1,R0

$P079A

ADCR2,R2

$P0801

LDA[FF],R1

$P09FF

$P0AB1

INCR1

$P0B0C

BZCL2

$P0C14

$P0D06

STA[FC],R2

$P0EFC

$P0F05

STA[FF],R1

$P10FF

$P1158

OUTR0

$P1208

JMPL1

$P1303

$P1401

L2:

LDA[FC],R1

$P15FC

$P1694

ADCR1,R0

$P1758

OUTR0

$P1860

HALT

微程序:

(新设计指令部分)

$M0100ED82

$M0200C05A

$M1A00222C

$M2C00262D

$M2D681B41