EDA状态机实验报告.docx

《EDA状态机实验报告.docx》由会员分享,可在线阅读,更多相关《EDA状态机实验报告.docx(7页珍藏版)》请在冰豆网上搜索。

EDA状态机实验报告

状态机设计

学院:

数学与计算机学院

专业:

姓名:

学号:

一、实验目的

1.通过实验掌握有限状态机的要点和特点及其设计;

2.用状态机实现串行序列的设计。

二、设计要求

1.先设计0111010011011010序列信号发生器;

2.再设计一个序列信号检测器,若系统检测到串行序列11010则输出为“1”,否则输出为“0”,并对其进行仿真和硬件测试。

三、实验设备

PC机,Quartueⅱ软件,实验箱

四、实验原理

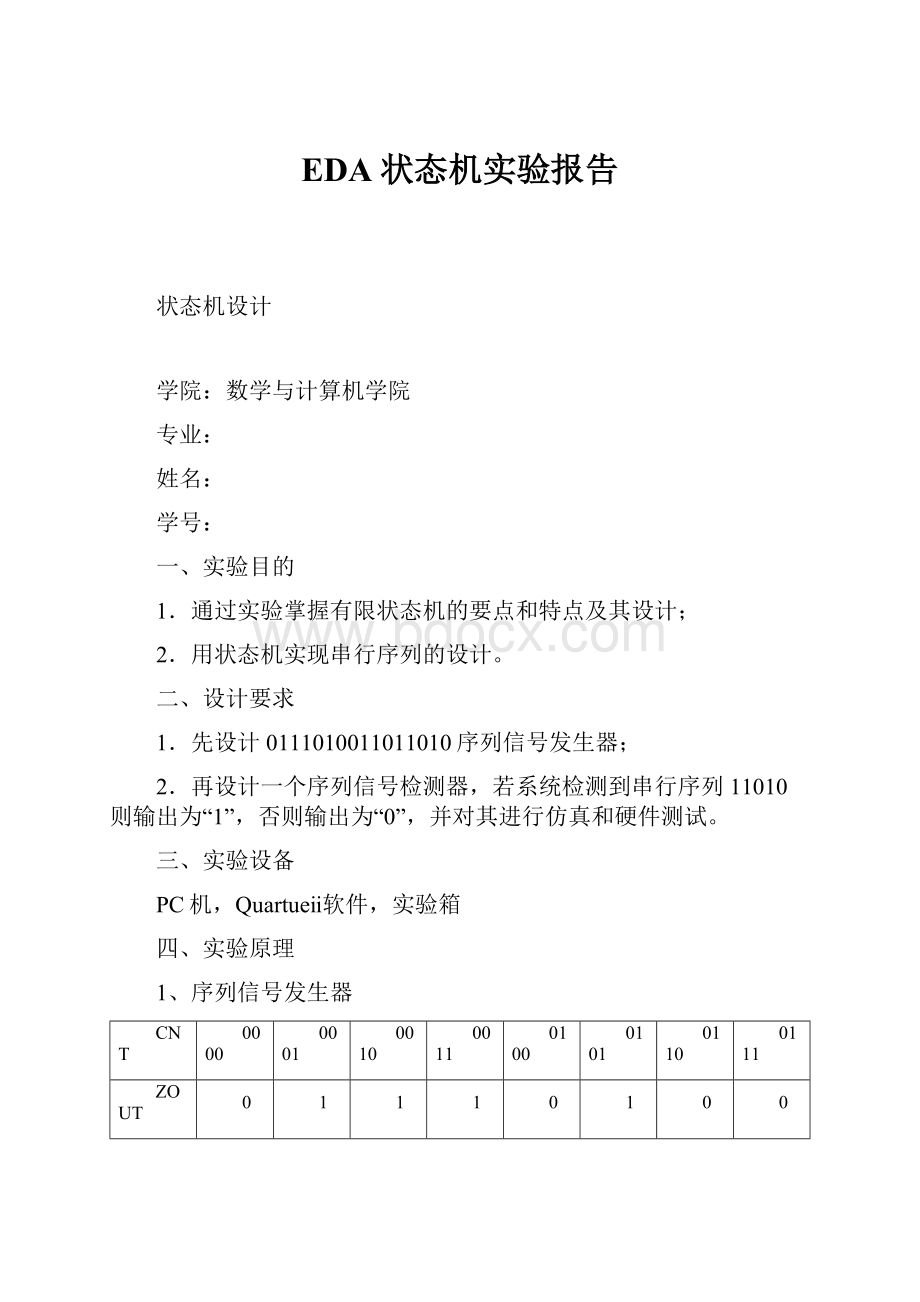

1、序列信号发生器

CNT

0000

0001

0010

0011

0100

0101

0110

0111

ZOUT

0

1

1

1

0

1

0

0

CNT

1000

1001

1010

1011

1100

1101

1110

1111

ZOUT

1

1

0

1

1

0

1

0

复位信号CLRN。

当CLRN=0时,使CNT=0000,当CLRN=1时,不影响程序运行,每来一个CLK脉冲CNT加一。

2、序列信号检测器

状态转移图:

五、实验步骤

1、信号发生器

(1)建立工作库文件夹,输入设计项目VHDL代码,如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYs_machineIS

PORT(clk,reset,state_input:

INSTD_LOGIC;

comb_output:

OUTSTD_LOGIC);

ENDs_machine;

ARCHITECTUREbehavOFs_machineIS

TYPEFSM_STIS(s0,s1,s2,s3);

SIGNALcurrent_state,next_state:

FSM_ST;

BEGIN

REG:

PROCESS(reset,clk)

BEGIN

IFreset='1'THENcurrent_state<=s0;

ELSIFCLK'EVENTANDCLK='1'THEN

current_state<=next_statE;

ENDIF;

ENDPROCESS;

COM:

PROCESS(current_state,next_state)

BEGIN

CASEcurrent_stateIS

WHENs0=>comb_output<='0';

IFstate_input='0'THENnext_state<=s0;

ELSEnext_state<=s1;

ENDIF;

WHENs1=>comb_output<='0';

IFstate_input='0'THENnext_state<=s0;

ELSEnext_state<=s2;

ENDIF;

WHENs2=>comb_output<='0';

IFstate_input='0'THENnext_state<=s0;

ELSEnext_state<=s3;

ENDIF;

WHENs3=>comb_output<='1';

IFstate_input='0'THENnext_state<=s0;

ELSEnext_state<=s3;

ENDIF;

ENDcase;

ENDPROCESS;

ENDbehav;

(2)对其进行波形仿真,如下图:

3)将其转换成可调用元件如图:

2、信号检测器

1)建立工作库文件夹,输入设计项目VHDL代码,如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYSCHKIS

PORT(DIN,CLK,CLR :

INSTD_LOGIC;

ss:

OUTSTD_LOGIC_VECTOR

ENDSCHK;

ARCHITECTUREbehavOFSCHKIS

SIGNALQ:

INTEGERRANGE0TO5;

SIGNALD:

STD_LOGIC_VECTOR(5DOWNTO0);

BEGIN

D<="11010" ;

PROCESS(CLK,CLR)

BEGIN

IFCLR='1'THEN Q<=0;

ELSIF CLK'EVENTANDCLK='1'THEN

CASEQIS

WHEN0=> IFDIN=D(4)THENQ<=1;ELSEQ<=0;ENDIF;

WHEN1=> IFDIN=D(3)THENQ<=2;ELSEQ<=0;ENDIF;

WHEN2=> IFDIN=D

(2)THENQ<=3;ELSEQ<=2;ENDIF;

WHEN3=> IFDIN=D

(1)THENQ<=4;ELSEQ<=0;ENDIF;

WHEN4=> IFDIN=D(0)THENQ<=5;ELSEQ<=2;ENDIF;

WHENOTHERS=> Q<=0;

ENDCASE;

ENDIF;

ENDPROCESS;

PROCESS(Q)

BEGIN

IFQ=5 THEN ss<="1";

ELSE ss<="0";

ENDIF;

ENDPROCESS;

ENDbehav;

3)将其转换成可调用元件如图:

3.序列信号检测器顶层文件

1)调用序列信号发生器和序列信号检测器元件,建立工作库文件夹,输入设计项目原理图如下图:

2)对总体进行波形仿真,如下图:

功能仿真:

六、实验心得

本实验中使用moore型状态机效果更好一些。

在实际应用中,mealy型和moore型状态机各有所长,应根据实际合理选择。