EP3C40Q240C8N引脚原理图.docx

《EP3C40Q240C8N引脚原理图.docx》由会员分享,可在线阅读,更多相关《EP3C40Q240C8N引脚原理图.docx(14页珍藏版)》请在冰豆网上搜索。

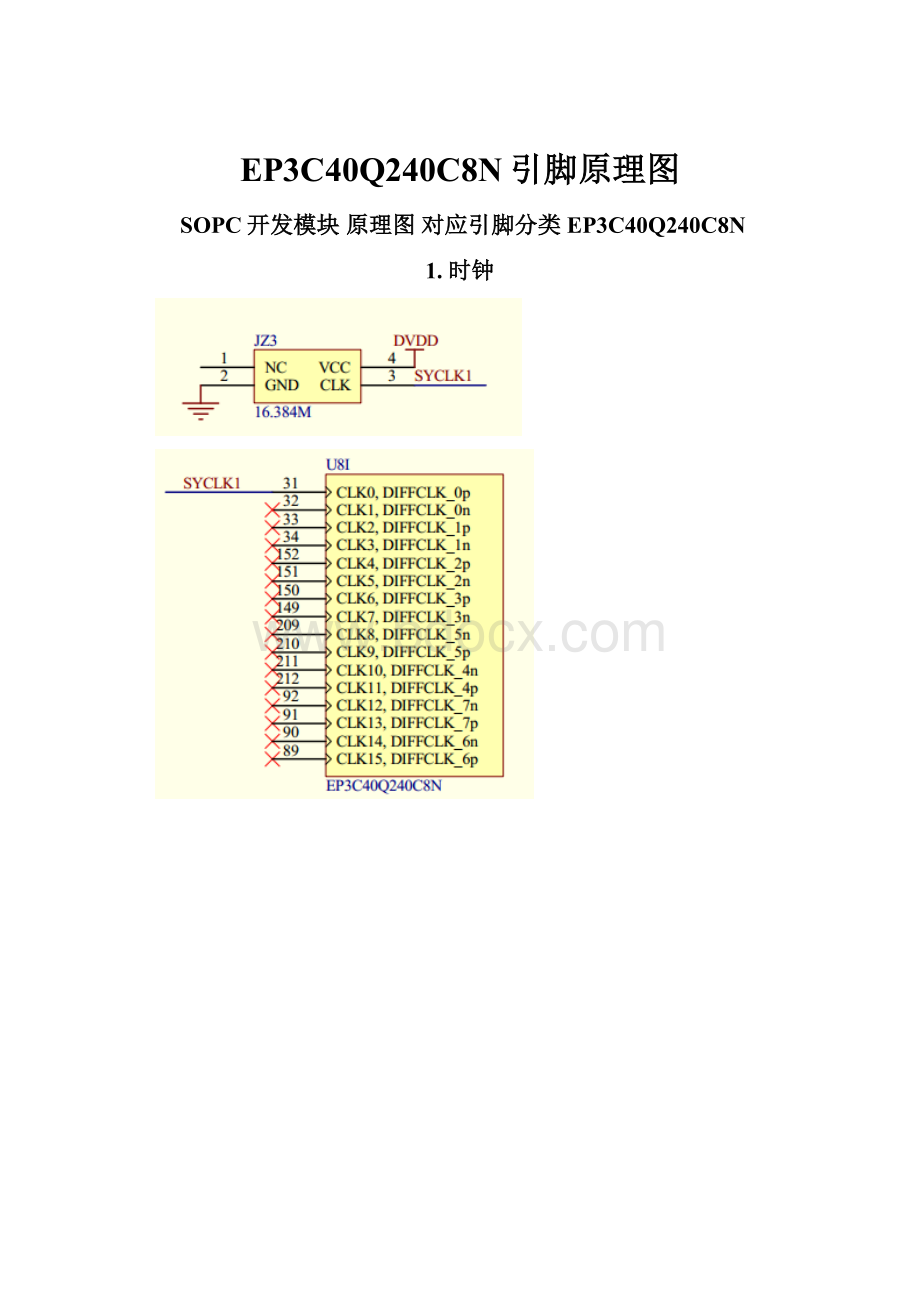

EP3C40Q240C8N引脚原理图

SOPC开发模块原理图对应引脚分类EP3C40Q240C8N

1.时钟

2.LED和按键

3.port——外接试验箱端口

4.SAA7113H

SAA7113是一种视频解码芯片,它可以输入4路模拟视频信号,通过内部寄存器的不同配置可以对4路输入进行转换,输入可以为4路CVBS或2路S视频(Y/C)信号,输出8位“VPO”总线,为标准的ITU656、YUV4:

2:

2格式。

7113兼容PAL、NTSC、SECAM多种制式,可以自动检测场频适用的50或60Hz,可以在PAL、NTSC之间自动切换。

7113内部具有一系列寄存器,可以配置为不同的参数,对色度、亮度等的控制都是通过对相应寄存器改写不同的值,寄存器的读写需要通过I2C总线进行。

7113的模拟与数字部分均采用+3.3V供电,数字I/O接口可兼容+5V,正常工作时功耗0.4W,空闲时为0.07W。

7113需外接24.576MHz晶体,内部具有锁相环(LLC),可输出27MHz的系统时钟。

芯片具有上电自动复位功能,另有外部复位管脚(CE),低电平复位,复位以后输出总线变为三态,待复位信号变高后自动恢复,时钟丢失、电源电压降低都会引起芯片的自动复位。

7113为QFP44封装。

5.ADV7123——视频数模转换器

ADV7123(ADV®)是一款单芯片、三通道、高速数模转换器,内置三个高速、10位、带互补输出的视频数模转换器、一个标准TTL输入接口以及一个高阻抗、模拟输出电流源。

6.CH372——总线通用接口芯片

7.Wm8731-编码解码器

8.XPT2046——触摸屏控制器

9.EPCS16-闪存

10.FPGA所有bank引脚:

(注:

专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)