标准实验报告二 脉冲成型实验.docx

《标准实验报告二 脉冲成型实验.docx》由会员分享,可在线阅读,更多相关《标准实验报告二 脉冲成型实验.docx(16页珍藏版)》请在冰豆网上搜索。

标准实验报告二脉冲成型实验

电子科技大学

实验报告

学生姓名:

学号:

指导教师:

一、实验室名称:

通信信号处理及传输实验室

二、实验项目名称:

脉冲成型实验

三、实验原理:

1、脉冲成型的理论基础

在现代无线通信中,由于基带信号的频谱范围都比较宽,为了有效利用信道,在信号传输之前,都要对信号进行频谱压缩,使其在消除码间干扰和达到最佳检测的前提下,大大提高频带的利用率。

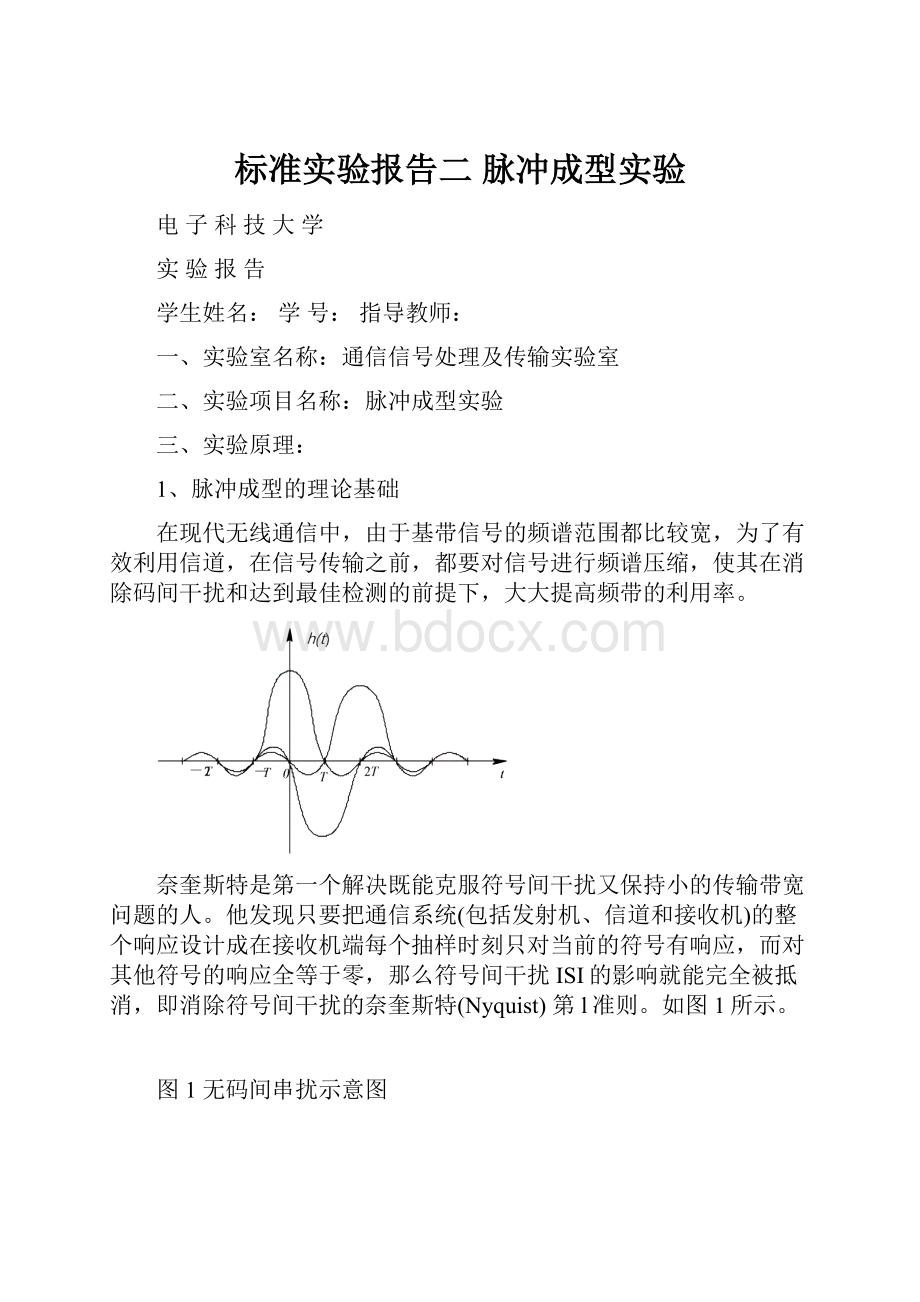

奈奎斯特是第一个解决既能克服符号间干扰又保持小的传输带宽问题的人。

他发现只要把通信系统(包括发射机、信道和接收机)的整个响应设计成在接收机端每个抽样时刻只对当前的符号有响应,而对其他符号的响应全等于零,那么符号间干扰ISI的影响就能完全被抵消,即消除符号间干扰的奈奎斯特(Nyquist)第l准则。

如图1所示。

图1无码间串扰示意图

在理论上,Nyquist第l准则成功地解决了成形滤波器的设计问题,但是它只给出了一个抽象的理论准则,而对于如何具体设计成形滤波器并没有一个明确的答案。

由于数字技术的发展,基带信号的频谱成形可通过数字方法进行。

利用数字式处理来实现频谱波形成形滤波的情况越来越广泛。

数字滤波具有精度高、可靠性高、灵活性强、便于大规模集成、可以得到很高的性能指标等优点,可实现有限冲激响应(FlR)滤波器或无限冲激响应滤波(IIR)滤波器。

FIR滤波器可做到严格的线性相位,设计方法既有从时域出发考虑的加窗法,从频域出发考虑的频率采样法、等波纹最佳一致逼近法,也有综合考虑频域和时域要求的最优化设计方法(线性规划法)。

在实际应用中,升余弦滤波器是运用较为广泛的成形滤波器,因为它有如下的优点:

1)满足Nyquist第1准则;

2)可以消除理想低通滤波器设计上的困难,有一平滑的过渡带;

3)通过引入滚降系数改变传输信号的成形波形,可以减小抽样定时脉冲误差所带来的影响,即降低码间干扰。

升余弦滤波器的传递函数为:

,

其中,

是滚降因子,取值范围0到1。

当

时,升余弦滚降滤波器对应于具有最小带宽的矩形滤波器。

这种滤波器的冲激响应可由对其传递函数做傅里叶变换得到:

。

图2是升余弦滤波器的频域传递函数及时域冲激响应,其中(a)是频域传递函数

,(b)是时域冲激响应

。

图2升余弦滤波器的频域传递函数及时域冲激响应

升余弦滚降传递函数可以通过在发射机端和接收机端使用同样的滤波器来实现,同时在平坦衰落信道中为实现最佳性能提供了匹配滤波。

为实现滤波器的响应,脉冲成形滤波器可以用在基带数据上,也可以使用在发射机的输出端。

图3就是将输入随机序列{+1,-1}通过0.5升余弦滤波器后的脉冲成型波形。

图3滚降系数0.5的升余弦脉冲成型波形

不使用奈奎斯特技术来实现脉冲成形是有可能的,其中一项就是MSK调制方式的应用,与OQPSK调制方式结合的效率较高的半正弦脉冲调制。

通过截短的传递函数来抑制相邻符号间的干扰。

由于使用更短的截短传递函数,半正弦脉冲成形后的信号频谱相对升余弦滚降成形的信号频谱来说,主瓣较宽,旁瓣较高,频谱效率较低。

2、VHDL实现脉冲成型

在程序中,我们首先产生升余弦滤波器系数,再将输入数据滤波输出,即可得到我们期望的滚将系数(0.5或0.8)的升余弦信号成型波形。

因此,这里重点就是如何生成各种滚降系数的升余弦滤波器系数。

(1)利用MATLAB生成升余弦滚降滤波器系数

在MATLAB中,可以利用函数rcosine得到升余弦滤波器系数,格式如下:

[NUM,DEN]=RCOSINE(Fd,Fs,TYPE_FLAG,R,DELAY)

其中,Fd表示数字信号频率;Fs表示滤波器采样频率,且Fs/Fd必须是一个正整数。

TYPE_FLAG表示设计的滤波器的类型,可以是'iir'、'sqrt'、或者它们的组合'iir/sqrt',也可以是常规类型'normal'。

R表示滚降系数,取值范围是[0,1].。

DELAY表示滤波器延迟,必须为一个正整数,DELAY/Fd可以得到以秒为单位的滤波器延迟。

我们以产生0.8滚降系数的升余弦滤波器为例,Fd=1;Fs=8;TYPE_FLAG取“fir”,即可得到49个滤波器系数:

-0.0000-0.0012-0.0036-0.0064-0.0085-0.0088-0.0068-0.00320.0000-0.0000-0.0058-0.0185-0.0361-0.0530-0.0600-0.04600.00000.08520.21080.36960.54650.72020.86710.96541.00000.96540.86710.72020.54650.36960.21080.08520.0000-0.0460-0.0600-0.0530-0.0361-0.0185-0.0058-0.00000.0000-0.0032-0.0068-0.0088-0.0085-0.0064-0.0036-0.0012-0.0000

(2)将升余弦滤波器系数转换为VHDL数组

取滤波器对应的单位冲激响应正负两个第二零点之间的33个样本(9~41,包括左右两个0),然后进行幅值放大(如这里调整为原始系数*100)并取为整数,最后再转换为二进制数,就得到一个包含33个10bit的向量的数组,由此来近似FIR形式的升余弦滚降滤波器。

constantrcosine_eighty:

ps_array(32downto0):

=

(

"0000000000",

"1111111111",

"1111111111",

"1111111110",

"1111111100",

"1111111010",

"1111111001",

"1111111011",

"0000000000",

"0000001000",

"0000010101",

"0000100100",

"0000110110",

"0001001000",

"0001010110",

"0001100000",

"0001100100",

"0001100000",

"0001010110",

"0001001000",

"0000110110",

"0000100100",

"0000010101",

"0000001000",

"0000000000",

"1111111011",

"1111111001",

"1111111010",

"1111111100",

"1111111110",

"1111111111",

"1111111111",

"0000000000");

注:

这里的二进制数为补码表示。

(3)将信号滤波输出,即得到脉冲成型信号

脉冲成形的过程,其实就是输入数据din和升余弦滚将滤波器的时域响应进行卷积的过程。

在源代码中,合法的输入din(长度为2bit)一共有三种:

00、01、11,分别对应的是0、-1和+1。

对于每一次的输入din,在经过和滤波器系数filter_coef(长度为10bit)卷积后,都会得到一个对应的输出filter_dout(长度为10bit)。

利用卷积等效于错位相乘再累加的原理,我们对于每一次的输入,都调用函数signed_mul来得到din和滤波器系数(ps_array)分别相乘的结果,分别存储在33个变量r0,r1,r2,r3,r4,r5,r6,r7,r8,r9,ra,rb,rc,rd,re,rf,r10,r11,r12,r13,r14,r15,r16,r17,r18,r19,r1a,r1b,r1c,r1d,r1e,r1f,r20中,为接下来将要进行的累加操作做好准备。

设置33个中间变量:

h0,h1,h2,h3,h4,h5,h6,h7,h8,h9,ha,hb,hc,hd,he,hf,h10,h11,h12,h13,h14,h15,h16,h17,h18,h19,h1a,h1b,h1c,h1d,h1e,h1f,h20,进行赋值相叠累加:

h0<=r0;

h1<=h0+r1;

h2<=h1+r2;

h3<=h2+r3;

……

h1f<=h1e+r1f;

h20<=h1f+r20;

累加结果存储在h20中,并将其输出到filter_dout,就得到din对应通过滤波器后的结果。

四、实验目的:

1.理解脉冲成形工作原理,加深对奈奎斯特准则的理解。

2.研究几种常用脉冲成形(半正弦、滚降系数0.5和0.8的升余弦滚降)中的信号波形与频谱,了解基带信号的连续发送波形。

3.学会观察信号频谱,分析不同脉冲成形滤波后发送信号的频谱效率。

4.能够基于ISE编写并调试FPGA脉冲成型程序。

五、实验内容:

(1)脉冲成型基础验证实验;观察不同滚降系数的脉冲成型信号的时域波形及频谱;

(2)基于FPGA完成滚降系数

的升余弦滤波器对BPSK信号进行基带调制。

六、实验器材(设备、元器件):

计算机、软件无线电实验箱、信号发生器、示波器、FPGA仿真器、+5V电源

七、实验步骤及实验数据结果分析:

1.脉冲成型基础实验

通过实验平台的菜单窗口提示,利用键盘选择菜单内容,逐级进入该实验操作界面,根据操作步骤的提示,利用示波器在指定接口进行输出信号波形观察。

具体步骤如下:

检查实验平台左上方和右下方的PowerSwitch是否处于关闭(OFF)状态;

检查实验平台的电源线是否连接正确,若连接正确,实验平台右下方的PowerReady指示灯会亮起;

将实验平台左上方的PowerSwitch置为开启(ON)状态,实验系统进入启动状态,观察实验平台中部的显示屏直至进入“高级软件无线电教学系统”;

按下“确认(回车)”键进入系统实验列表;

选择“1”按Enter键,屏幕显示“进入实验中,请稍候”提示框,直至进入基础实验列表;

选择“1”进入脉冲成形实验列表;

在选择具体实验的项目之后按“确认(回车)”,进入脉冲成形仿真实验窗口;

(1)半正弦脉冲成形

选择“1”进入半正弦脉冲成形仿真实验窗,按照软件无线电实验平台界面的提示进行后续操作,将示波器分别观测实验平台TXI和TXQ端口,通过示波器观察输出波形和频谱。

半正弦脉冲成形时域波形

根据示波器上产生波形的频谱图,观察并记录该发送波形的频谱特征:

主瓣过零点带宽(dB)

主瓣与第一旁瓣增益差(dB)

第一旁瓣带宽(dB)

1500KHz

25dB

1000KHz

(2)滚降系数

的升余弦滚降

选择“2”进入滚降系数

的升余弦滚降脉冲成形仿真实验窗,按照软件无线电实验平台界面的提示进行后续操作,将示波器分别观测实验平台TXI和TXQ端口,通过示波器观察输出波形和频谱。

滚降系数

的升余弦滚降时域波形

根据示波器上产生波形的频谱图,观察并记录该发送波形的频谱特征:

主瓣过零点带宽(dB)

主瓣与第一旁瓣增益差(dB)

第一旁瓣带宽(dB)

750KHz

36dB

600KHz

(3)滚降系数

的升余弦滚降

选择“3”进入滚降系数

的升余弦滚降脉冲成形仿真实验窗,按照软件无线电实验平台界面的提示进行后续操作,将示波器分别观测实验平台TXI和TXQ端口,通过示波器观察输出波形和频谱。

滚降系数

的升余弦滚降时域波形

滚降系数

的升余弦滚降波形频谱

根据示波器上产生波形的频谱图,观察并记录该发送波形的频谱特征:

主瓣过零点带宽(dB)

主瓣与第一旁瓣增益差(dB)

第一旁瓣带宽(dB)

900KHz

40dB

500KHz

2.脉冲成型扩展实验

扩展实验主要完成滚降系数

的升余弦滤波器对BPSK信号进行基带调制。

A、从系统平台界面程序进入―》扩展实验-》FPGA扩展实验-》基带信号调制实验;

B、在ISE中打开FPGA_modulate工程,在modula_main.vhd中,确定

Constantmodulation_sel:

std_logic_vector(3downto0):

=“0100”;

C、编译pulse_shaping工程,原程序中包含基于滚降系数0.8的脉冲成型,完成后将bit文件下载到FPGA中。

D、在ARM界面中输入要被调制的数据,然后按“确认”键,在示波器上观察输出时域波形及其频谱。

(由于是BPSK调制,我们只关心TXI路的信号)

输入“456”经BPSK调制后得到下面的波形:

原程序中滚降系数为0.8的时域波形

原程序中滚降系数为0.8的频谱图

E、打开pulse_shaping_filter.vhd文件,基于VHDL补充完成滚降系数

的升余弦滤波器,实现BPSK信号的基带调制;

其中,将滚降系数

的升余弦滤波器系数转换为10-bit的二进制数组为:

constantrcosine_25:

ps_array(32downto0):

=

(

"1111111111",

"1111111010",

"1111110101",

"1111110000",

"1111101101",

"1111101100",

"1111101111",

"1111110101",

"0000000000",

"0000001101",

"0000011101",

"0000101101",

"0000111110",

"0001001101",

"0001011001",

"0001100001",

"0001100100",

"0001100001",

"0001011001",

"0001001101",

"0000111110",

"0000101101",

"0000011101",

"0000001101",

"0000000000",

"1111110101",

"1111101111",

"1111101100",

"1111101101",

"1111110000",

"1111110101",

"1111111010",

"1111111111");

F、再次编译FPGA_modulate工程,完成后将bit文件下载到FPGA中。

G、再次在ARM界面中输入要被调制的数据,然后按“确认”键,在示波器上观察输出波形。

(由于是BPSK调制,我们只关心TXI路的信号)

输入“456”经BPSK调制后得到下面的波形:

滚降系数为0.25的时域波形

滚降系数为0.25的频谱图

八、实验结论:

脉冲成型是通信中消除码间干扰的有效方法。

升余弦滤波器满足Nyquist第1准则,是应用最为广泛的一类成型滤波器。

通过引入滚降系数改变传输信号的成形波形,可以减小抽样定时脉冲误差所带来的影响,即降低码间干扰。

九、思考题

不同滚降系数的升余弦滤波器对系统的影响。

答:

滚降系数越大,成型后的脉冲波形的频谱过渡带越大,频谱越被展宽。

十、总结及心得体会:

通过本次实验理解了升余弦滤波器成型的原理,理解了滚降系数对脉冲成型波形的影响。

同时也学习了基于FPGA的脉冲成型的设计思路和方法。

十一、对本实验过程及方法、手段的改进建议:

报告评分:

指导教师签字: