MATLAB设计FPGA实现联合ISE和Modelsim仿真的FIR滤波器设计.doc

《MATLAB设计FPGA实现联合ISE和Modelsim仿真的FIR滤波器设计.doc》由会员分享,可在线阅读,更多相关《MATLAB设计FPGA实现联合ISE和Modelsim仿真的FIR滤波器设计.doc(22页珍藏版)》请在冰豆网上搜索。

QQ:

290632690肤浅。

。

。

制作

MATLAB设计,FPGA实现,联合ISE和Modelsim仿真的FIR滤波器设计

摘要:

本文首先利用MATLAB产生两个频率不一样的正弦信号,并将这两个正弦信号相加,得到一个混叠的波形;然后利用MATLAB设计一个FIR低通滤波器,并由Verilog实现,联合ISE和Modelsim仿真,实现滤除频率较高的信号,并将滤波后的数据送到MATLAB中分析。

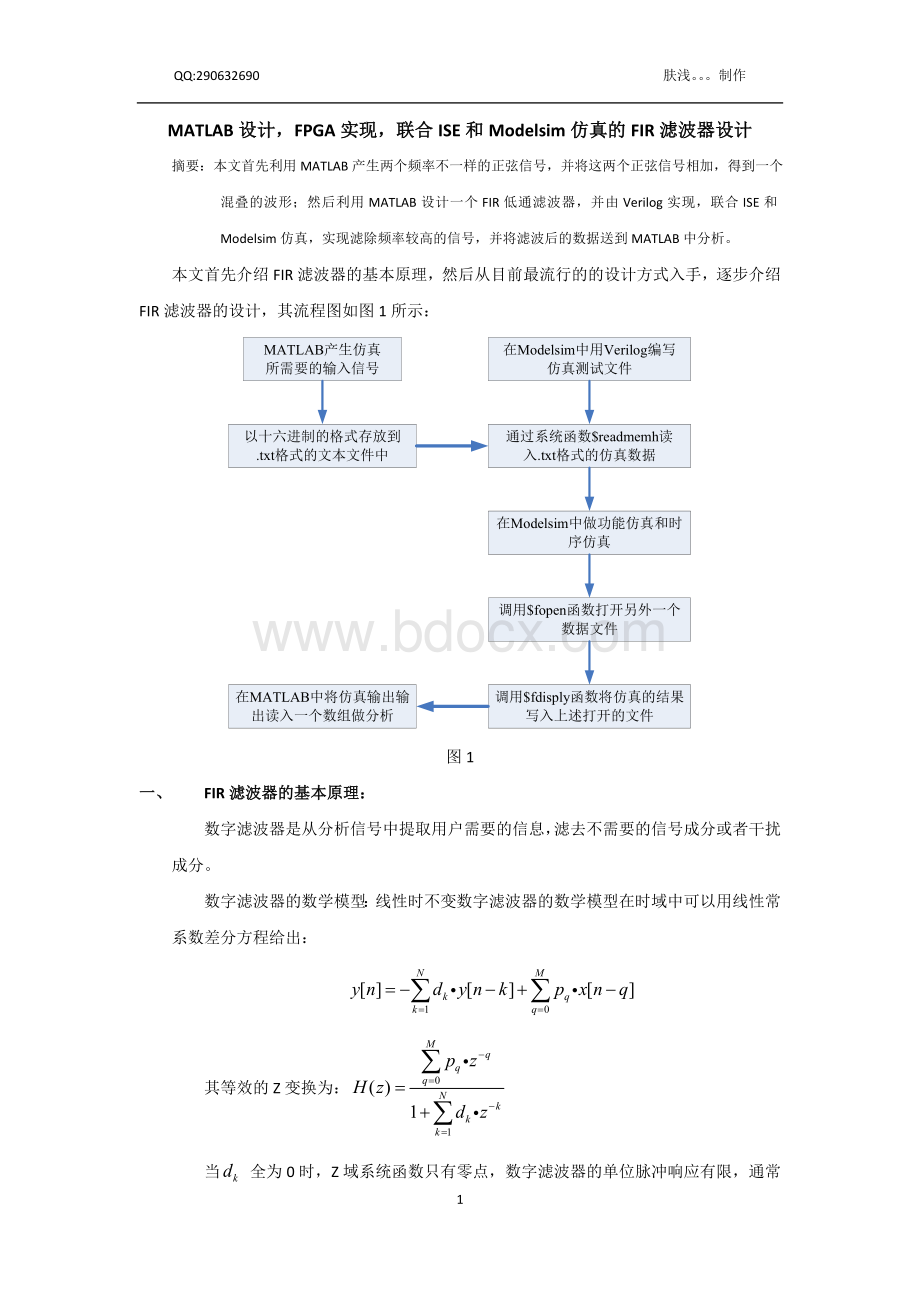

本文首先介绍FIR滤波器的基本原理,然后从目前最流行的的设计方式入手,逐步介绍FIR滤波器的设计,其流程图如图1所示:

图1

一、FIR滤波器的基本原理:

数字滤波器是从分析信号中提取用户需要的信息,滤去不需要的信号成分或者干扰成分。

数字滤波器的数学模型:

线性时不变数字滤波器的数学模型在时域中可以用线性常系数差分方程给出:

其等效的Z变换为:

当全为0时,Z域系统函数只有零点,数字滤波器的单位脉冲响应有限,通常这用滤波器被称为有限冲激响应(FIR)滤波器。

它的输出只与当前的输入和过去的输入有关,跟过去的输出无关。

FIR滤波器的一个重要特性是具有线性相位,即系统的相异和频率成正比,可达到无失真传输。

更加详细的介绍FIR滤波器的理论算法知识,请参考别的先关书籍资料、

二、FIR滤波器的设计及验证:

1)由MATLAB产生FIR滤波器的输入数据,并存放到.txt文件中

用MATLAB产生两个频率分别为:

0.5MHz和2MHz的正弦信号,并将这两个正弦信号叠加,得到一个混叠的信号,并将这个混叠信号的波形数据存放到C盘根目录下面的matlab_wave_data.txt文件中。

MATLAB实现代码如下:

clearall;

fs=25000000;%25M采样率

t=0:

1/fs:

0.0002;%共0.0002*25000000=5000个点

f1=500000;

f2=2000000;

signal1=sin(2*pi*f1*t);%频率为0.5MHz的正弦信号

signal2=sin(2*pi*f2*t);%频率为2.0MHz的正弦信

%由于正、余弦波形的值在[0,1]之间,需要量化成16bit,先将数值放大

y2=fix(16384+(2^14-1)*signal1);%量化到15bit

y3=fix(16384+(2^14-1)*signal2);%量化到15bit

y1=y2+y3;%量化到16bit

%再将放大的浮点值量化,并写道到存放在C盘的文本中

fid=fopen('c:

/matlab_wave_data.txt','wt');

fprintf(fid,'%x\n',y1);%以16进制的格式将数据存放到.txt文件中。

如果不用16进制,后面

%读数会出错。

fclose(fid);

plot(y2,'b');

holdon;

plot(y3,'b');

holdon;

plot(y1,'r');

legend('0.5MHz正弦','2MHz正弦','两者叠加');

title('MATLAB产生的两个正弦信号的叠加波形');

信号波形图如图2所示:

图2

存放数据的文件路径、名称已经文本的内容如图3所示:

图3

用MATLAB回读C盘根目录下的matlab_wave_data.txt文件,验证存入的波形数据是否正确,MATLAB代码如下:

fid=fopen('c:

/matlab_wave_data.txt','r');

fori=1:

5001;%一共有5001个数据

num(i)=fscanf(fid,'%x',1);%从fid所指的文件中,以16进制的方式读出一个数据

end

fclose(fid);

figure

(2);

plot(num,'b');

legend('MATLAB从txt文件中读出的原始叠加波形数据');

title('直接回读MATLAB产生的两个正弦信号的叠加波形');

显示的波形如图4所示:

图4

对比图4和图2中的叠加波形,可知以上操作的正确性。

2)用MATLAB设计FIR滤波器

输入信号是频率别为0.5MHz和2MHz的正弦信号的叠加,我们的任务是设计一个低通滤波器滤除掉2MHz的干扰信号。

因此,我们可以设计一个采样率为25MHz的低通滤波器,其通带带宽为1MHz,阻带宽度为2MHz。

通带内纹波抖动为1dB,阻带下降为80dB。

在MATLAB的命令窗口输入:

fdatool命令并回车,打开FDATool工具箱,用MATLAB的FDATool工具设计该滤波器,参数设置如图5所示:

设计好参数后,点击DesignFilter,可以在FDATool窗口的左上角看到滤波器的阶数为63阶,点击FileàGenerateM-file,并将滤波器命名为mylowfilter。

图5

编写如下代码,滤除混叠信号中的高频信号。

Hd=mylowfilter;%滤波器名称

output=filter(Hd,y1);%对叠加信号y,进行滤波处理

figure(3);

plot(y2,'k');

holdon;

plot(output,'r');

legend('0.5MHz原始信号','滤波后取出的信号');

title('信号通过MTALAB的低通滤波器后的波形');

滤波后的波形如图6所示:

图6

生成.coe文件,用于Xilinx的IPCore设计滤波器,FDATool窗口点击FileàExport…,保持默认设置,点击Export即可,次数在MATLAB的workspace窗口多出一个Num的1*64的数组,这就是滤波器的系数,如图7所示:

图7

由于MATLAB生成的滤波器系数全是一些小数,而FPGA只能处理整数,因此我们必须将这些小数扩大一定的倍数,使它们变成整数。

在MATLAB的命令窗口输入下面的一段代码然后按Enter,即可将上面这些系数变为整数,注意这里的*32767,表示将系数扩大32767倍,这里的扩大倍数只能选2^N,目的是为了后面滤波后的波形数据的高位截取(丢掉低位,即除以2^N)。

返回ans=0,表示操作正确。

coeff=round(Num/max(abs(Num))*32767);

%abs()求绝对值,max()求最大值,round()四舍五入

fid=fopen('e:

/fircoe.txt','wt');%将滤波器系数写入文件件中

fprintf(fid,'%16.0f\n',coeff);%将滤波器系数以16位浮点数的格式保存

fclose(fid)

程序运行的结果如图8所示:

图8

将文件的格式改为.coe格式,在文件的开口加上:

radix=10;

coefdata=

在每个数字前的空格处加一个逗号“,”,并在最后一个数字后面加上分号“;”如图9所示:

图9

这样就产生了可供FIR滤波器的IPCore可调用的.coe文件。

3)用Verilog编程读取MATLAB产生的波形数据

通过Verilog的$readmemh()函数即可读出.txt文件中的数据(这里的数据是以16进制形式存储的),具体用法如下:

reg[15:

0]data_in[0:

2000];//定义一个16bit*2001的数组

initialbegin//读出MATLAB产生的波形数据0.5MHz_sin+4MHz_sin信号

$readmemh("c:

/matlab_wave_data.txt",data_in);

//将matlab_wave_data.txt中的数据读入存储器data_in

End

我在modelsim中尝试用readmemh来读取matlab生成的数据,但是一旦到了负数的地方就出现问题了,之后的所有数据都变成了xxxxx,因此我在用MATLAB产生波形数据时都给正弦信号添加了一个偏移量,将正弦信号平移到了0之上。

用Modelsim仿真工具可以看到读出的数据,并与原文件数据(图3)比较,可以判断读出的数据是否正确,这里是ISE和Modelsim联合仿真的结果,如图10所示:

图10

4)由Xilinx的FIR的IPCore实现FIR滤波器

FIR的IPCore的生成步骤就不多说了,简单的说一下参数配置情况:

a)我们使用由MATLAB生成的.coe文件导入滤波器的系数。

b)输入信号的采样频率为25MHz,这里必须和MATLAB产生的波形数据的采样频率保持一致。

c)FIR滤波器的运行时钟,这里我们选择250MHz,这里必须和仿真文件里给的时钟保持一致。

d)输入数据的类型,我们这里选择了无符号数,输入数据位宽为16bit,因为modelsim不能读出负数(要么用补码,要么加偏移)。

如图11、图12所示:

图11

图12

FIR的IPCore的列化如下:

FIR16_IPFIR16_IP_ins(

.clk(clk),//inputclk

.rfd(rfd),//outputrfd在其上升沿将输入数据加载到滤波器内核中

.rdy(rdy),//outputrdy在其上升沿输出滤波器的计算结果

.din(data_in_reg),//input[15:

0]din

.dout(dout));//output[35:

0]dout特别注意这个数据位宽

我们主要对其进行简单的控制:

在rfd上升沿将输入数据加载到滤波器内核中,在rdy上升沿输出滤波器的计算结果。

具体的Verilog代码如下:

always@(posedgeclk)begin

if(reset==1'b0)begin

i <= 1'b0;

m <= 1'b0;

data_in_reg <= 16'h0000;

end

elsebegin

rfd_1q <= rfd;

rfd_2q <= rfd_1q;

if(rfd_1q&~rfd)begin //rfd信号的上升沿将输入数据加载到滤波器内核中

data_in_reg <= data_in[i];

i <= i+1;

m<= ~m;

if(i==2002)

i <= 0;

end

end

end

always@(posedgeclk)begin

if(reset==1'b0)begin

Data_out_reg <= 0;

j <= 0;

n <= 0;

end

elsebegin

rdy_1q <= rdy;

rdy_2q <= rdy_1q;

if(rdy_1q&~rdy)begin

Data_out_reg <= dout;

j <= j+1'b1;

n<= ~n;

end

end

end