FPGA数码管计数器实验.doc

《FPGA数码管计数器实验.doc》由会员分享,可在线阅读,更多相关《FPGA数码管计数器实验.doc(2页珍藏版)》请在冰豆网上搜索。

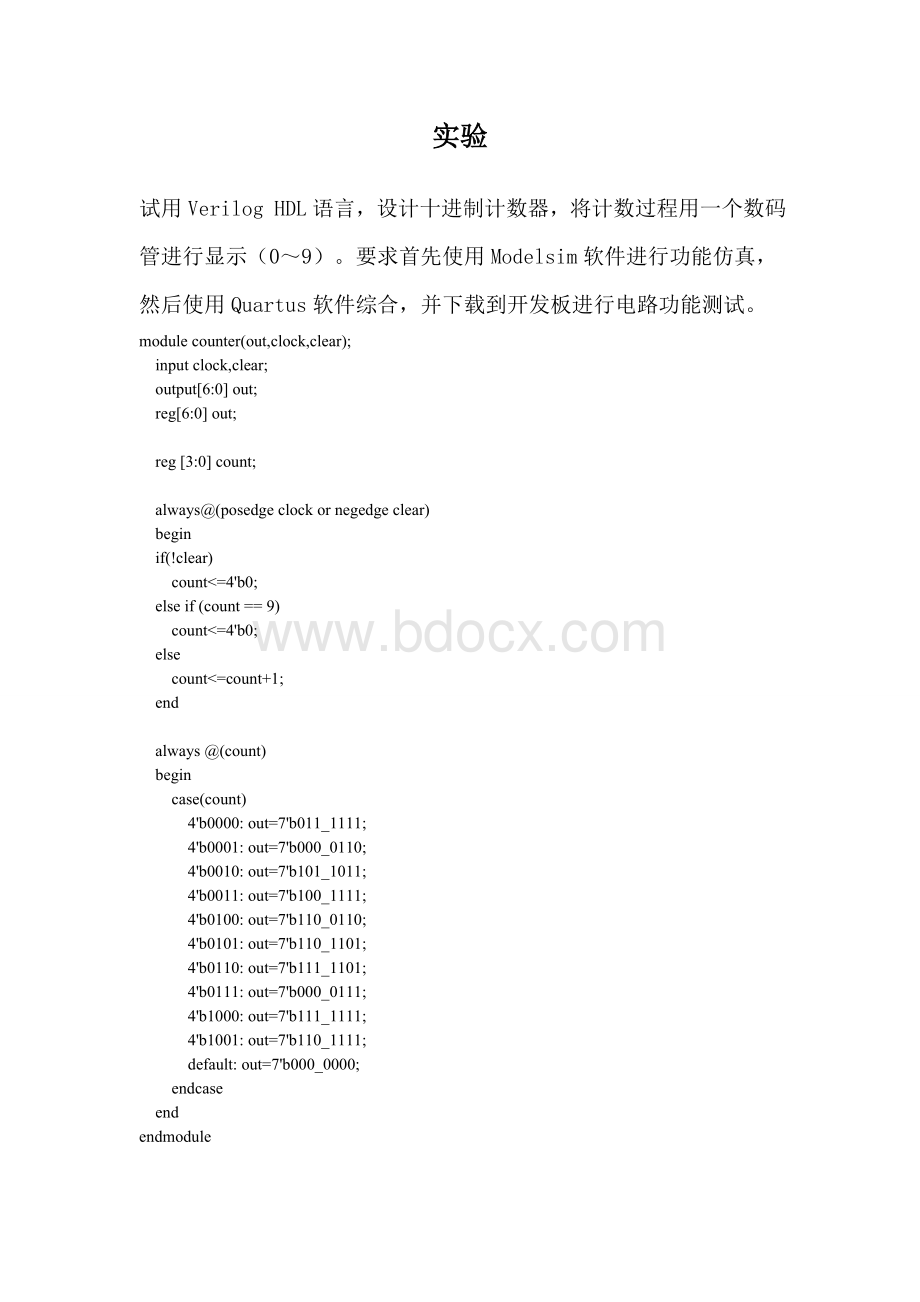

实验

试用VerilogHDL语言,设计十进制计数器,将计数过程用一个数码管进行显示(0~9)。

要求首先使用Modelsim软件进行功能仿真,然后使用Quartus软件综合,并下载到开发板进行电路功能测试。

modulecounter(out,clock,clear);

inputclock,clear;

output[6:

0]out;

reg[6:

0]out;

reg[3:

0]count;

always@(posedgeclockornegedgeclear)

begin

if(!

clear)

count<=4'b0;

elseif(count==9)

count<=4'b0;

else

count<=count+1;

end

always@(count)

begin

case(count)

4'b0000:

out=7'b011_1111;

4'b0001:

out=7'b000_0110;

4'b0010:

out=7'b101_1011;

4'b0011:

out=7'b100_1111;

4'b0100:

out=7'b110_0110;

4'b0101:

out=7'b110_1101;

4'b0110:

out=7'b111_1101;

4'b0111:

out=7'b000_0111;

4'b1000:

out=7'b111_1111;

4'b1001:

out=7'b110_1111;

default:

out=7'b000_0000;

endcase

end

endmodule

`timescale1ns/1ns

`include"./counter.v"

moduletest;

regClock,Clear;

wire[6:

0]Out;

initial

begin

Clock=0;

Clear=1;

#50Clear=0;

#500Clear=1;

end

always#50Clock=~Clock;

counterm(.out(Out),.clock(Clock),.clear(Clear));

endmodule