DDS原理及实现.doc

《DDS原理及实现.doc》由会员分享,可在线阅读,更多相关《DDS原理及实现.doc(7页珍藏版)》请在冰豆网上搜索。

1DDS原理简介

数字频率合成器(DirectDigitalSynthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术。

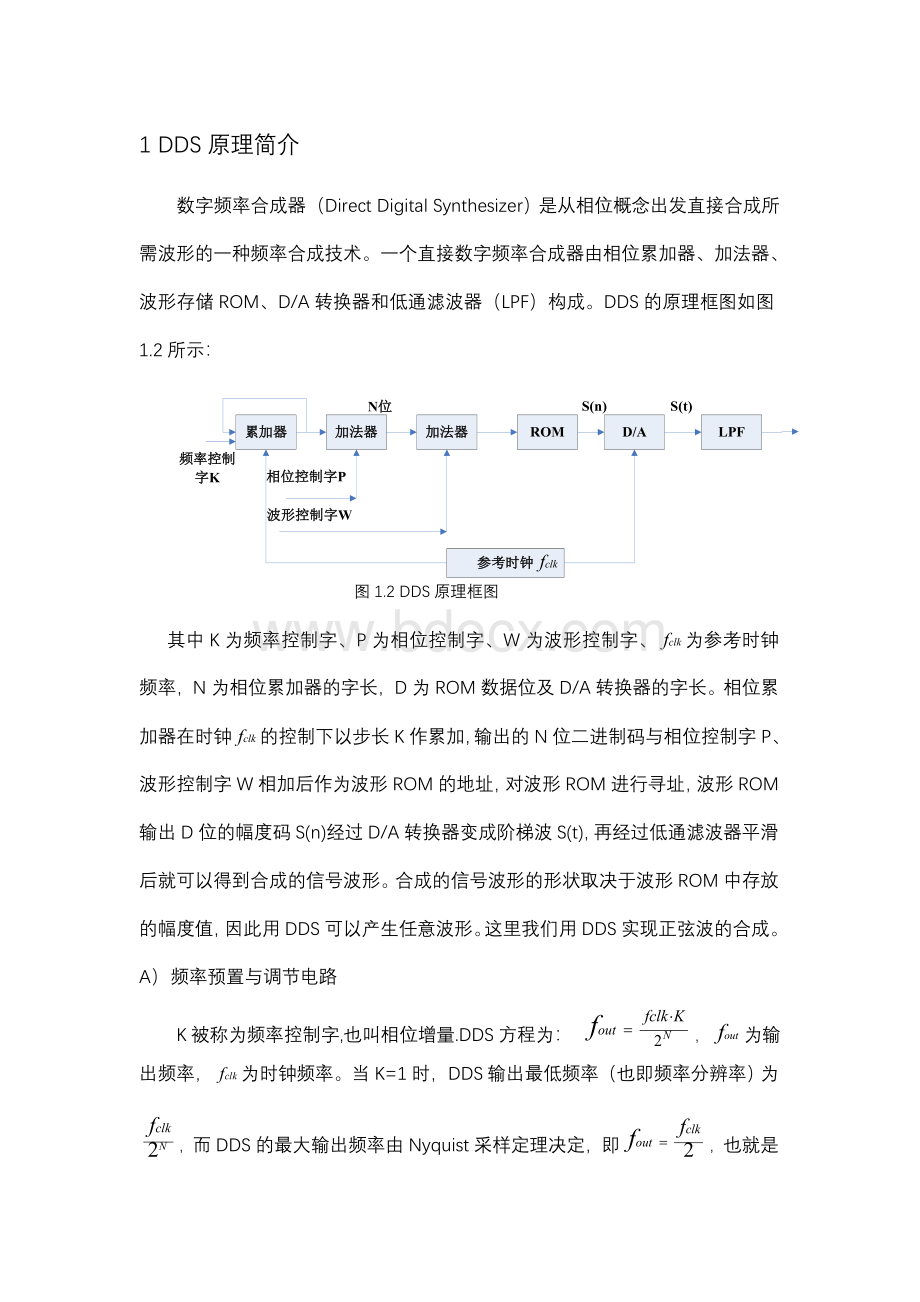

一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器(LPF)构成。

DDS的原理框图如图1.2所示:

图1.2DDS原理框图

其中K为频率控制字、P为相位控制字、W为波形控制字、为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。

相位累加器在时钟的控制下以步长K作累加,输出的N位二进制码与相位控制字P、波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位的幅度码S(n)经过D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。

合成的信号波形的形状取决于波形ROM中存放的幅度值,因此用DDS可以产生任意波形。

这里我们用DDS实现正弦波的合成。

A)频率预置与调节电路

K被称为频率控制字,也叫相位增量.DDS方程为:

,为输出频率,为时钟频率。

当K=1时,DDS输出最低频率(也即频率分辨率)为,而DDS的最大输出频率由Nyquist采样定理决定,即,也就是说K最大值为。

因此,只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS的输出频率,只要改变频率控制字K即可。

B)累加器

相位累加器由N位加法器与N位寄存器级联构成。

每来一个时钟脉冲,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。

寄存器将加法器在上一个时钟作用后所产生的相位数据反馈到加法器的输入端;以使加法器在下一个时钟的作用下继续与频率控制字进行相加。

这样,相位累加器在时钟作用下,进行相位累加。

当相位累加器累加满量里就会产生一次溢出,完成一个周期性的动作。

C)控制相位的累加器

通过改变相位控制字P可以控制输出信号的相位参数。

令相位加法器的字长为N,当相位控制字由0跃变到P(P0)时,波形存储器的输入为相位累加器的输出与相位控制字P之和,因而其输出的幅度编码相位会增加,从而使最后输出的信号产生相移。

D)控制波形的加法器

通过改变波形控制字W可以控制输出信号的波形。

由于波形存储器中的不同波形是分块存储的,所以当波形控制字改变时,波形存储器的输入为改变相位后的地址与波形控制字W(波形地址)之和,从而使最后输出的信号产生相移。

E)波形存储器

用相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位—幅

值转换,即可以给定的时间上确定输出的波形的抽样幅值。

N位的寻址ROM相当于把0°~360°的正弦信号离散成具有个样值的序列,若波形ROM有D位数据位,则个样值的幅值以D位二进制数值固化在ROM中,按照地址的不同可以输出相应相位的正弦信号的幅值。

E)D/A转换器

D/A转换器的作用是把合成的正弦波数字量转换成模拟量。

正弦幅度量化序列S(n)经D/A转换后变成了包络为正弦波的阶梯波S(t)。

需要注意的是,频率合成器对D/A转换器的分辨率有一定的要求,D/A转换器的分辨率越高,合成的正弦波S(t)台阶数就越多,输出波形的精度也就越高。

F)低通滤波器

对D/A输出的阶梯波S(t)进行频谱分析,可以S(t)中除了主频外,还相存在分布在,2……两边正负处的非谐波分量,幅值包络为辛格函数。

因此,为了取出主频,必须在D/A转换器的输出端接入截止频率为/2的低通滤波器。

2FPGA的DDS载波实现方法

实现通信中不少信道都不能直接传送基带信号,必须用基带信号对载波波形的某些参量进行控制,使载波的这些参量随基带信号的变化而变化,即所谓正弦载波调制。

从原理上来说,受调载波的波形可以是任意的,只要已调信号适合于信道传输就可以了。

但实际上,在大多数数字通信系统中,都选择正弦信号作为载波。

这是因为正弦信号形式简单,便于产生及接收。

方法一:

用ROM核来实现

说明:

将载波一个周期的采样值直接写入V代码中的,而不是用ROM核。

(利用ROM核需要将载波一个周期的采样值写入COE文件中,插入ROM核中)

优点:

用不同的初始值寻址可以输出不同频率和不同初始相位的载波。

方法二:

用DDS核来实现

优点:

频率和初始相位都可以任意设定。

缺点:

在使用时比较难控制

方法三:

用Sine-CosineLook-upTable核来实现

l代码:

modulesine__cosine(clk,reset,in_rdy,desine,decosine,out_rdy);

inputclk,reset,in_rdy;

output[7:

0]desine,decosine;

outputout_rdy;

wireout_rdy;

wireRFD,RDY;

regND;

reg[3:

0]THETA;

always@(posedgeclk)

begin

if(reset)beginND<=0;THETA<=0;end

elseif(in_rdy)

beginTHETA<=THETA+1;

ND<=in_rdy;

end

end、

//核例化

sinecosinesinecosine(

.THETA(THETA),//Bus[3:

0]

.CLK(clk),

.SCLR(reset),

.ND(ND),

.RFD(RFD),

.RDY(out_rdy),

.SINE(desine),//Bus[7:

0]

.COSINE(decosine));//Bus[7:

0]

endmodule

l仿真图:

第一路为正弦波,第二路为余弦波

l说明:

可以对THETA赋不同初始值即可以实现不同初始相位的载波。

此正弦波和余弦波一个周期是采样16个点,可以在IP核进行参数设置修改的。

其频率为,输出位宽为8位宽。

优点:

载波频率是时钟频率的

其中N在IP核中可设置,设置很简单,初始相位也可以通过修改THETA参数来实现,实现起来很方便。

也比较容易控制。

方法四:

将载波一个周期的采样点值写入代码中来实现。

l代码:

modulesine(clk,reset,en,out_rdy,out);

inputclk,reset,en;

outputout_rdy;

output[7:

0]out;

regout_rdy;

reg[7:

0]out;

reg[2:

0]addr;

always@(posedgeclk)

begin:

initial_control

if(reset)begin

addr<=3'd0;

end

elseif(en)begin

addr<=addr+1;

end

end

always@(posedgeclk)

begin:

Red_sig

if(en)

case(addr)

4'd0:

beginout<=8'd45;out_rdy<=1;end

4'd1:

beginout<=8'd64;out_rdy<=1;end

4'd2:

beginout<=8'd45;out_rdy<=1;end

4'd3:

beginout<=8'd0;out_rdy<=1;end

4'd4:

beginout<=8'd211;out_rdy<=1;end

4'd5:

beginout<=8'd192;out_rdy<=1;end

4'd6:

beginout<=8'd211;out_rdy<=1;end

4'd7:

beginout<=8'd0;out_rdy<=1;end

endcase

end

endmodule

l仿真图:

l说明:

此正弦载波一个周期是采样8个点,即频率为

其输出位宽为8位宽。

若想产生余弦载波的话,只需将Red_sig中out的值改变即可。

优点:

与模块使能信号en同时输出,没有延时。

在设计调制解调时,不用设计基带信号与载波同步。

相对于用核产生要方便一些,因为用核产生时,因为设置了握手信号,载波较使能信号都有固定时间的延时,例如用Sine-CosineLook-upTable核来实现载波时,一般都有2或3个系统时钟的延时,致使载波与基带信号不同步,需将基带信号延时以使两路信号同步。

缺点:

若载波的一个周期采样多个点的话,将采样值直接写入V代码中,就有点麻烦了。