基于eda的数字钟程序设计.docx

《基于eda的数字钟程序设计.docx》由会员分享,可在线阅读,更多相关《基于eda的数字钟程序设计.docx(21页珍藏版)》请在冰豆网上搜索。

基于eda的数字钟程序设计

一、课题要求:

(1)技术要求:

1、掌握多功能数字钟的工作原理。

2、应用EDA技术,VHDL语言编写程序。

3、层次化设计,设计原理框图。

4,、硬件设计及排版。

(2)功能要求:

1、基本功能:

能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时、60分钟、60秒的计数器显示。

2、扩展功能:

(1)能够利用按键实现“校时”“校分”

“清零”功能。

(2)能利用扬声器做整点报时,整点前

五秒短声,整点长声。

(3)本人工作:

负责软件部分,,编写各部分模块的VHDL程序,并且锁定引脚,将程序下载到芯片中。

二、设计方案:

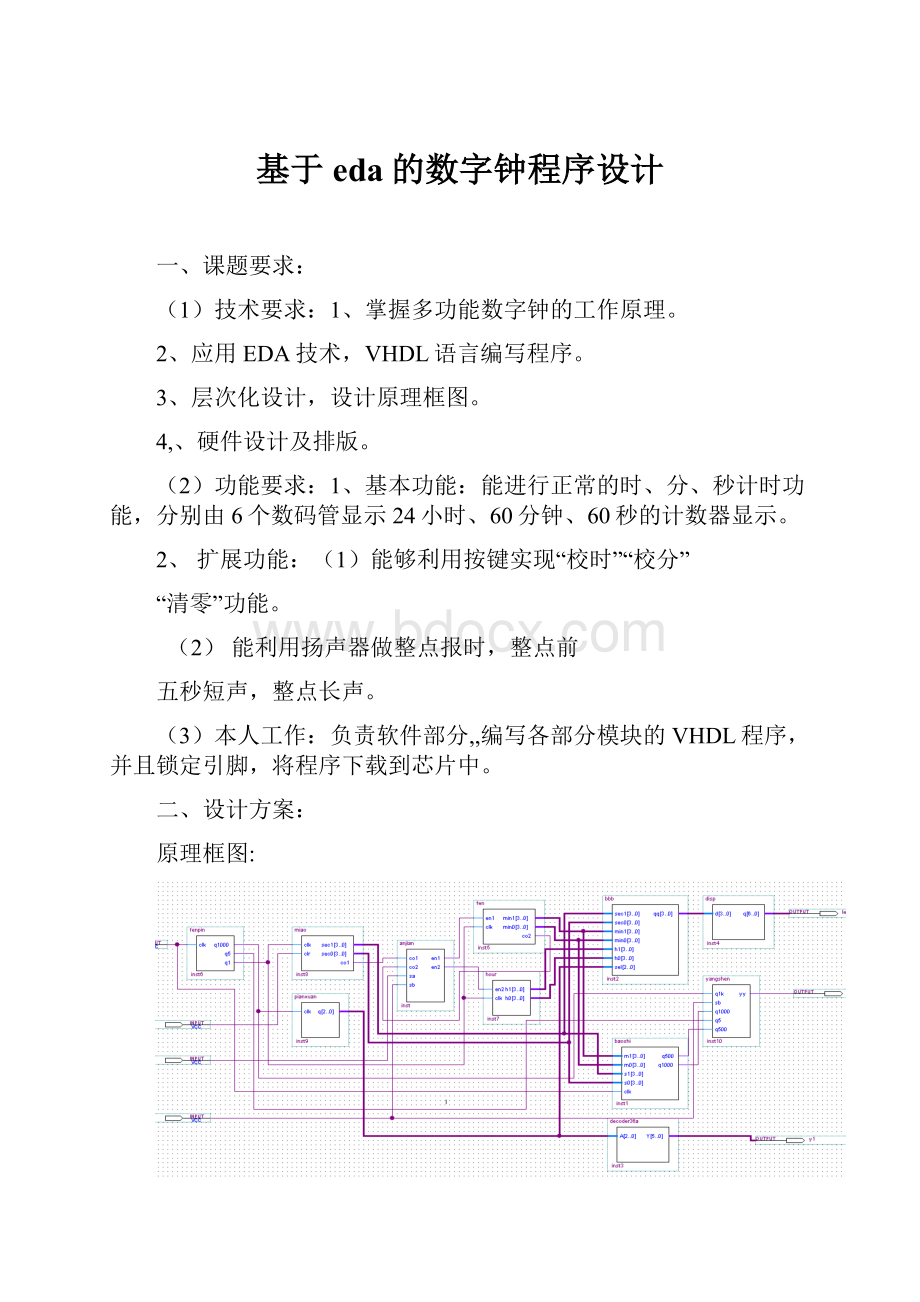

原理框图:

数字钟原理框图

一共有11个小模块:

分频,片选,按键,小时,分,秒,显示模块,七段显示译码器,报

时,扬声,36译码器。

左边第一个是时钟信号输入端,50Mhz到分频模块。

第二个为清零按键,第三个为校分按

键,第四个为校时按键。

右边第一个为七段显示译码器输出端,第二个为扬声器输出端,第三个为6个数码管输出

端。

中间模块为数字钟的核心,有计时,报时,校时功能。

三、单元模块设计

1、分频模块

该模块是将时钟脉冲50Mhz分频到1000、500和1,分别给报时模块和及时模块。

2、秒模块

仿真图

该模块为60进制计数器,有分频模块得到的1hz进行计时,计时输出为秒的数值,在计时到59时进位1到co端。

当按下s3时,秒清零。

3.、分模块

仿真图

该模块也为60进制计数器,计时输出为分的数值。

在EN信号有效且时钟来时,计数器加1、在s2按下时,EN使能端有效,实现校分功能。

4、时模块

仿真图

该模块为24进制计数器,计时输出为小时的数值,在EN信号到来时,计数器加1,在S1按下时,EN信号有效,实现校时功能。

5、片选模块

仿真图

该模块提供数码管片选信号。

6、按键模块

仿真图

该模块是有几个门电路组成,把它编写成一个模块,到时写程序方便。

该模块连接几个按键,由按键控制。

7、报时模块

仿真图

该模块为整点报时提供控制信号,当59分时,秒为50,52,54,56,58时,Q500输出“1”;秒为00时,Q1000输出“1”。

这两个信号经过逻辑门实现报时功能。

8、BBB模块

仿真图

该模块对应不同的片选信号送出不同的要显示的数据。

9、36译码器模块

仿真图

该模块为36译码器,为输出到数码管对应功能。

10、七段译码器模块

仿真图

该模块为七段译码器,输出到数码管的每一个引脚,可以正确的点亮每一个数码管。

11、扬声模块

仿真图

该模块也为几个门电路组合,控制着对扬声器的输入,当时间到达某一点时,输出不同的脉冲信号到扬声器,给予扬声器信号。

四、顶层模块设计

程序图:

总体框图

顶层文件将上面11个小模块集合到一起构成了总的程序,最终也是将这个顶层文件写到FPGA芯片中。

五、硬件电路设计

由另一位同学负责,收集好器件,将器件排版在电路板上,并将其焊接成成品。

六、硬件电路安装及调试

在EDA中,将顶层文件各个输入与输出端口锁定引脚。

锁定好引脚后将整个顶层文件下载到FPGA芯片中。

注:

在下载时,要注意先安装USB程序,再设置IDE环境设置,然后再programmer中选择自己要的文件,下载时必须先安装好芯片再接电源,下载成功后,先拔电源,再拔下USB。

下载好以后,用杜邦线将硬件和芯片的引脚连接好,检查无误后进行测试。

七、调试结果

为了每个模块的正确性,将一一对每个模块进行测试。

将芯片与硬件连接好,检查无误后,打开电源,此时硬件上的数码管开始计时,等到秒为59时,下一秒,分为1,秒为00。

然后用校时功能按键将分校分到59分,此时当秒为50时,扬声器开始响,并且到整点时,扬声器持续响一段时间。

按下S3,秒清零。

调试结束,基本功能能够计时,并且进位到分和时,扩展功能,按下S2和S3后能够进行分和时的校时,并且到整点时开始报时。

八、设计中遇到的问题及解决方案

我负责软件部分,开始在编写程序时根本无从下手,再找了一些资料后终于对数字钟有些了解。

用EDA设计每一个模块,都需要一个一个的去仿真,看程序对不对,经常在一些小程序上出现问题。

本来有好多门电路,发现放在顶层文件中比较麻烦,所以将这些门电路组成两个模块,按键模块和扬声模块,这样方便顶层文件的编写。

分频模块,由于要将50MHz的脉冲分到1000Hz,500Hz,和1Hz,分频量比较大,不能仿真,只能先改小一下数据,验证程序是否正确。

36译码器部分,本来使用的是38译码器,发现多了2个输入,有6个数码管,但是38译码器并不影响输出。

在下载过程,锁定引脚,发现芯片上的引脚与硬件上的引脚是反的,数码管显示的是乱码。

当数字钟的时分秒顺序错了以后,不需要重新锁定引脚,只要将对应的杜邦线对调一下就行了。

我们校时用的按键是自锁开关,其实只要改成下拉电阻就可以了。

九、收获与体会

经过两个星期的数电课程设计,收获很大,让我们自己设计了数电模型,从软件和硬件上学到了很多知识。

两个同学一个设计软件,一个设计硬件,不仅提高了学习能力,还培养了团队合作能力。

我负责的是软件部分,这学期正好学习了EDA技术,把它应用到了软件的程序编写中来。

我们设计的是数字钟,虽然数字钟看起来很简单,但是要把每个模块全部搞在一起还是有点难度的。

开始经过上网及图书馆借书来了解数字钟的结构与工作原理,把它每一部分的模块摸透清楚后,在开始编程,写入芯片。

同时还要把软件与硬件结合起来,在各自做各自的工作时还要紧密结合自己组员的工作,只有两个人的东西做完后,组合起来才算真正的完成。

首先明确好数字钟的功能,基本功能:

能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时、60分钟、60秒的计数器显示。

扩展功能:

(1)能够利用按键实现“校时”“校分”“清零”功能。

(2)能利用扬声器做整点报时,整点前五秒短声,整点长声。

然后设计好总的原理图,将功能全部覆盖进去,设计每个模块,用EDA中的VHDL编写程序,然后再仿真,根据仿真图检测自己的程序是否正确。

当每个模块在电脑中仿真无误时,编写顶层文件,把各个小模块连接到一起,然后将整个程序画出原理框图,与自己预测的相比较。

当软件做好后,用下载线将自己写的程序写进芯片中,不过此时要注意先连接好线才能开电源,当下载后,要先关电源,再拔USB接口。

下载后与同组同学用杜邦线连接开始测试,第一次先将整个程序写入,发现没有正确显示,然后一个一个模块检测后,发现了问题,终于数字钟做好了,基本功能与扩展功能都出来了。

这次课程设计后,软件方面有着明显的提高,而且合作啊能力也提高了,作品完成的还是很好的。

首先要感谢老师的细心教导,让我学习到了好多知识,从硬件到软件,不仅仅是知识上,还有能力上,还要感谢同组同学,没有他的硬件,这次数字钟也完不成。

这次收获还是很大的,自己的努力与汗水终于没有出,总结这次课程设计的经验,在以后的课程设计中能够更好的发挥!

十、参考文献:

1、《EDA技术与VHDL》清华大学出版社

2、《数字系统设计与VerilogHDL(第三版)》王金明编著

3、《EDA技术与应用(第2版)》江国强编著

4、《EDA技术实用教程》科学出版社