EDA实验报告.docx

《EDA实验报告.docx》由会员分享,可在线阅读,更多相关《EDA实验报告.docx(13页珍藏版)》请在冰豆网上搜索。

EDA实验报告

EDA技术与Verilog设计实验报告

专业班级:

姓名:

学号:

日期:

2011年10月30日

一、半加器和全加器的设计

1.实验目的:

通过一位全加器的设计和仿真,熟悉基于QuartusⅡ软件进行原理图设计的基本流程。

该全加器通过两步实现,首先设计一个半加器,将半加器生成原理图符号,以供调用,然后用半加器构成全加器。

2.原理图设计源文件

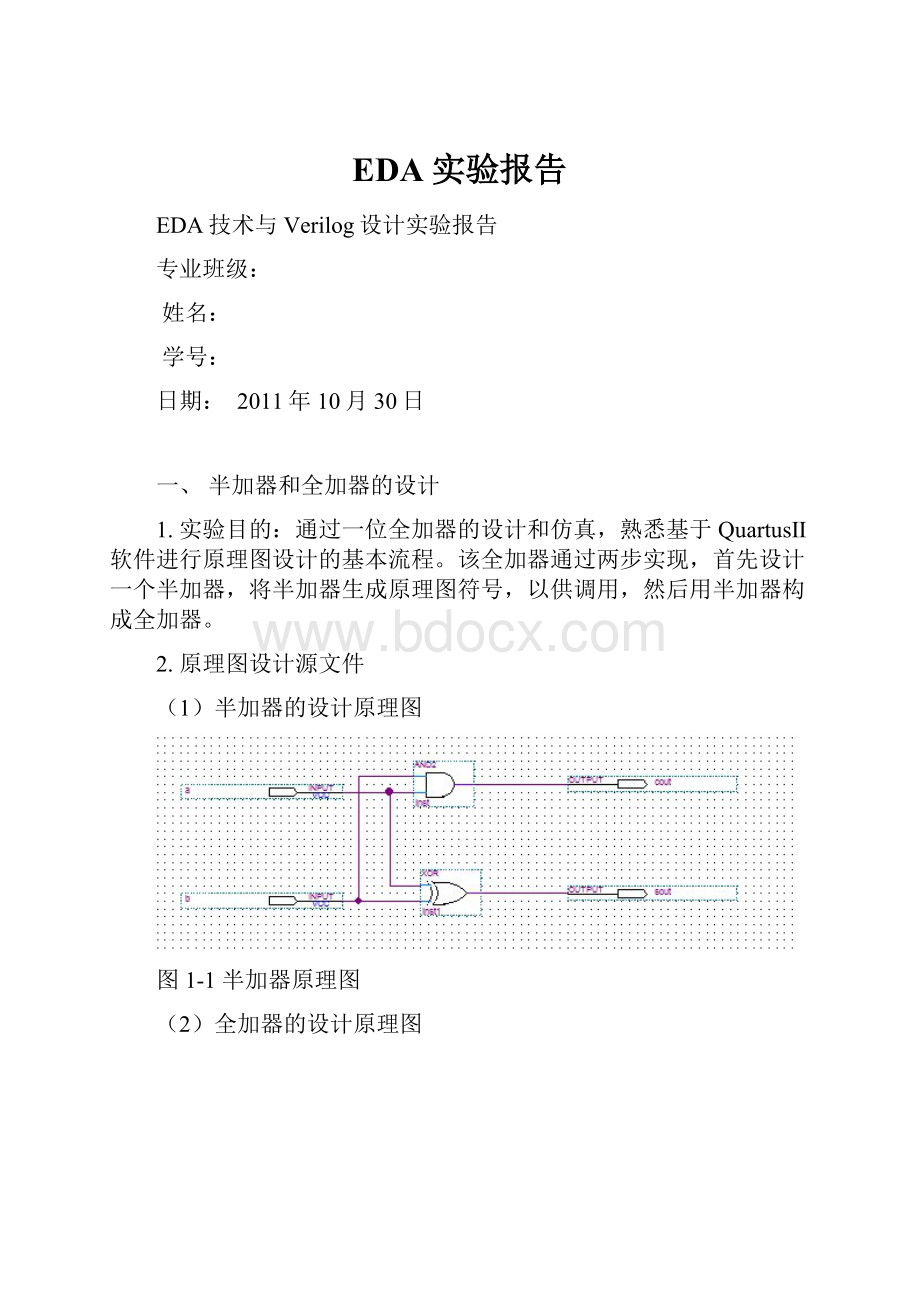

(1)半加器的设计原理图

图1-1半加器原理图

(2)全加器的设计原理图

图1-2全加器原理图

3.设计仿真图

(1)半加器的功能仿真图

图1-3半加器功能仿真图

(2)全加器的功能仿真图

图1-4全加器功能仿真图

二、四选一数据选择器的设计

1.实验目的:

通过四选一数据选择器的设计熟悉synpilify软件的使用及verilog语言设计方法,并观察设计的综合结果是否符合要求。

2.四选一数据选择器的verilog语言设计源程序

modulemux4_1(out,in0,in1,in2,in3,sel);

inputin0,in1,in2,in3;

input[1:

0]sel;

outputout;

regout;

always@(in0orin1orin2orin3orsel)

case(sel)

2'b00:

out=in0;

2'b01:

out=in1;

2'b10:

out=in2;

2'b11:

out=in3;

default:

out=2'bx;

endcase

endmodule

3.四选一数据选择器的逻辑综合图

(1)RTL级综合图

图2-1四选一数据选择器RTL级综合图

(3)门级综合图

图2-2四选一数据选择器门级综合图

三、基于QuartusⅡ图形输入电路的设计

1.实验目的

(1)通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

(2)初步了解QuartusⅡ原理图输入设计的全过程。

(3)掌握组合逻辑电路的静态测试方法。

2.实验原理

3—8译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其他则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

其真值表如表3—1所示。

表3-13-8译码器真值表

输入

输出

ABC

D7D6D5D4D3D2D1D0

000

100

010

110

001

101

011

111

00000001

00000010

00000100

00001000

00010000

00100000

01000000

10000000

3.3-8译码器的设计原理图

图3-13-8译码器原理图

4.3-8译码器的功能仿真图形

图3-23-8译码器功能仿真图

四、含异步清零和同步时能的加法计数器

1.实验目的

(1)了解二进制计数器的工作原理。

(2)进一步熟悉QuartusⅡ软件的使用方法和verilog输入。

(3)时钟在编程过程中得作用。

2.实验原理

二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:

在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数器清零,继续进行检测和计数。

3.加法计数器的verilog语言设计程序

moduleCOUNT(cout,cq0,cq1,cq2,cq3,clk,en,ret);

inputclk,en,ret;

outputcout,cq0,cq1,cq2,cq3;

regcout,cq0,cq1,cq2,cq3;

always@(posedgeclkornegedgeret)

begin

if(!

ret)

begin

{cq0,cq1,cq2,cq3}<=4'b0000;cout<=1'b0;

end

elseif(en)

begin

{cq0,cq1,cq2,cq3}<={cq0,cq1,cq2,cq3}+1;

cout<=cq0&!

cq1&!

cq2&cq3;

if({cq0,cq1,cq2,cq3}==4'b1001){cq0,cq1,cq2,cq3}<=4'b0000;

end

end

endmodule

4.加法计数器的功能仿真图形

图4-1含异步清零和同步使能的加法计数器的功能仿真图

五、多功能数字钟的设计

1.实验目的

(1)了解数字钟的工作原理。

(2)进一步熟悉用verilog语言编写驱动七段数码管显示的代码。

(3)掌握verilog编写中得一些技巧。

2.实验原理

多功能数字钟应该具有的功能有:

显示时—分—秒、整点报时、小时和分钟可调等基本功能。

首先要知道钟表的基本原理,整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加一秒,当秒从59秒跳转到00秒时,分钟增加一分,同时当分钟从59分跳转到00分时,小时增加一小时,但是需要注意的是,小时的范围是从0~23小时。

在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个三位的二进制码显示十位,用一个四位的二进制码(BCD码)显示个位,对于小时因为它的范围是从0~23,所以可以用一个二位的二进制码显示十位,用四位二进制码显示个位。

实验中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz时钟信号,但是扫描却需要一个比较高频率的信号,因此为了得到准确的1Hz信号,必须对输入的系统时钟进行分频。

对于整点报时功能,用户可以根据系统的硬件结构和自身的具体要求来设计。

本实验设计的是当进行整点的倒计时5秒时,让LED灯来闪烁进行整点报时的提示。

3.多功能数字钟的verilog语言设计程序

moduleclock1(clk,s1,s2,rst,hour,min,sec,spk,q,sel,led,minclk,hclk);

inputclk,s1,s2,rst;

outputspk;

output[3:

0]led;

output[7:

0]hour,min,sec;

output[6:

0]q;

output[2:

0]sel;

outputminclk,hclk;

reg[16:

0]counter_clk;//扫描时钟信号

reg[6:

0]q;//数码管输出信号

reg[7:

0]hour1,min1,sec1;

reg[2:

0]sel;//位选信号

regdiv_clk;//分频信号

regminclk,hclk;//向分钟和小时进位信号

regspk;//整点报时信号

reg[3:

0]led;

wirect1,ct2;

always@(negedgerstorposedgeclk)//对系统时钟进行10000分频

begin

if(~rst)

begin

counter_clk<=16'h0000;

div_clk<=1'b0;

end

else

begin

if(counter_clk==16'h1387)

begin

counter_clk<=16'h0000;

div_clk<=~div_clk;

end

elsecounter_clk<=counter_clk+1;

end

end

assignct1=(~s1)|minclk;//ct1用于计时、校时中的分钟计数

assignct2=(~s2)|hclk;//ct1用于计时、校时中的小时计数

always@(posedgediv_clkornegedgerst)//秒计时进程

if(~rst)sec1<=0;

elseif(sec1==8'h59)

beginsec1<=0;minclk<=1;end

elsebegin

if(sec1[3:

0]==4'b1001)

beginsec1[3:

0]<=4'b0000;sec1[7:

4]<=sec1[7:

4]+1;end

elsesec1[3:

0]<=sec1[3:

0]+1;

minclk<=0;

end

always@(posedgect1ornegedgerst)//分钟计时和分钟调整进程

begin

if(~rst)min1<=0;

elseif(min1==8'h59)beginmin1<=0;hclk<=1;end

elsebegin

if(min1[3:

0]==9)

beginmin1[3:

0]<=0;min1[7:

4]<=min1[7:

4]+1;end

elsemin1[3:

0]<=min1[3:

0]+1;

hclk<=0;

end

end

always@(posedgect2ornegedgerst)//小时计时和小时调整进程

if(~rst)hour1<=0;

elseif(hour1==8'h23)hour1<=0;

elseif(hour1[3:

0]==9)

beginhour1[7:

4]<=hour1[7:

4]+1;hour1[3:

0]<=0;end

elsehour1[3:

0]<=hour1[3:

0]+1;

assignhour=hour1;//时、分、秒的显示控制

assignmin=min1;

assignsec=sec1;

always//产生整点报时信号

begin

if((min1==8'h59)&&(sec1>8'h50)||(!

(min1|sec1)))

if((sec1%2)==0)spk<=1;

elsespk<=0;

elsespk<=0;

end

always//led灯闪烁

begin

if(((min1==8'h59)&&(sec1>8'h55)||(!

(min1|sec1)))&&div_clk)

led=4'b1111;

elseled<=0;

end

always@(posedgeclkornegedgerst)//产生位选信号sel

begin

if(~rst)sel<=3'b000;

else

begin

if(sel==3'b101)sel<=3'b000;

elsesel<=sel+1;

end

end

always@(sel)//由位选信号选择相应数码管

begin

case(sel)

3'b000:

q<=disp(hour1[7:

4]);

3'b001:

q<=disp(hour1[3:

0]);

3'b010:

q<=disp(min1[7:

4]);

3'b011:

q<=disp(min1[3:

0]);

3'b100:

q<=disp(sec1[7:

4]);

3'b101:

q<=disp(sec1[3:

0]);

default:

;

endcase

end

function[6:

0]disp;//数码管显示

input[3:

0]a;

case(a)

4'h0:

disp=7'b0111111;

4'h1:

disp=7'b0000110;

4'h2:

disp=7'b1011011;

4'h3:

disp=7'b1001111;

4'h4:

disp=7'b1100110;

4'h5:

disp=7'b1101101;

4'h6:

disp=7'b1111101;

4'h7:

disp=7'b0000111;

4'h8:

disp=7'b1111111;

4'h9:

disp=7'b1101111;

default:

disp=7'b1111111;

endcase

endfunction

endmodule

4.多功能数字钟的功能仿真图形(分段显示不同时刻的功能仿真图)

图4-1多功能数字钟功能仿真图1

图4-2多功能数字钟功能仿真图2

图4-3多功能数字钟功能仿真图3