TMS320C54DSP原理应用第2章图文.docx

《TMS320C54DSP原理应用第2章图文.docx》由会员分享,可在线阅读,更多相关《TMS320C54DSP原理应用第2章图文.docx(14页珍藏版)》请在冰豆网上搜索。

TMS320C54DSP原理应用第2章图文

第2章TMS320C54x的CPU结构和存储器配置

2.1TMS320C54xDSP的结构

2.2TMS320C54x的总线结构

2.3TMS320C54x的CPU结构

2.4TMS320C54x存储器和I/O空间

2.1TMS320C54xDSP的结构

2.1.1TMS320C54xDSP的基本结构

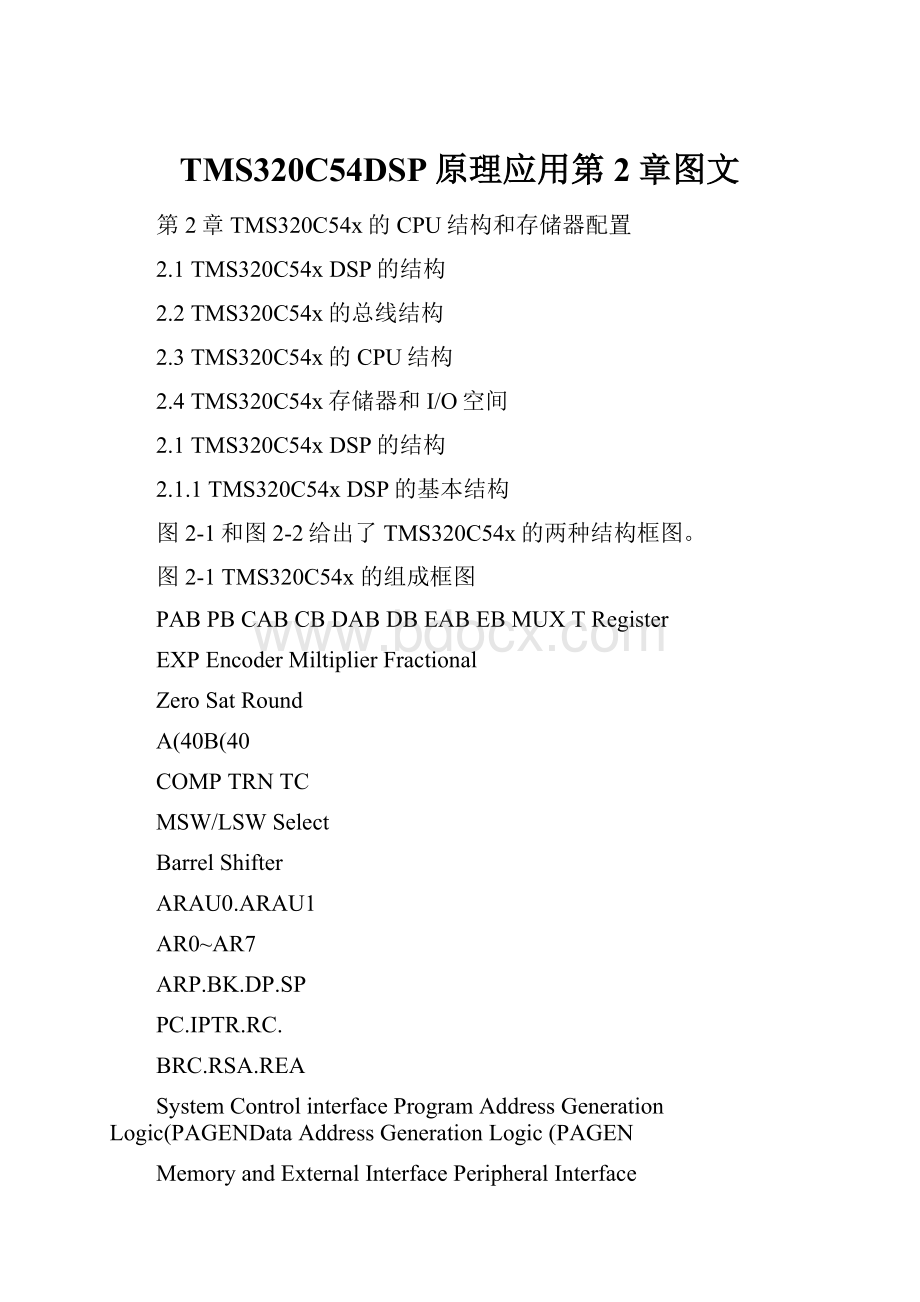

图2-1和图2-2给出了TMS320C54x的两种结构框图。

图2-1TMS320C54x的组成框图

PABPBCABCBDABDBEABEBMUXTRegister

EXPEncoderMiltiplierFractional

ZeroSatRound

A(40B(40

COMPTRNTC

MSW/LSWSelect

BarrelShifter

ARAU0.ARAU1

AR0~AR7

ARP.BK.DP.SP

PC.IPTR.RC.

BRC.RSA.REA

SystemControlinterfaceProgramAddressGenerationLogic(PAGENDataAddressGenerationLogic(PAGEN

MemoryandExternalInterfacePeripheralInterface

XDA

B

Signctr

Signctr

TDAA

BCDAB0MUX

Adder(40

MUX

AMUB

ALU(40

SignctrSignctr

TABC

D

S

A

BMUX

BACDSignctr

S

Legend:

AAccumulatorA

BAccumulatorB

CCBDataBus

DDBDataBus

EEBDataBusMMACUnit

PPBProgramBusSBarrelShifterTTRegisterUALU

E

图2-2TMS320C54x的功能框图

Buffered

SerialPort(BSP

TimerTDMSerialPort

StandardSerialPortHostPort

Interface(HPI16/8Multi-channelBuffereSerialPort(McBSP

PLLClockGeneratorS/WWaitstateGenerator

PowerManagement

JATGEmulationControlProgramData/RAM

ProgramData/ROM

PeripheralBus

DMA

Ch0Ch1Ch2Ch3Ch4Ch5

C54xDSPCPU

40bitALUCMPSOperator(VITERBIEXPEncoderALU

17*17MPY

40bitAdderRND,SATMAC40bitACCAAccumulators

(-16,31

Shifter

40bitACCB

40bitBarrel8AuxiliaryRegisterAddressingUnit

2AddessingUnitsD(15~0A(22~0

TMS320C54x是16位定点DSP。

TMS320C54x的中央处理单元(CPU具有改进的哈佛结构、低功耗设计和高度并行性等特点。

除此之外,高度专业化的指令系统可以全面地发挥系统性能。

使用TMS320C54x的专用硬件逻辑的CPU,再配以按照用户需要所选择的片内存储器和片内外设,可组成用户的ASIC(ApplicationSpecificIntergratedCircuit,专用集成电路以应用于电子产品的不同领域。

2.1.2TMS320C54xDSP的主要特点

TMS320C54x系列定点DSP芯片共享同样的CPU内核和总线结构,但每一种器件片内存储器的配置和片内外设不尽相同。

表2-1提供了TMS320C54x各DSP基本性能的概要。

表2-1TMS320C54x系列基本配置汇总表

TMS320C54x的主要特征如下:

(1CPU(中央处理单元利用其专用的硬件逻辑和高度并行性提高芯片的处理性能。

●1条程序总线、3条数据总线和4条地址总线组成的改进型哈佛结构,提供了更快的速度和更高的灵活性。

●40bit的算术逻辑单元(ALU包括40bit的桶形移位器和两个独立的40bit累加器A、B。

●17×17bit并行乘法单元和专用的40bit加法器用于无等待状态的单周期乘/累加操作。

●比较、选择和存储单元(CSSU能够完成维特比(Viterbi,通信中的一种编码方式的加/比较/选择操作。

●指数译码器可以在单周期内对40bit累加器进行指数运算。

●两个地址发生器包括8个辅助寄存器(AR0~AR7和两个辅助寄存器算术运算单元(ARAU0、ARAU1。

●TMS320C5420还包括一个双CPU的结构。

(2存储器具有192K字可寻址存储空间(包括64K字程序存储空间、64K字数据存储空间和64K字I/O空间。

其中,TMS320C548、TMS320C549、

TMS320C5402、TMS320C5410和TMS320C5420的程序存储空间还可以扩展到8M字。

片内存储器配置因型而异。

(3高度专业化的指令集能够快速地实现算法并用于高级语言编程优化。

其包括:

●单指令重复和块指令重复。

●用于更好地管理程序存储器和数据存储器的块移动指令。

●32位长整数操作指令。

●指令同时读取2或3个操作数。

●并行存储和加载的算术指令。

●条件存储指令。

●快速中断返回。

(4片内外设和专用电路采用模块化的结构设计,可以快速地推出新的系列产品。

其包括:

●可编程软件等待状态发生器。

●可编程分区转换逻辑电路。

●可使用内部振荡源或外部振荡源的锁相环(PLL时钟发生器。

当使用外部振荡源时,内部允许使用多个值对芯片倍频。

●外部总线接口可以禁止或允许外部数据总线、地址总线和控制线的输出。

●数据总线支持总线挂起的特征。

●可编程定时器。

●8bit并行主机接口(HPI。

●串行口:

全双工串口(支持8bit或16bit数据传送、时分多路(TDM串口和缓冲(BSP串口。

(5TMS320C54x执行单周期定点指令时间为

25/20/15/12.5/10ns,每秒指令数为40/66/100MIPS。

(6TMS320C54x电源由IDLE1、IDLE2和IDLE3功耗下降指令控制功耗,以便DSP工作在节电模式下,使之更适合于手机。

其控制CLKOUT引脚的输出,省功耗。

(7在片仿真接口、片上的JTAG接口符合

IEEE1149.1边界扫描逻辑接口标准,可与主机连接,用于芯片的仿真和测试。

2.2TMS320C54x的总线结构

TMS320C54xDSP片内由8组16bit总线(1组程序总线、3组数据线和4组地址总线构成。

程序总线(PB传送从程序存储器装载的指令代码和立即数。

这些总线的功能分别是:

3组数据总线(CB、DB和EB负责将片内的各种元器件相互连接,例如CPU、数据地址产生逻辑、程序地址产生逻辑、片内外设和数据存储器等。

TMS320C54x能利用两个辅助寄存器算术单元(ARAU0和ARAU1在同一个周期内生成两个数据存储器地址。

PB能加载保存于程序空间的操作数(例如,系数表,并将操作数传送到乘法器和加法器中进行乘累加操作,或利用数据移动指令(MVPD和READA把程序空间的数据传送到数据空间。

TMS320C54x还有一组双向的片内总线用于访问片内外设,这组总线轮流使用DB和EB与CPU连接。

访问者使用这组总线进行读/写操作需要两个或更多的周期,具体所需周期数取决于片内外设的结构。

表格2-2总结了各种不同类型的总线访问。

表2-2总线访问类型

2.3TMS320C54x的CPU结构

CPU是DSP芯片中的核心部分,是用来实现数字信号处理运算和高速控制功能的部件。

CPU内的硬件构成决定了其指令系统的性能。

TMS320C54x的CPU包括:

●40位算术逻辑单元(ALU;

●两个40位的累加器A、B;

●桶型移位寄存器(BarrelShifter;

●乘法器/加法器单元(Multiplier/Adder;

●比较、选择和存储单元(CSSU;

●指数编码器(EXPEncoder;

●CPU状态和控制寄存器(ST0、ST1和PMST;

●寻址单元(AddressingUnit。

2.3.1算术逻辑运算单元

使用算术逻辑单元(ALU和两个累加器(A、B能够完成二进制的补码运算,同时,ALU还能够完成布尔运算。

算术逻辑单元的输入操作数可以来自:

●16位的立即数;

●数据存储器中的16位字;

●暂存器T中的16位字;

●数据存储器中读出的2个16位字;

●累加器A或B中的40位数;

●移位寄存器的输出。

2.3.2累加器

累加器A和B可作为ALU和乘法器/加法器单元的目的寄存器,累加器也能输出数据到ALU或乘法器/加法器中。

累加器可分为三部分:

保护位、高位字和低位字。

累加器A和B的示意图如图2-3和图2-4所示。

图2-3累加器A

AG

39

32AH3116AL150

保护位高位字低位字

图2-4累加器B

BG

39

32BH3116BL150

保护位高位字低位字

保护位用于保存计算时产生的多余高位,防止在迭代运算中产生溢出,例如自相关运算。

AG、AH、AL、BG、BH和BL都是存储器映像寄存器(在存储空间中占有地址,由特定的指令将其内容放到16位数据存储器中,并从数据存储器中读出或写入32位累加器值。

2.3.3桶形移位器

桶形移位器能把输入的数据进行0~31位的左移和0~15位的右移。

40位桶形移位器的输入来自数据总线DB的16位输入数据、DB和CB的32位输入数据及任意一个40位累加器,并输出到ALU,经过MSW/LSW(最高有效字/最低有效字写选择单元至EB总线。

它所移的位数就是指令中的移位数。

移位数都是用二进制补码表示,正值表示左移,负值表示右移。

移位数可由立即数、状态寄存器ST1中的累加器移位方式(ASM字段和被指定为移位数值寄存器的暂存器T来决定。

桶形移位器可以执行以下定标操作:

●在执行ALU操作前预定好一个数据存储器操作数或累加器内容;

●对累加器的值进行算术或逻辑移位;

●归一化累加器;

●在保存累加器到数据存储器之前定标累加器。

2.3.4乘累加器单元

TMS320C54xCPU的乘累加器单元能够在一个周期内完成一次17*17bit的乘法和一次40位的加法。

乘

法器和ALU并行工作可在一个单指令周期内完成一次乘累加(MAC运算。

该单元能够快速高效地完成如卷积、相关和滤波等运算。

乘法器/加法器单元由17×17bit的硬件乘法器、40位专用加法器、符号位控制逻辑、小数控制逻辑、0检测器、溢出/饱和逻辑和16位的暂

存器(T等部分组成,可支持有/无符号的整数、小数乘法运算,并可对结果进行舍入处理。

乘累加器单元的一个输入操作数来自T寄存器、数据存储器或累加器A(31~16位;另一个则来自于程序存储器、数据存储器、累加器A(31~16位或立即数。

乘法器的输出加到加法器的输入端,累加器A或B则是加法器的另一个输入端,最后结果送往目的累加器A或B。

2.3.5比较选择存储单元

通信领域常常用到维持比(Viterbi算法,该算法需要完成大量的加法/比较/选择(ACS运算。

CSSU单元支持各种Viterbi算法,其中加法由ALU单元完成,只要将ST1中的C16置1,所有的双字指令都会变成双16位算术运算指令,这样ALU就可以在一个机器周期内完成两个16位数的加/减法运算,其结果分别存放在累加器的高16位和低16位中。

CSSU可以最大限度地完成累加器高字与低字的比较操作,即选择累加器中较大的字,并存储在数据存储器中,且不改变状态寄存器ST0中的测试/控制位TC字段和状态转移寄存器TRN的值。

CSSU利用优化的片内硬件加速Viterbi的蝶形运算。

2.3.6指数编码器

指数编码器是一个专用硬件,它支持单周期指令EXP。

它可以求出累加器中的指数值,并以二进制补码形式存放于T中。

用EXP和NORM指令可以对累加器中的内容归一化,完成定点数和浮点数之间的转换。

2.3.7CPU状态控制寄存器

1.状态寄存器(ST0和ST1

使用置位指令SSBX和复位指令RSBX可以单独设置和清除状态寄存器的各位。

例如:

SSBXSXM;符号扩展SXM=1

RSBXSXM;禁止符号扩展SXM=0

APR、DP和ASM字段可以通过LD指令装载一个短立即数,ASM和DP也可以通过LD指令由数据存储器装载。

ST0的结构如图2-5所示,含义见表2-3。

图2-5ST0寄存器结构

ARPTCCOVAOVB

DP15

131********

表2-3ST0寄存器

图2-6ST1寄存器结构BRAF15CPL14XF13HM12INTM11010OVM9SXM8C167FRCT6CMPT5ASM

40

表2-4ST1寄存器

2.处理器工作方式状态寄存器(PMST

PMST可由存储器映像寄存器指令装载,如STM。

图2-7是PMST寄存器的结构图。

PMST各位的含义列于表2-5中。

图2-7PMST寄存器结构

IPTR15

7MP/MC6OVLY5AVIS4DROM3CLKOFF2SMUL+1SST+0注:

+表示仅LP器件有此位,其他器件为保留位。

表2-5PMST寄存器

2.3.8寻址单元

TMS320C54x有两个地址发生器:

PAGEN(ProgramAddressGenerationLogic和DAGEN(DataAddressGenerationLogic。

PAGEN包括程序计数器PC、IPTR、块循环寄存器(RC、BRC、RSA和REA,这些寄存器可支持程序存储器寻址。

DAGEN包括循环缓冲区大小寄存器BK、DP、堆栈指针寄存器SP、8个辅助寄存器(AR0~AR7和2个辅助寄存器算术单元(ARAU0和ARAU1。

8个辅助寄存器和2个辅助寄存器算术单元一道可进行16位无符号数算术运算,支持间接寻址模块,AR0~AR7由ST0中的ARP来指定。

2.4TMS320C54x存储器和I/O空间

DSP扩展存储器主要分为两类:

ROM和RAM。

ROM包括EPROM、EEPROM、FlashMemroy等。

这一类存储器主要用于存储用户程序和系统常数表,一般映像在程序存储空间。

RAM主要指静态RAM(SRAM。

本章主要讨论片内存储器,而片外扩展存储器将在第8章中详细介绍。

所有TMS320C54x芯片内都包含随机存储器(RAM和只读存储器(ROM。

在芯片中有两类RAM:

双寻址RAM(DARAM和单寻址RAM(SARAM,分别也可称为双口RAM和单口RAM。

DARAM每个机器周期可被访问两次。

TMS320C54x因具体器件不同,片内存储器的类型或容量也有些差异。

表2-6列出了几种常用的TMS320C54x器件的存储器容量。

TMS320C54x有26个CPU寄存器和片内外设寄存器被映像在数据存储空间,各类TMS320C54x存储器的特征及组织和使用不同的片内存储器块将在下面详细介绍。

表2-6TMS320C54x内部存储器容量

2.4.1存储器空间

TMS320C54x采用改进的哈佛结构。

存储空间由三个独立可选的存储空间组成,这三个独立可选的存储空间包括64K字的程序存储空间、64K字的数据存储空间和64K字的I/O空间。

片内或片外的ROM和RAM、外部的EPROM和EEPROM以及芯片中的存储器映像寄存器包括在这三个空间中。

在TMS320C54x中,片内存储器有DARAM、SARAM和ROM三种类型。

它们通常配置在数据存储空间,但也可以配置在程序存储空间。

片内ROM则一般配置在程序存储空间,但一部分ROM也可以配置到数据存储空间中。

TMS320C54x的工作方式状态寄存器PMST提供了三个控制位:

MP/、OVLY和DROM,用于在存储空间中配置片内存储器。

使用这三个控制位可以设置片内存储器是否配置到存储空间,并指定片内存储器是配置到程序存储空间还是数据存储空间。

●MP/

:

微处理器/微型计算机工作方式位。

当MP/=0

时,允许片内ROM配置到程序存储空间;当MP/=1时,禁止片内ROM配置到程序存储空间。

●OVLY:

RAM重叠位。

当OVLY=1时,片内ROM配置到程序和数据存储空间;当OVLY=0时,片内RAM仅配置到数据存储空间。

●DROM:

数据ROM位。

当DROM=1时,片内ROM配置到程序和数据存储空间。

当DROM=0时,禁止ROM配置到数据存储空间。

DROM的用法与MP/的状态无关。

MCMCMCMC

图2-8~图2-12是TMS320C54x芯片数据和程序存储空间的配置图,从中也可以看到上述三个控制位与内存储器的关系。

图2-8TMS320C541存储器图

保留(OVLY=1

或

外部(OVLY=0

片内DARAM(OVLY=1

或

外部DARAM(OVLY=0

外部

中断字及保留

(外部

程序存储器0000H

MP/MC=1微处理器模式

007FH0080H

13FFH1400HFF7FH

FF80HFFFFH

保留(OVLY=1

或

外部(OVLY=0

片内DARAM(OVLY=1

或

外部DARAM(OVLY=0

外部

中断字及保留

(片内

片内ROM(28K字

程序存储器

0000H

007FH0080H

13FFH1400HFF7FH

FF80HFFFFH

8FFFH9000HMP/MC=0微型计算机模式

存储器映像寄存器片内DARAM(5K字

外部

保留(DROM=1或

外部(DROM=0

片内ROM(DROM=1

或

外部ROM

(DROM=0数据存储器0000H007FH0080H13FFH1400HFEFFHFF00HFFFFH

DFFFHE000H

暂存器SPRAM005FH0060H