蔡觉平老师西电Verilog HDL上机大作业硬件描述语言微电子学院.docx

《蔡觉平老师西电Verilog HDL上机大作业硬件描述语言微电子学院.docx》由会员分享,可在线阅读,更多相关《蔡觉平老师西电Verilog HDL上机大作业硬件描述语言微电子学院.docx(20页珍藏版)》请在冰豆网上搜索。

蔡觉平老师西电VerilogHDL上机大作业硬件描述语言微电子学院

《VerilogHDL数字集成电路设计原理与应用》上机作业

班级:

*******

学号:

*******

姓名:

*******

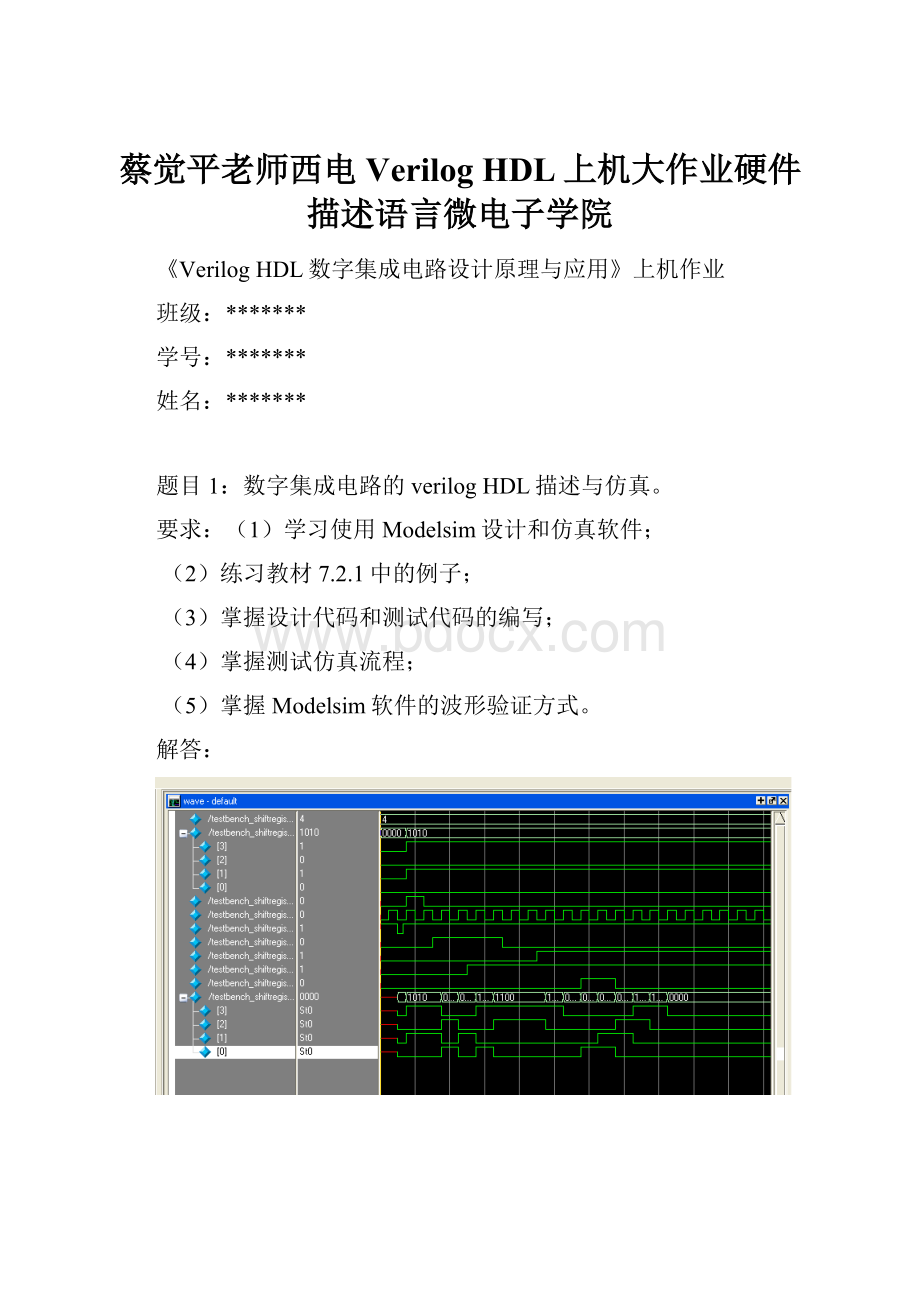

题目1:

数字集成电路的verilogHDL描述与仿真。

要求:

(1)学习使用Modelsim设计和仿真软件;

(2)练习教材7.2.1中的例子;

(3)掌握设计代码和测试代码的编写;

(4)掌握测试仿真流程;

(5)掌握Modelsim软件的波形验证方式。

解答:

题目2:

简述begin-end语句块和fork-join语句块的区别,并写出下面信号对应的程序代码

解答:

(1)begin-end语句块和fork-join语句块的区别:

1、执行顺序:

begin-end语句块按照语句顺序执行,fork-join语句块所有语句均在同一时刻执行;

2、语句前面延迟时间的意义:

begin-end语句块为相对于前一条语句执行结束的时间,fork-join语句块为相对于并行语句块启动的时间;

3、起始时间:

begin-end语句块为首句开始执行的时间,fork-join语句块为转入并行语句块的时间;

4、结束时间:

begin-end语句块为最后一条语句执行结束的时间,fork-join语句块为执行时间最长的那条语句执行结束的时间;

5、行为描述的意义:

begin-end语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join语句块为电路上电后,各电路模块同时开始工作的过程。

(2)程序代码:

Begin-end语句:

moduleinitial_tb1;

regA,B;

initial

begin

A=0;B=1;

#10A=1;B=0;

#10B=1;

#10A=0;

#10B=0;

#10A=1;B=1;

end

endmodule

Frk-join语句:

modulewave_tb2;

regA,B;

parameterT=10;

initial

fork

A=0;B=1;

#TA=1;B=0;

#(2*T)B=1;

#(3*T)A=0;

#(4*T)B=0;

#(5*T)A=1;B=1;

join

endmodule

题目3.分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

解答:

(1)阻塞赋值语句

moduleblock2(din,clk,out0,out1,out2,out3);

inputdin,clk;

outputout0,out1,out2,out3;

regout0,out1,out2,out3;

always@(posedgeclk)

begin

out0=din;

out1=out0;

out2=out1;

out3=out2;

end

endmodule

(2)非阻塞赋值语句

modulenon_block1(din,clk,out0,out1,out2,out3);

inputdin,clk;

outputout0,out1,out2,out3;

regout0,out1,out2,out3;

always@(posedgeclk)

begin

out0<=din;

out1<=out0;

out2<=out1;

out3<=out2;

end

endmodule

题目4:

设计16位同步计数器

要求:

(1)分析16位同步计数器结构和电路特点;

(2)用硬件描述语言进行设计;

(3)编写测试仿真并进行仿真。

解答:

(1)电路特点:

同步计数器的时间信号是同步的;每当到达最高计数后就会重新计数。

(2)程序代码:

modulecomp_16(count,clk,rst);

output[15:

0]count;

inputclk,rst;

reg[15:

0]count;

always@(posedgeclk)

if(rst)count<=16'b0000000000000000;

else

if(count==16'b1111111111111111)

count<=16'b0000000000000000;

else

count<=count+1;

endmodule

(3)仿真代码:

modulecomp_16_tb;

wire[15:

0]count;

regclk,rst;

comp_16U1(count,clk,rst);

always#1clk=~clk;

initial

begin

clk=0;rst=0;

#1rst=1;

#10rst=0;

#10rst=1;

#10rst=0;

#99999$finish;

end

endmodule

题目5.试用VerilogHDL门级描述方式描述如下图所示的电路。

解答:

modulezy(D0,D1,D2,D3,S1,S2,T0,T1,T2,T3,Z);

outputZ;

inputD0,D1,D2,D3,S1,S2;

wireT0,T1,T2,T3,wire1,wire2;

notU1(wire1,S1),

U2(wire2,S2);

andU3(T0,D0,wire2,wire1),

U4(T1,D1,S1,wire1),

U5(T2,D2,S1,wire2),

U6(T3,D3,S1,S2);

orU7(Z,T0,T1,T2,T3,);

endmodule

题目6.试用查找真值表的方式实现真值表中的加法器,写出VerilogHDL代码:

Cin

ain

bin

sum

Cout

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

解答:

modulehomework6(SUM,COUT,A,B,CIN);

outputSUM,COUT;

inputA,B,CIN;

regSUM,COUT;

always@(AorBorCIN)

case({A,B,CIN})

3'b000:

SUM<=0;

3'b000:

COUT<=0;

3'b001:

SUM<=1;

3'b001:

COUT<=0;

3'b010:

SUM<=1;

3'b010:

COUT<=0;

3'b011:

SUM<=0;

3'b011:

COUT<=1;

3'b100:

SUM<=1;

3'b100:

COUT<=0;

3'b101:

SUM<=0;

3'b101:

COUT<=1;

3'b110:

SUM<=0;

3'b110:

COUT<=1;

3'b111:

SUM<=1;

3'b111:

COUT<=1;

endcase

endmodule

题目7:

设计16位同步加法器和乘法器

要求:

(1)分析16位同步加法器和乘法器结构和电路特点;

(2)用硬件描述语言进行设计;

(3)编写测试仿真并进行仿真。

解答:

(1)16位同步加法器和乘法器结构和电路特点:

加法器的进位只用考虑一位,但是乘法器的进位要考虑到32位才行。

(2)程序代码:

16位同步加法器:

moduleadder(a,b,c,sum,cout);

output[15:

0]sum;

outputcout;

input[15:

0]a,b;

inputc;

assign{cout,sum}=a+b+c;

endmodule

16位同步乘法器:

modulemultiplier(a,b,mul);

input[15:

0]a,b;

output[31:

0]mul;

assignmul=a*b;

endmodule

(3)仿真代码:

16位同步加法器:

moduleadder_tb;

reg[15:

0]a,b;

regc;

wire[15:

0]sum;

wirecout;

initial

begin

a=8;b=8;c=1;

end

initial

begin

#10a=16'b1111111111111111;#10b=1;

end

adderU2(.a(a),.b(b),.c(c),.cout(cout),.sum(sum));

endmodule

16位同步乘法器:

modulemultiplier_tb;

reg[15:

0]a,b;

wire[31:

0]mul;

initial

begin

a=3;b=8;

end

initial

begin

#10a=100;

#15b=100;

end

multiplierU1(.a(a),.b(b),.mul(mul));

endmodule

仿真截图:

加法器:

乘法器:

题目8.将下面的状态转移图用VerilogHDL描述。

在图中,状态机的输入只与状态的跳转有关,与状态机的输出无关,因此该状态机为摩尔型状态机。

下面为三段式描述方式。

解答:

程序代码:

modulehomework8(clk,out,step,clr);

output[2:

0]out;

inputstep,clk,clr;

reg[2:

0]out;

reg[1:

0]state,next_state;

always@(posedgeclk)

state<=next_state;

always@(stateorclr)

if(clr)

next_state<=0;

else

case(state)

2'b00:

case(step)

1'b0:

beginnext_state<=2'b00;out<=3'b001;end

1'b1:

beginnext_state<=2'b01;out<=3'b001;end

endcase

2'b01:

begin

out<=3'b010;

next_state<=2'b10;

end

2'b10:

case(step)

1'b0:

beginnext_state<=2'b00;out<=3'b100;end

1'b1:

beginnext_state<=2'b11;out<=3'b100;end

endcase

2'b11:

case(step)

1'b0:

beginnext_state<=2'b11;out<=3'b111;end

1'b1:

beginnext_state<=2'b00;out<=3'b111;end

endcase

endcase

endmodule

仿真代码:

modulehomework8_tb;

regclk,step,clr;

wire[3:

0]out;

always

#5clk=~clk;

initial

beginclk=0;

clr=1;

step=1;

end

initial

begin

#5clr=0;

#10step=0;

#10step=1;

end

homework8U1(clk,out,step,clr);

endmodule

仿真截图:

题目9.如下图所示电路,若其延迟时间设定如表所示,试写VerilogHDL程序设计该电路。

路径

最小值(min)

典型值(type)

最大值(max)

a_sa_y

10

12

14

s_s0_sa_y

15

17

19

s_sb_y

11

13

15

b_sb_y

10

12

14

解答:

程序代码:

modulea(a,s,b,y,s0);

inputa,b,s,s0;

outputy;

assigny=(s&&b)||(s0&&a);

specify

(a=>y)=(10,12,14);

(b=>y)=(10,12,14);

(s=>y)=(11,13,15);

(s0=>y)=(11,13,15);

endspecify

endmodule

moduleb(a,s,b,y);

inputs,a,s,b;

outputy;

wires0;

not#(4)U1(s0,s);

delay_doorU2(a,s,b,y,s0);

endmodule

题目10.设计一个8位数字显示的简易频率计。

要求:

①能够测试10Hz~10MHz方波信号;

②电路输入的基准时钟为1Hz,要求测量值以8421BCD码形式输出;

③系统有复位键;

④采用分层次分模块的方法,用VerilogHDL进行设计。

解答:

程序代码:

modulex;

regstandard_clk;

regtest_clk;

wire[7:

0]out;

regreset;

initialbeginreset=0;test_clk=0;standard_clk=0;end

initial#15reset=1;

always#1test_clk=~test_clk;

always#10standard_clk=~standard_clk;

aU1(.reset(reset),.test_clk(test_clk),.standard_clk(standard_clk),.ratio_final(out));

endmodule

modulea(reset,test_clk,standard_clk,ratio_final);

inputreset,test_clk,standard_clk;

output[7:

0]ratio_final;

wiremul_clk;

wirereset_comp;

wire[7:

0]ratio_start;

andU0(reset_comp,reset,standard_clk);

tU1(.ain(test_clk),.din(standard_clk),.mul(mul_clk));

wU2(.clk(mul_clk),.count(ratio_start),.reset(reset_comp));

cU3(.ratio_start(ratio_start),.ratio_final(ratio_final));

endmodule

modulew(clk,count,reset);

inputclk,reset;

outputcount;

parameterbit=8;

reg[bit-1:

0]count;

always@(posedgeclkornegedgereset)

if(!

reset)

count<=8'b00000000;

else

count<=count+1;

endmodule

modulet(ain,din,mul);

parameterwidth=1;

input[width-1:

0]ain,din;

output[width*2-1:

0]mul;

assignmul=ain*din;

endmodule

modulec(ratio_start,ratio_final);

input[7:

0]ratio_start;

output[7:

0]ratio_final;

assignratio_final=2*ratio_start;

endmodule

题目11.用VerilogHDL设计一个4位LED显示器的动态扫描译码电路。

要求:

①4个七段显示器共用一个译码驱动电路;

②显示的数码管清晰明亮,无闪烁现象发生。

解答:

modulea(out,in);

outputout;

inputin;

reg[6:

0]out;

wire[3:

0]in;

always@(in)

begin

case(in)

4'd0:

out=7'b1111110;

4'd1:

out=7'b0110000;

4'd2:

out=7'b1101101;

4'd3:

out=7'b1111001;

4'd4:

out=7'b0110011;

4'd5:

out=7'b1011011;

4'd6:

out=7'b1011111;

4'd7:

out=7'b1110000;

4'd8:

out=7'b1111111;

4'd9:

out=7'b1111011;

endcase

end

endmodule

modulew(in1,in2,in3,in4,out1,out2,out3,out4);

outputout1,out2,out3,out4;

inputin1,in2,in3,in4;

wire[3:

0]in1,in2,in3,in4;

wire[6:

0]out1,out2,out3,out4;

aU1(.in(in1),.out(out1));

aU2(.in(in2),.out(out2));

aU3(.in(in3),.out(out3));

aU4(.in(in4),.out(out4));

endmodule

modulec;

reg[3:

0]in1,in2,in3,in4;

wire[6:

0]out1,out2,out3,out4;

initial

begin

in1=4'b0010;

in2=4'b0100;

in3=4'b1000;

in4=4'b0000;

end

initial

begin

#5in4=4'b0111;

in3=4'b0110;

in2=4'b0100;

in1=4'b0000;

end

wU1(in1,in2,in3,in4,out1,out2,out3,out4);

endmodule