SOC课程设计山东大学.docx

《SOC课程设计山东大学.docx》由会员分享,可在线阅读,更多相关《SOC课程设计山东大学.docx(54页珍藏版)》请在冰豆网上搜索。

SOC课程设计山东大学

《SOC设计方法与实现》课程设计

一、实验负责人:

二、实验时间:

2012.11.20—2012.12.14

三、设计说明:

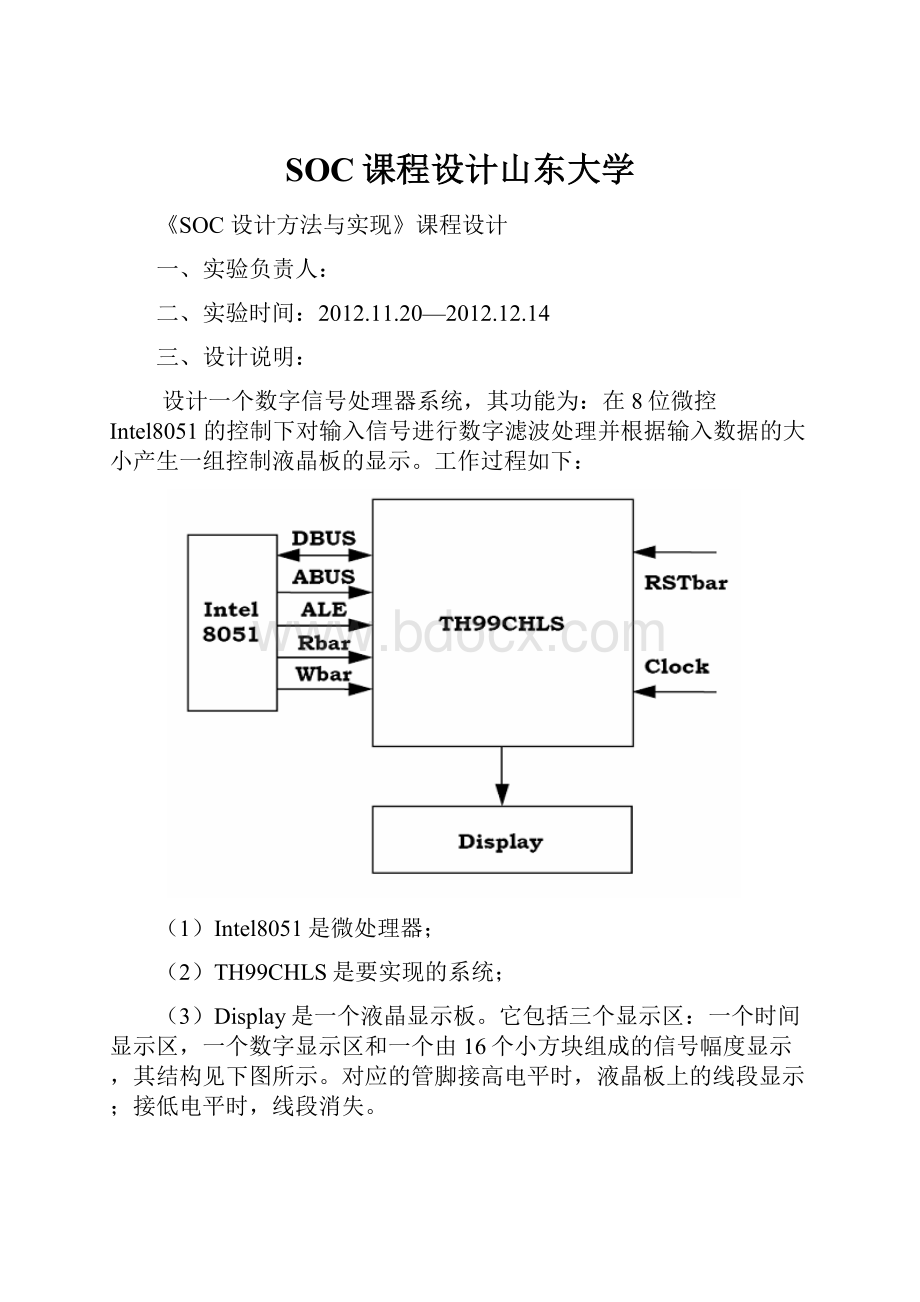

设计一个数字信号处理器系统,其功能为:

在8位微控Intel8051的控制下对输入信号进行数字滤波处理并根据输入数据的大小产生一组控制液晶板的显示。

工作过程如下:

(1)Intel8051是微处理器;

(2)TH99CHLS是要实现的系统;

(3)Display是一个液晶显示板。

它包括三个显示区:

一个时间显示区,一个数字显示区和一个由16个小方块组成的信号幅度显示,其结构见下图所示。

对应的管脚接高电平时,液晶板上的线段显示;接低电平时,线段消失。

四、实验目的:

完成一个数字系统的VerilogHDL描述和利用EDA工具的VerilogHDL仿真综合环境对这一描述进行仿真并综合,完整地从事一个数字VLSI系统的设计过程,理解和掌握现代集成电路的设计流程、硬件描述语言综合理论等高层次设计方法以及它和物理实现之间的关系,巩固在理论课阶段学习的相关知识。

5、实验设备:

代码输入工具:

QuartusII

功能仿真:

ModelSimSE6.2b

综合工具:

DC,SynplifyPro8.6.2

6、系统简介:

1、工作过程

(1)在外部信号PEbar的控制下,芯片从端口in读入一个八位数据。

(2)在

(1)中输入的数据与微处理器给出的另一个八位数据进行按位“与”操作。

(3)在

(2)中处理过的数据经数字滤波后从端口out输出。

(4)TH99CHLS内部产生一组时间信号,包括时和分,其格式为:

(hh:

mm)。

这组时间信号的初值由微处理器给出,微处理器可以随时对时间信号进行修改。

(5)送往液晶显示板的信号有三组:

a.(4)中产生的时间信号,经七段译码后从端口hour和minute送出;

b.(3)中经数字滤波的信号,在转换成十进制并做七段译码后,百位经端口d00,十位经端口d10,个位经端口d01送出;

c.(3)中经数字波的信号,在经过

压缩后通过端口ap送出。

2、数字滤波器

数字滤波器的转移函数为:

滤波器的系数B0,B1,...,B6均由微处理器给出。

微处理器可以根据需要修改这些系数。

3、模块说明

根据功能分析,将整个系统分为8个模块。

各个模块对应的源文件和功能描述如下表所示。

模块名称

对应源文件

功能说明

decoder

decoder.v

将四位二进制译码为LED显示。

输入4bit,输出为7bit直接驱动显示装置,为组合逻辑。

H2D

H2D.v

进行16进制到十进制的转换。

输入为8bit无符号数,输出为百,十,个位数字(其中每个数字4bit位宽),同样为组合逻辑

decoder_4X16

decoder_4X16

4-16译码器,主要是将经过y=sqrt(x)压缩后的数据送至显示设备。

输入4bit,输出16bit,组合逻辑。

sqrt_lut

sqrt_lut.v

主要实现y=sqrt(x)的运算。

主要是通过比较和查找表方式实现。

输入8bit,输出4bit。

时序逻辑,一个时钟周期。

mul8b_shiftadd_fsm

mul8b_shiftadd_fsm.v

乘法器设计。

通过移位加的方式实现。

内部通过状态机实现。

完成一次乘法需要8个时钟周期

timer_clk

timer_clk.v

时间时钟模块,主要是根据系统时钟计算秒。

通过计数器级联的方式实现。

filter

filter.v

这是整个系统比较核心的部分。

主要实现滤波器的设计和与微处理器的接口时序设计。

接口需要三态控制,并且要注意读写信号的控制,滤波器采用并行设计,用面积换取速度。

TH99CHLS

TH99CHLS.v

顶层元件例化。

主要是将上述各个模块进行组合。

整个功能框图如下:

七、行为描述及仿真结果

下面是测试用的模块介绍,模拟TH99CHLS外围的单片机、控制信号和数据输入等:

模块名称

对应的源文件

功能说明

osc_rst

osc_rst.v

产生时钟频率和复位信号

fir_tb

fir_tb.v

滤波器数据的输入

wr_rd

wr_rd.v

单片机WR,RD信号的模拟

mcu

mcu.v

主要是模拟单片机对TH99CHLS芯片的控制,包括寄存器的读入与读出等一系列操作

top_test

top_test.v

顶层测试文件,主要是进行元件例化

ModelSimSE功能仿真结果波形图如下:

第一张图为前0-7us,第二张图为7us-15us.详细图形见source中的1.bmp和2.bmp.也可以查看其下的vsim.wlf(需要安装modelsim)。

此图为对TH99CHLS芯片内部b0-b6(滤波器系数)寄存器的操作和对mini,hour寄存器初始化的操作仿真结果。

八、综合结果及分析

Synplify综合结果如下:

DC综合结果如下:

九、所占用的资源和数据通道分析

该系统所占用的资源如下:

在滤波器设计中,并没有采用乘法器的复用,而是采用了多个乘法器的复制,牺牲面积来换取速读的提高。

综合后的频率能够达到50MHz。

滤波器的数据通道如下:

(用多个乘法器)

10、RTL级设计

RTL级设计的基本部件是寄存器、计数器、多路复用器和算术逻辑单元(ALU),通常采用真值表和状态表来表示,其描述多采用数据流描述方式,行为级设计中,通过定义I/O响应的方式描述硬件,很少考虑硬件的具体实现,仅仅是一些写就的程序或者过程,用于模拟器件行为,建立算法模型,由于没有考虑具体物理实现,通常综合效果不好。

RTL级设计中,数据的相关性与硬件的物理实现是一致的,存在直接的映射关系,其描述说明的是数据在寄存器间的实际移动与寄存器级实现。

基于物理实现的考虑,因此RTL描述是有着许多限制的。

使用verilog语言描述的风格对设计有很大的影响。

就逻辑综合而言,重要的是考虑实际的硬件实现问题:

在不牺牲高抽象层次和控制逻辑综合输出结构之间要进行折中。

在之前的行为级设计时,设计者编码风格偏向于RTL级描述,因此需要对个别语句进行修改即可,具体verilog代码见报告Appendix部分。

在本设计中,采用台积电0.13um工艺库tcb013ghp,综合库采用dw_foundation.sldb由于设计规模的原因,约束文件中设置约束较宽松,且不加线负载,根据设计要求及以上设计考虑,编写.synopsys_dc.setup文件和top.con约束文件进行综合设计。

得出所设计系统的门级网表,并分析系统的功耗,面积,时序等信息。

十一、控制状态及化简

由滤波器公式可知采用通常的调配方法,用四个步长来实现。

如图所示:

这样的方法虽然可行,但资源的使用太大,需要7个乘法器和3个加法器,同时逻辑综合后也会消耗很大的面积和功耗,为了提高资源的利用效率,我们需要对数据通路和控制器重新设计,尽量减少资源数量,同时在速度和代价上做出相应的优化。

由于公式中的描述乘法器过多而牺牲了很大的代价,在设计中,先以减少乘法器为目的,

但如果只采用一个乘法器,控制步又变得相对冗长,所以,在这个实验中,采用6个时钟步

长,根据“基于距离”的资源调配方法,实现算子的调度与资源的调配,同时,对寄存器也

进行了优化,使得其采用更少的寄存器。

资源分配的优化如下图所示:

上图采用6个步长,资源包括:

乘法器M1、M2,加法器A1、A2,寄存器:

r1、r2、r3、r4。

当然使用6个步长较上一种方案可能速度上有所牺牲,但带来了寄存器代价和资源代价的很大改善。

十二、门数和结果分析

综合之后生成系统芯片如下图所示,给出了芯片的I/O引脚。

综合生成的门级网表如下图所示:

在命令行中输入design_vision>sizeof_collection[get_cells–hierarchical*],可以得到

系统的cell数目,报告如下所示:

由于库里不包含详细的每个门的晶体管电路,系统只能报告cell的个数,为224,

根据cell估算系统的门数,大致在1000门左右。

在命令行中输入report_area,可以得到系统的面积,最后得到的芯片总面积为

2137.026628,报告如下所示:

在命令行中输入report_power,可以得到系统的功耗,由于各个引脚的高低电平不

确定,系统默认库里的电压值进行计算,设定V=1V,总功耗为9.1080uW,报告如下所

示:

加激励文件对设计进行仿真验证得到的系统总波形图如下图所示:

仿真验证结果与行为级仿真验证结果基本相似,可知本设计及综合基本完成了本

系统的功能要求、时序要求。

综上所述,本设计系统基本完成了设计要求(功能、时序),系统包含224个单元,

约1000门,芯片总面积为2137.026628,总功耗约为9.1080uW。

在集成电路设计中,对系统电路进行设计描述时虽然使用编程语言进行设计,但要始终从硬件电路结构及其实现方面考虑,这样才能使系统设计无论从可行性还是有效性等方面都能得到保证。

比如设计者在设计时曾遇到这样一个设计错误:

case语句default,使用行为级描述时可以让其执行空操作或者延时,可是从硬件角度这是不具有意义的。

这是设计时的一个小例子,许多设计问题的出现都是由于设计者过少地甚至漠视硬件电路结构造成的。

其次,集成电路设计中验证是重点。

随着设计规模的日益增大,验证工作的重要性越来越突出,难度挑战也日趋加大,验证工作在总设计工作的比例初步上升。

不可忽视验证的重要性,优化算法思路使验证语句覆盖率、状态覆盖率、转移覆盖率等方面提高,使验证工作尽可能趋于完备,对于设计成功具有极为重要的意义。

十三、VerilogHDL代码

///////////////////////////////////////////////////////////////////////////////////

`timescale1ns/10ps

moduletop_test();

wireclk,rst_n;

wire[7:

0]abus;

wireale,rbar_n,wbar_n,cs_n;

wirepebar_n;

wire[7:

0]fir_in;

wire[7:

0]dbus_xio;

wire[13:

0]hour,mini;

wire[20:

0]fir_out;

wire[15:

0]fir_out_sqrt;

wiresend_data_en;

fir_tbUfir_tb(send_data_en,pebar_n,fir_in);

osc_rstUost_rst(clk,rst_n);

TH99CHLSUTH99(

dbus_xio,

abus,

rbar_n,

wbar_n,

ale,

pebar_n,

fir_in,

cs_n,

rst_n,

clk,

//outputports

fir_out,

fir_out_sqrt,

hour,

mini

);

mcuUmcu(

.dbus_xio(dbus_xio),

.abus(abus),

.rbar_n(rbar_n),

.wbar_n(wbar_n),

.ale(ale),

.cs_n(cs_n),

.send_data_en(send_data_en)

);

endmodule

//////////////////////////////////////////////////////////////////

moduledecoder(

//input

hex,

//output

led

);

input[3:

0]hex;

outputreg[6:

0]led;

always@(hex)begin

case(hex)

4'b0000:

led=7'b011_1111;//0

4'b0001:

led=7'b001_1000;//1

4'b0010:

led=7'b111_0110;//2

4'b0011:

led=7'b111_1100;//3

4'b0100:

led=7'b101_1001;//4

4'b0101:

led=7'b110_1101;//5

4'b0110:

led=7'b110_1111;//6

4'b0111:

led=7'b011_1000;//7

4'b1000:

led=7'b111_1111;//8

4'b1001:

led=7'b111_1101;//9

default:

led=7'b000_0000;//null

endcase

end

endmodule

////////////////////////////////////////////////////////////////////

moduleTH99CHLS(

//input

dbus_xio,

abus,

rbar_n,

wbar_n,

ale,

pebar_n,

fir_in,

cs_n,

rst_n,

clk,

//outputports

fir_out,

fir_out_sqrt,

hour,

mini

);

inputclk,rst_n;

input[7:

0]abus;

inputale,rbar_n,wbar_n,cs_n;

inputpebar_n;

input[7:

0]fir_in;

inout[7:

0]dbus_xio;

output[13:

0]hour,mini;

output[20:

0]fir_out;

output[15:

0]fir_out_sqrt;

wire[15:

0]fir_out_Hex;

wire[7:

0]hour_Hex,mini_Hex;

wire[3:

0]fir_sqt_Hex;

wire[3:

0]hud_Hex,ten_Hex,num_Hex;

filterUfilter(.dbus_xio(dbus_xio),.abus(abus),.rbar_n(rbar_n),

.wbar_n(wbar_n),.ale(ale),.pebar_n(pebar_n),

.fir_in(fir_in),.cs_n(cs_n),.rst_n(rst_n),.clk(clk),

.fir_out(fir_out_Hex),.hour(hour_Hex),.mini(mini_Hex));

sqrt_lutUsqt(.result(fir_sqt_Hex),.in(fir_out_Hex[7:

0]),.clk(clk),.rst_n(rst_n));

decoder_4X16Ude4X16(.out(fir_out_sqrt),.in(fir_sqt_Hex));

H2DUH2d1(.hex(fir_out_Hex[7:

0]),

.hud(hud_Hex),.ten(ten_Hex),.num(num_Hex));

decoderUdecoder1(.hex(hud_Hex),.led(fir_out[20:

14]));

decoderUdecoder2(.hex(ten_Hex),.led(fir_out[13:

7]));

decoderUdecoder3(.hex(num_Hex),.led(fir_out[6:

0]));

decoderUdecoder4(.hex(hour_Hex[7:

4]),.led(hour[13:

7]));

decoderUdecoder5(.hex(hour_Hex[3:

0]),.led(hour[6:

0]));

decoderUdecoder6(.hex(mini_Hex[7:

4]),.led(mini[13:

7]));

decoderUdecoder7(.hex(mini_Hex[3:

0]),.led(mini[6:

0]));

endmodule

//////////////////////////////////////////////////////////////////////

`timescale1ns/10ps

modulewr_rd(

dbus_xio,

abus,

rbar_n,

wbar_n,

ale);

parameterMCU_CLK=40;//25MHz

parameterLL_DELAY=15;

outputreg[7:

0]abus;

outputregale,rbar_n,wbar_n;

inout[7:

0]dbus_xio;

regctrl;

reg[7:

0]abus_low;

assigndbus_xio=ctrl?

abus_low:

8'hzz;//ifctrl=1outputthenhiz

integeri;

initialbegin

rbar_n=1'b1;

wbar_n=1'b1;

end

taskwrite_register;

input[7:

0]write_addr;

input[7:

0]write_data;

//writemovx

begin

ale=1'b0;//configb0

#MCU_CLK;

ale=1'b1;

ctrl=1'b1;

#LL_DELAY;

abus_low=write_addr;

abus=8'h0;

#LL_DELAY;

ale=0;

ctrl=1'b0;//float

#MCU_CLK;

#MCU_CLK;

ctrl=1'b1;

abus_low=write_data;

#1;

wbar_n=1'b0;

for(i=0;i<8;i=i+1)

#MCU_CLK;

wbar_n=1'b1;

end

endtask

//endmovx

taskread_register;

input[7:

0]read_addr;

output[7:

0]read_data;

//readmovx

begin

ale=1'b0;//configb0

#MCU_CLK;

ale=1'b1;

ctrl=1'b1;

#LL_DELAY;

abus_low=read_addr;

abus=8'h0;

#LL_DELAY;

ale=0;

ctrl=1'b0;//float

#MCU_CLK;

#MCU_CLK;

ctrl=1'b0;

rbar_n=1'b0;

#MCU_CLK;

read_data=dbus_xio;

for(i=0;i<7;i=i+1)

#MCU_CLK;

rbar_n=1'b1;

end

endtask

endmodule

/////////////////////////////////////////////////////////////////////

moduledecoder_4X16(

//output

out,//16bitwidthhighvoltageffect

//input

in//fourbitwidth

);

input[3:

0]in;

output[15:

0]out;

assignout[15]=in[3]&in[2]&in[1]&in[0];//111115

assignout[14]=in[3]&in[2]&in[1]&(~in[0]);//111014

assignout[13]=in[3]&in[2]&(~in[1])&in[0];//110113

assignout[12]=in[3]&in[2]&(~in[1])&(~in[0]);//110012

assignout[11]=in[3]&(~in[2])&in[1]&in[0];//101111

assignout[10]=in[3]&(~in[2])&in[1]&(~in[0]);//101010

assignout[9]=in[3]&(~in[2])&(~in[1])&in[0];//10019

assignout[8]=in[3]&(~in[2])&(~in[1])&(~in[0]);//10008

assignout[7]=(~in[3])&in[2]&in[1]&in[0];//01117

assignout[6]=(~in[3])&in[2]&in[1]&(~in[0]);//01106

assignout[5]=(~in[3])&in[2]&(~in[1])&in[0];//01015

assignout[4]=(~in[3])&in[2]&(~in[1])&(~in[0]);//01004

assignout[3]=(~in[3])&(~in[2])&in[1]&in[0];//00113

assignout[2]=(~in[3])&(~in[2])&in[1]&in[0];//00102

assignout[1]=(~in[3])&(~in[2])&(~in[1])&in[0];//00011

assignout[0]=(~in[3])&(~in[2])&(~in[1])&(~in[0]);//00000

endmodule

////////////////////////////////////////////////////////////////////

modulefilter(

//inputports

dbus_xio,

abus,

rbar_n,

wbar_n,

ale,

pebar_n,

fir_in,

cs_n,

rst_n,

clk,

//outputports

fir_out,

hour,

mini,

);

inoutwire[7:

0]dbus_xio;//databusconnecttop0complexofdataandaddr

//outputreg[7:

0]dbus;

input[7:

0]abus;//addrbusconnecttop2

inputrbar_n,wbar_n;//rdandwrsignalconnecttord,weofmc