allegro162 PCB布线2.docx

《allegro162 PCB布线2.docx》由会员分享,可在线阅读,更多相关《allegro162 PCB布线2.docx(29页珍藏版)》请在冰豆网上搜索。

allegro162PCB布线2

4.2布线规则设置

布线约束规则是PCB布线中很重要的一步工作,规则设置和好坏直接影响到PCB信号的好坏和工作效率。

布线规则主要设置的是差分线,线宽线距,等长匹配,过孔等等。

下面一步一步设置这些规则。

约束规则在约束管理器中设置。

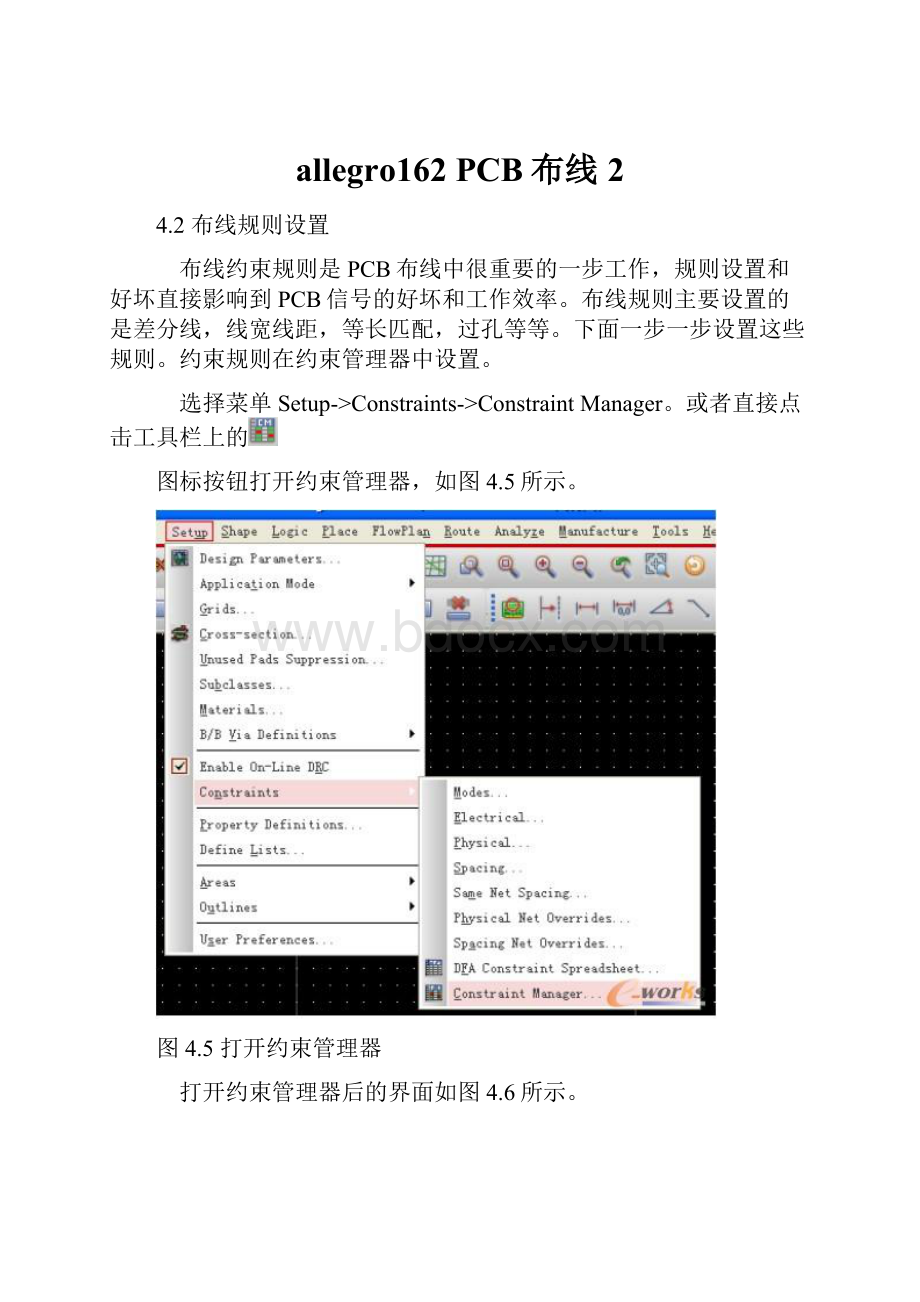

选择菜单Setup->Constraints->ConstraintManager。

或者直接点击工具栏上的

图标按钮打开约束管理器,如图4.5所示。

图4.5打开约束管理器

打开约束管理器后的界面如图4.6所示。

图4.6约束管理器

可以看到界面包含了两个工作区,左边是工作簿/工作表选择区,用来选择进行约束的类型;右边是工作表区,是对应左边类型的具体约束设置值。

在左边共有6个工作表,而一般只需要设置前面四个工作表的约束就可以了,分别是Eelctrical、Physical、Spacing、SameNetSpacing。

分别对应的是电气规则的约束、物理规则的约束,如线宽、间距规则的约束(不同网络)、同一个网络之间的间距规则。

为了能更好的使用约束管理器,先做一点基本概念的解释。

4.2.1对象(object)

对象是约束所要设置的目标,是具有优先级的,顶层指定的约束会被底层的对象继承,底层对象指定的同样约束优先级高于从顶层继承下来的约束,一般尽量在顶层指定约束。

最顶层的对象是系统system,最底层的对象是管脚对pin–pair。

对象的层次关系依次为:

系统(system)->设计(Designe)->总线(bus)->网络类(netclass)->总线(bus)->差分对(differentialpair)->扩展网络/网络(Xnet)->相对或匹配群组(Matchgroup)->管脚对(Pinpair)

(1)系统(system)

系统是最高等级的对象,除了包括设计(比如单板)之外,还包括连接器这些设计的扩展网络、互连电缆和连接器。

(2)设计(Designe)

设计代表一个单板或者系统中的一块单板,在多板结构中,每块板都是系统的一个单独的设计。

(3)网络类集合(netclass)

网络类集合可以是总线、网络扩展网络、差分对及群组匹配的集合。

(4)总线(bus)

总线是管脚对、网络或者扩展网络的集合。

在总线上获取的约束被所有总线的成员继承。

在与原理图相关联时,约束管理器不能创建总线,而且总线是设计层次的,并不属于系统层次。

(5)差分对(differentialpair)

用户可以对具有差分性质的两对网络建立差分对。

(6)扩展网络/网络(Xnet)

网络就是从一个管脚到其他管脚的电子连接。

如果网络的中间串接了被动的、分立的器件比如电阻、电容或者电感,那么跨接在这些器件的两个网络可以看成一个扩展网络。

如图4.7所示,网络net1、net2和net3组成一个扩展网络。

图4.7Xnet

(7)相对或匹配群组(Matchgroup)

匹配群组也是网络、扩展网络和管脚对的集合,但集合内的每个成员都要匹配或者相对于匹配于组内的一个明确目标,且只能在【relativepropagationdelay】工作表定义匹配群组,共涉及了三个参数,目标,相对值和偏差。

如果相对值没有定义,匹配群组内的所有成员将是绝对的,并允许一定的偏差。

如果定义了相对值,那么组内的所有成员将相对于明确的目标网络。

·目标:

组内其他管脚对都要参考的管脚对就是目标,目标可以是默认的也可以是明确指定的管教对,其他的管脚对都要与这个目标比较。

·相对值:

每个成员与目标的相对差值,如果没有指定差值,那么所有成员就需要匹配,如果此值不为0,群组就是一个相对匹配的群组。

·偏差:

允许匹配的偏差值。

(8)管脚对(Pinpair)

管脚对代表一对逻辑连接的管脚,一般是驱动和接收。

Pinpair可能不是直接连接的,但是肯定存在于同一个网络或者扩展网络中。

分页

4.2.2建立差分对

本设计中共有三对差分线信号,分别是DDR内存时钟信号、USBOTG数据信号、USBHOST数据信号。

在约束管理器中选择Objects->Create->DifferentialPair,如图4.8所示。

图4.8建议差分对

弹出CreateDifferentialPair对话话,如图4.9所示。

图4.9CreateDifferentialPair对话框

在左上角的下拉框中选择Net,然后在下面的列表框中找到DDR内存芯片的两个时钟信号网络分别是XM1SCLK、XM1SCLKN在列表框中双击这两个网络或者单击选中后点

按钮加到右边的Selections编辑框中。

在DiffPairName编辑框中输入差分对的名字:

DDRCLK,然后点击Create按钮。

点击Close关闭对话框。

其它的两个差分对用同样的方法建立,这里就不重复了。

最后点击左边Eelctrical工作表下的Net->Routing,在右边的工作表中就可以看到设置好的三个差分对。

如图4.10所示。

图4.10设置好的差分对

4.2.3差分对规则设置

建立好差分对后,还需要建立一个专门于差分对的电气规则。

首先点击左边工作表选择区中的Eelctrical工作表下的EelctricalConstraintSet->Routing->DifferentialPair,然后选择菜单Objects->Create->EelctricalCSet,如图4.11所示。

图4.11差分对规则设置

弹出CreateElectricalCSet对话框,如图4.12所示。

在ElectricalCSet编辑框中输入该约束规则的名称:

DIFF_FAIR,点击OK关闭对话框。

图4.12CreateElectricalCSet对话框

这时候在右边的工作表内我看看到多了一个DIFF_PAIR约束规则,如图4.13所示。

图4.13增加的DIFF_PAIR规则

下面给这个差分对约束规则设置参数。

差分对约束规则参数主要有以下几个:

·UncoupledLength:

差分对网络中的不匹配的长度。

即不能按差分对走线的总长度。

·MinLineSpacing:

最小的线间距。

·PrimaryGap:

差分对最优先选择的线间距(边到边间距)。

·PrimaryWidth:

差分对最优先选择的线宽。

·NeckGap:

差分对在Neck模式下的线间距(边到边间距),用于在布线密集区域内切换到Neck模式,这时差分走线的线间距由PrimaryGap设定的值切换到该值。

·NeckWidth:

差分对在Neck模式下的线宽,用于在布线密集区域内切换到Neck模式,这时差分走线的线宽由PrimaryWidth设定的值切换到该值。

最后设置的差分线规则约束参数如图4.14所示。

图4.14设置好的差分线约束参数

由于布线密度大走线空间有线,所以差分线的间距采用1W原则(线边到线边),如果空间允许,可采用3W原则。

分别设置了Primary模式和Neck模式下的线宽和线间距为(5mil,5mil),(3.15mil,3.15mil)。

Neck模式主要用于从CPU芯片扇出时候的线宽线间距。

设置好差分线约束规则后,将该约束规则应用到刚才建立的两个差分信号上,点击左边工作表选择区中的Eelctrical工作表下的Net->Routing在右边的工作表中找到刚才建立的三个差分对,在ReferencedElectriclCSet列中选择刚设置好的差分对约束规则DIFF_PAIR,如图4.15所示。

图4.15将差分对约束规则应用到差分对上

4.2.4CPU与DDR内存芯片走线约束规则

CPU与DDR内存之间的信号速度都很高,对信号完整性要求很高,需要对时序严格的匹配,以满足信号波形的完整性。

布线要求如下:

(1)DDR时钟线,要求差分布线,并要求精确控制差分对的走线等长误差,控制在20mil以内。

由于DDR内存使用两片,所以时钟线走线要采用T形或者Y形拓扑结构。

阻抗控制在100Ω,长度比地址线长。

(2)DDR数据线,CPU的数据总线宽度为32位,使用两片16位的DDR内存与之连接,所以然CPU的数据线为分两组,DATA0-DATA15,DQS0、DQS1,DQM0、DQM1为一组;DATA16-DATA31,DQS2、DQS3,DQM2、DQM3为一组。

两组的所有信号线需要严格等长匹配,误差控制在50mil以内。

由于布线密度大空间有限,信号间距采用1W原则(线边到线边),如果空间足够应选择3W原则,DDR数据线与其它的信号线必需要足够的间距,至少要保证3W的间距。

阻抗控制在60Ω以内。

(3)DDR地址线与其它控制线,DDR地址线与其它控制线为一组,需严格等长匹配,误差控制在100mil以内,走线长度比DDR数据线长。

采用T形或者Y形拓扑结构。

以上约束需要从电气、线宽和间距上分别设置不同的规则,现先讲Electrical工作表下的规则设置。

点击左边工作表选择区中的Eelctrical工作表下的EelctricalConstraintSet->Routing工作表,选择菜单Objects->Create->EelctricalCSet建立两个规则(名称分别为DDR_DQ,DDR_ADDR),过程参考4.2.3小节,建立好的规则如图4.16所示。

图4.16建立DDR约束规则

参数不需要设置。

然后点击左边工作表选择区中的Eelctrical工作表下的EelctricalConstraintSet->Routing->RelativePropagation工作表,鼠标放在右边刚才建立的两个规则(DDR_DQ,DDR_ADDR)上,点击右键,在弹出的菜单中选择Create->MatchGroup,如图4.17所示。

图4.17建立DDR等长匹配规则

在弹出的CreateElectricalCSetMatchGroup对话框中输入名称MATCH_LENTH,如图4.18所示。

点击OK关闭对话框。

图4.18CreateElectricalCSetMatchGroup对话框

在PinPairs列的下拉框中选择LongestPinPair,Scope列选择Class,Delta:

Tolerance列中先点击下面的按钮,选择单位为mil,然后在编辑框中输入:

0mil:

100mil(0mil:

50mil)。

最后如图4.19所示。

注意,只有在RelativePropagation工作表下才能建立这个规则。

图4.19DDR等长匹配群组参数

分页

接下来设置等数据线与地址线的等长匹配。

先建立两个名称分别为DDR_DATA,DDR_ADDR的NetClass。

点击左边工作表选择区中的Eelctrical工作表下的Net->Routing->RelativePropagation工作表。

在右边的工作表区中同时选中网络XM1DATA0-XM1DATA31,XM1DQM0-XM1DQM2,XM1DQS0-XM1DQS2(选中后会这些网络名会反色显示),点击鼠标右键,弹出一个菜单项,选择Create->NetClass。

如图4.20所示。

图4.20建立DDR_DATANetClass

弹出CreateNetClass对话框,如图4.21所示。

输入名称DDR_DATA,点击OK关闭对话框。

图4.21CreateNetClass对话框

建立DDR_ADDR的过程也一样,同时选中网络XM1ADDR0-XM1ADDR15,XM1CASN、XM1CKE0、XM1CSN0、XM1RASN、XM1WEN后右键Create->NetClass。

其它就不重复了。

然后将上一步建立的两个电气规则DDR_DQ,DDR_ADDR分别应用到DDR_DATA,DDR_ADDR两个NetClass上。

在右边的工作表区内,分别点击DDR_DATA,DDR_ADDRNCls的ReferencedElectricalCSet编辑框,分别选择DDR_DQ,DDR_ADDR。

这时候,约束管理器自动建立了两个MachGroup(MATCH_LENTH_DDR_ADDR,MATCH_LENTH_DDR_DATA),如图4.22所示。

图4.22等长匹配

由于CPU的地址线和其它的一些控制信号被两片DDR内存芯片共用,所以还需要建立一个管脚对(PinPair)匹配组来约束等长匹配。

在右边工作表区内将DDR_ADDRNetClass展开,在XM1ADDR0网络上点击右键,弹出一个菜单项选择Create->PinPair。

如图4.23所示。

图4.23建立PinPair

弹出CreatePinPairsofXM1ADDR0对话框,如图4.24所示。

在左右两个编辑框中分别列出了该网络上的所有元件的引脚(Pin),对于每个一XM1ADDRx网络,都有三个Pin。

所以每一个XM1ADDRx网络都需要建立两对管脚对,即CPU-DDR1,CPU-DDR2。

在左边的编辑框点点击U15,H24(Out),右边的编辑框中点击U16,J8(In),然后点击Apply按钮,即建立了U15,H24与U16,J8两个管脚的PinPair。

接着在左边的编辑框点点击U15,H24(Out),右边的编辑框中点击U17,J8(In),然后点击Apply按钮。

又建立了U15,H24与U17,J8两个管脚的PinPair。

点击OK后关闭对话框。

在工作表区可以看到,在XM1ADDR0网络下多了两个PPr(PinPair)U15,H24:

U16,J8,U15,H24:

U17,J8。

如图4.25所示。

用同样的方法为DDR_ADDRNetClass的每一个网络建立两个管脚对。

然后将刚才建立的所有管脚对选中,点击右键,弹出的菜单项中选择Create->MatchGroup。

如图4.26所示。

图4.24CreatePinPairs对话框

图4.25XM1ADDR0网络上的两个PinPair

图4.26建立管脚对匹配群姐

在弹出的CreateMatchGroup对话框中输入名称:

MATCH_PPR_ADDR。

点击OK关闭对话框。

如图4.27所示。

图4.27CreateMatchGroup对话框

在工作表区可以看到增加了一个MATCH_PPR_ADDR的MGrp,点击Delta:

Tolerence编辑框,将匹配值修改为0mil:

100mil。

即误差控制在100mil内。

如图4.28所示。

图4.28MATCH_PPR_ADDR匹配群组

分页

4.2.5设置物理线宽和过孔

点击约束管理器左边工作表选择区里的Pysical工作表,然后再点击Pysical->ConstraintSet->AllLayer工作表。

在右边的工作表中可以看到已经有一个默认的规则了(名称为DEFAULT),这个规则是建立电路板的时候allegro自动生成的,所有的网络的线宽如果没有特别指定,都是默认使用这个规则,所以要把这个规则的参数修改一下。

这个板子如果没有特别要求的走线都将采用4mil的线宽,所以把DEFAULT规则的线宽都改成4mil。

改好后的DEFAULT规则如图4.29所示。

图4.29DEFAULT规则参数

在线宽约束规则中一般只要填写MinLineWidth,NeckMinWidth,DifferentialPair下的MinLineSpaceing,PrimaryGap和NeckGap。

最后要设置PCB中需要用到的过孔,点击Vias的编辑框,如图4.30所示。

图4.30添加VIA

弹出EditViaList对话框,如图4.31所示。

图4.31EditViaList对话框

把Showviasfromthelibrary复选框勾上,在左边的Selectaviafromthelibraryorthedatabase下面的列表框中就会列出你设置的库路径中的所有焊盘过孔,如果没有请检查你设置的库路径是否正确,参考112.2小节。

在左边的列表框中找到你需要添加的过孔双击后该过孔就会出现在右边的列表框,在右边有三个按钮,点击Remove可以删除一个已选择的过孔。

点击Up或者Down可以改变已选的过孔的上下位置,一般把用得最频繁的那个过孔放在最顶的位置,这样,当在布线的时候需要添加过孔会默认选择最顶的那个过孔,可以提高效率。

选择好以后,点击OK关闭对话框。

可以看到在工作表中Vias列的编辑框内就出现在刚才选择的过孔,如图所示。

图4.32添加好的过孔

另外一点,由于这个板子需要用到盲埋孔,盲里孔是用过孔生成的,在后面的章节讲。

下面增加两个线宽约束规则,点击菜单Objects->Create->PhysicalCSet如图4.33所示。

图4.33新增线宽约束规则

弹出CreatePhysicalCSet对话框,在PhysicalCSet编辑框内输入规则名称3.15MIL_WIDTH(另一个10MIL_WIDTH)点击OK关闭对话框。

图4.34CreatePhysicalCSet对话框

在右边的工作表中可以看到增加的两个约束规则,并且参数与DEFAULT是完全一样的,如图4.35所示。

图4.35新增的两个线宽约束规则

其中3.15MIL_WIDTH约束规则将用于S3C6410BGA封装扇出时候的线宽(3.15mil),因为BGA内部的空间有限,不可能采用更大的线宽,将这个约束规则应用到一个区域规则中,放在后面的章节讲。

而10MIL_WIDTH可用于需要加粗的网络,比如电源网络,我们将这个规则应用到一些电源网络上。

如果有需要还可以增加更多的线宽约束。

下面要修改3.15MIL_WIDTH和10MIL_WIDTH两个约束规则的参数,将3.15MIL_WIDTH约束规则的参数都设为3.15,10MIL_WIDTH都设为10,由于VIA已经自动从DEFAULT规则上复制了,所以就不需要另外添加过孔了,修改好后的参数如图4.36所示。

图4.36修改后的两个线宽约束规则参数

下面将10MIL_WIDTH约束规则应用到电源网络上。

点击左边工作表选择区的Net->AllLayer工作表,在右边的工作表中区列出了设计中的所有Net,可以看到所有网络的ReferencedPhysicalCSet列中都是DEFAULT这个规则,这是allero自动添加的应用。

首先建立一个NetClass将所有的电源网络都包括在这个NetClass中。

选择菜单Objects->Create->NetClass,如图4.37所示。

图4.37增加NetClass

分页

弹出CreateNetClass对话框,如图4.38所示。

在NetClass编辑框中输入名称POWER点击OK关闭对话框。

图4.38增加POWERNetClass

在右边的工作表中可以看到增加了POWERNCls。

然后在这个NetClass上点击右键弹出一个菜单项,选择Membership->NetClass,如图4.39所示。

图4.39为NetClass增加成员

弹出NetClassMembershipforPOWER对话框,如图4.40所示。

在左上角的下拉框中选择Net,之后左边的列表框就列出所有的网络,双击需要添加的电源网络将它加到右边的列表框中,也可以单击选中目标网络后点击

按钮将它加入到右边的列表框。

全部添加完后,点击OK关闭对话框。

在右边的工作表区中,可以看到,刚才选择的网络都加入到了POWER的NetClass中了。

然后点击POWRERNCls的ReferencedPhysicalCSet编辑框,选择刚才建立好的10MIL_WIDTH约束规则。

最后如图4.41所示。

图4.40NetClassMembershipforPOWER对话框

图4.41将10MIL_WIDTH规则应用到POWER上

最后要将3.15MIL_WIDTH这个规则应用到一个Region(区域)规则上,以便在BGA芯片(S3C6410)扇出的时候能够使用合适的线宽。

点击左边Physical工作表下的Region->AllLayer。

然后选择菜单Objects->Create->Region,如图4.42所示。

图4.42新建区域规则

弹出CreateRegion对话框,输入名称BGA_RGN,点击OK关闭对话框,如图4.43所示。

图4.43CreateRegion对话框

然后在右边工作表区里新增了一个BGA_RGNRgn。

点击ReferencedPhysicalCSet编辑框3.15MIL_WIDTH规则应用到BGA_RGN规则上。

如图4.44所示。

图4.44绑定BGA_RGN规则

如果你自己建了更多更详细的规则需要应用到其它网络上,方法也是一样的,这里就不重复了。

4.2.6设置间距约束规则

间距约束规则包括不同网络之间与相同网络之间。

间距规则约束比较复杂,需要考虑信号完整性、阻抗要求以及制板工艺要求等。

在4.2.4小节介绍了CPU与内存之间的信号布线要求,为了实现信号完整性的要求我要们专门为CPU与内存之间的信号线、地址控制信号线设置间距约束规则。

首先修改由allegro自动生成的默认间距规则DEFAULT。

点击左边工作表选择区的Spacing工作表下的SpacingConstraintSet->AllLayer,在右边可以看到有一个DEFAULT间距规则。

间距规则参数比较多,约束管理器将这些参数分成了七大类,每一类用一个单独的电子表格列出来,分别是:

Line、Pins、Vias、Shape、BondFinger、Hole、BBviaGap。

如图4.45所示。

图4.45间距规则参数分类

现在将DEFAULT规则的Line、Pins、Vias、BondFinger、Hole、BBviaGap页面下的所有参数设为4mil,而Shape页面下的参数则设为10mil。

Shape页面参数是设置铺铜与其它对象的间距,因此要大一些。

如图4.46所示。

图4.46DEFAULT规则间距参数

新建一个3.15MIL_SPACE规则用于BGA的区域规则。

点击菜单Objects->Create->SpacingCSet,建立一个名称为3.15MIL_