数字逻辑数字频率计的设计课程设计报告.docx

《数字逻辑数字频率计的设计课程设计报告.docx》由会员分享,可在线阅读,更多相关《数字逻辑数字频率计的设计课程设计报告.docx(15页珍藏版)》请在冰豆网上搜索。

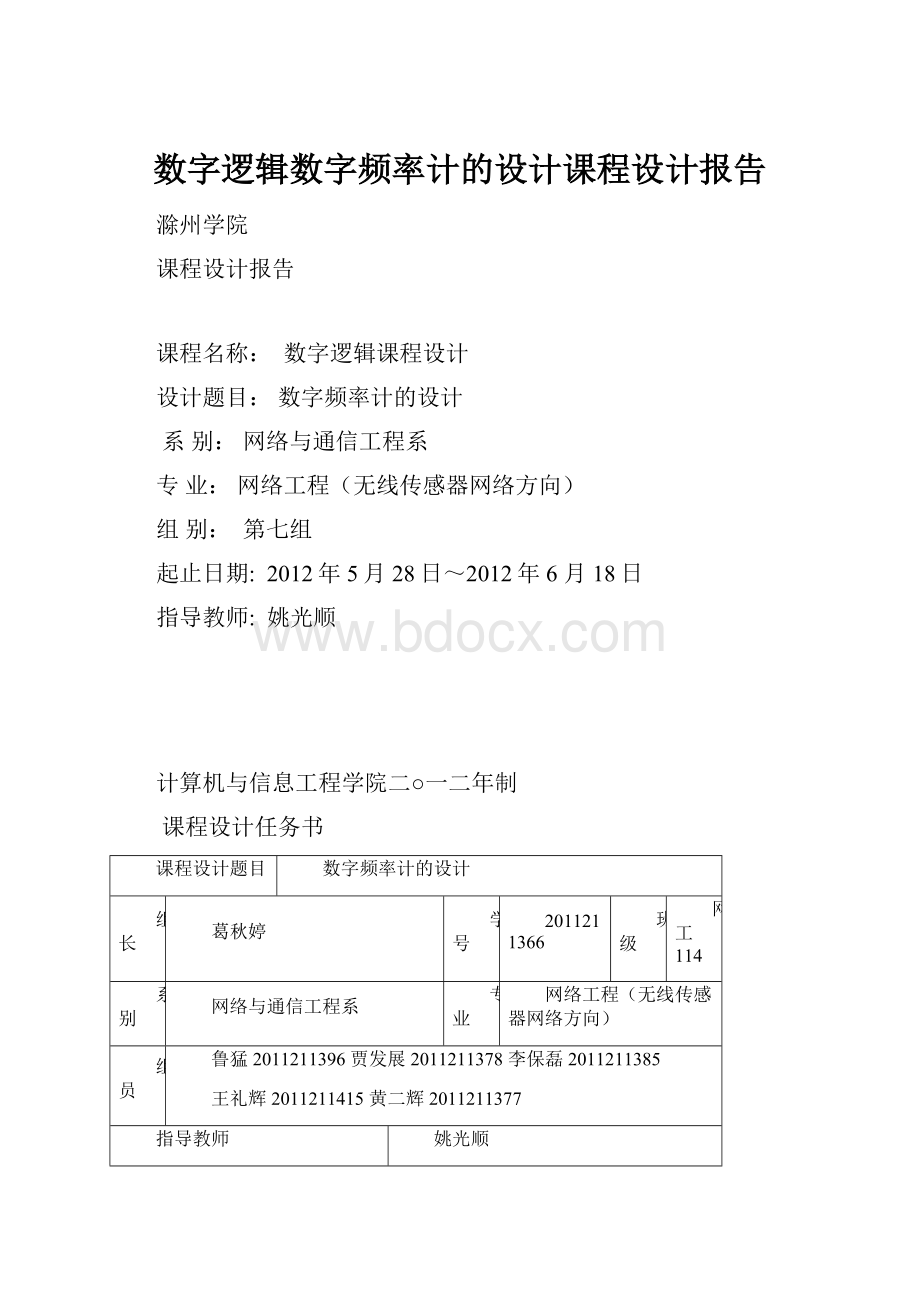

数字逻辑数字频率计的设计课程设计报告

滁州学院

课程设计报告

课程名称:

数字逻辑课程设计

设计题目:

数字频率计的设计

系别:

网络与通信工程系

专业:

网络工程(无线传感器网络方向)

组别:

第七组

起止日期:

2012年5月28日~2012年6月18日

指导教师:

姚光顺

计算机与信息工程学院二○一二年制

课程设计任务书

课程设计题目

数字频率计的设计

组长

葛秋婷

学号

2011211366

班级

网工114

系别

网络与通信工程系

专业

网络工程(无线传感器网络方向)

组员

鲁猛2011211396贾发展2011211378李保磊2011211385

王礼辉2011211415黄二辉2011211377

指导教师

姚光顺

课程设计目的

掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的

设计、安装、测试方法。

课程设计所需环境

Windows7,NIMultisim11

课程设计任务要求

频率测量范围:

1Hz~10KHz;

数字显示位数:

四位静态十进制计数显示被测信号的频率

课程设计工作进度计划

序号

起止日期

工作内容

分工情况

1

2012/6/8-2012/6/10

组员在一起讨论,发表个人看法

查好资料后,小组成员都积极参与讨论

2

2012/6/11-2012/6/13

上机搭建仿真电路,做报告文档

贾发展、黄二辉、李保磊、王礼辉搭建仿真电路,葛秋婷、鲁猛做报告文档,

3

2012/6/14-2012/6/15

调试仿真电路

组员一起组合、调试电路,运行出正确的结果

4

2012/6/16-2012/6/18

撰写课程设计报告

鲁猛、葛秋婷撰写设计实验报告

5

2012/6/19

提交报告

由组长将报告提交予老师查看,请老师指导

6

2012/6/20

完善报告并提交

由组长提交设计报告

目录

1绪论1

1.1设计背景1

1.2主要工作和方法1

1.3本文结构1

2相关知识1

2.1数字频率计概念…..1

2.2数字频率计组成1

3系统设计2

4系统实现2

4.1计数译码显示电路2

4.2控制电路3

5系统测试与数据分析5

6课程设计总结与体会8

6.1设计总结8

6.2设计体会8

结束语9

参考文献9

附录10

致谢12

1绪论

1.1设计背景

数字频率计是一种基础测量仪器,到目前为止已有30多年的发展史。

早期,设计师们追求的目标主要是扩展测量范围,再加上提高测量精度、稳定度等,这些也是人们衡量数字频率计的技术水平,决定数字频率计价格高低的主要依据。

目前这些基本技术日臻完善,成熟。

应用现代技术可以轻松地将数字频率计的测频上限扩展到微频段。

随着科学技术的发展,用户对数字频率计也提出了新的要求。

对于低档产品要求使用操作方便,量程(足够)宽,可靠性高,价格低。

而对于中高档产品,则要求有高分辨率,高精度,高稳定度,高测量速率;除通常通用频率计所具有的功能外,还要有数据处理功能,统计分析功能,时域分析功能等等,或者包含电压测量等其他功能。

这些要求有的已经实现或者部分实现,但要真正完美的实现这些目标,对于生产厂家来说,还有许多工作要做,而不是表面看来似乎发展到头了。

随着数字集成电路技术的飞速发展,应用计数法原理制成的数字式频率测量仪器具有精度高、测量范围宽、便于实现测量过程自动化等一系列的突出特点。

1.2主要工作和方法

设计一个数字频率计。

要求频率测量范围为1Hz-10kHz。

数字显示位数为四位静态十进制计数显示被测信号。

先确定好数字频率计的组成部分,然后分部分设计,最后组成电路。

1.3本文结构

本文第1部分前言主要说明频率计的用处和广泛性。

第2部分简要说明了本次课程设计的要求。

第3部分概要设计大致的勾画出本次设计的原理框架图和电路的工作流程图。

第4部分简要说明4位二进制计数器74160的原理和搭建计数译码显示电路的原理,同时分析控制电路的功能,形成控制电路图,及搭建显示电路和控制电路的组合原理图。

第5部分调试与操作说明,介绍相关的操作和输入不同频率是电路的显示情况。

2相关知识

2.1数字频率计介绍

2.1.1数字频率计概念

数字频率计是一种直接用十进制数字现设被测信号频率的一种测量装置,它不仅可以测量正弦波、方波、三角波等信号的频率,而且还可以用它来测量被测信号的周期。

经过改装,在电路中增加传感器,还可以做成数字脉搏计、电子称、计价器等。

因此,数字频率计在测量物理量方面有广泛的应用。

2.1.2数字频率计组成

数字频率计由振荡器、分频器、放大整形电路、控制电路、计数译码显示电路等部分组成。

其中的控制脉冲采用时钟信号源替代,待测信号用函数信号发生器产生。

数字频结构原理框图如图3.1所示。

施密特整形

计数

译码

数码

显示

待测计数

信号

闸门

检测

清

零

分

频

晶

振

控制电路

选通

图3.1数字频率计结构图

3系统设计

数字频率计由振荡器、分频器、放大整形电路、控制电路、计数译码显示电路等部分组成。

由振荡器的震荡电路产生一标准频率信号,经分频器分频得到控制脉冲。

控制脉冲经过控制器中的门电路分别产生选通脉冲、锁存信号和清零信号。

待测信号经过限幅、运放的放大、施密特整形之后,输出一个与待测信号同频率的矩形脉冲信号,该信号在检测门经过与选通信号合成,产生计数信号。

计数信号并与锁存信号和清零复位信号共同控制计数、锁存和清零三个状态,然后通过数码显示器件显示。

此实例主要分析频率计的工作原理,因此对振荡器、分频器、放大整形电路略过,着重对控制电路以及计数译码显示电路的设计。

其中的控制脉冲采用时钟信号源替代,待测信号用函数信号发生器产生。

4系统实现

4.1计数译码显示电路

选用带译码器的集成十进制计数芯片CD40110,该芯片有锁存控制端,可对计数进行锁存。

计数部分只显示锁存后的数据,每锁定一次,计数部分跳动一次,更新数据,如此往复。

因为仿真时受元器件的限制,通过讨论,最终选用4位二进制计数器74160,且要求显示四位,因此使用4组74160和数码管。

将各计数器的LOAD、ENP、ENT分别接高电平,个位的CLK端外接计数信号,低位的进位端接高位的CLK端,各芯片的CLR端连接起来外接清零信号,4个输出端接数码管,以此实现一个能显示4位十进制的计数器,图4.1为连接后的电路。

图4.1计数译码显示电路

4.2控制电路

控制电路是整个数字频率计正常工作的核心部分,需仔细分析各种频率信号(计数、选通、锁存、清零)的时序关系,以最终控制计数译码显示电路的工作状态。

由于功能要求识别的最小频率是1Hz,因此将选通信号的高电平时间定为1s,在这个时间段内允许待测信号输入进行计数,锁存和清零信号的输出均为高电平。

在选通信号为低电平时关闭闸门,计数停止,处于数据锁存的时间段,此时的锁存信号为低电平,清零信号仍为高电平,直到选通信号的下一个高电平到来之前(开始下一个计数),清零信号端输出一个低电平实现数码管显示的清零,准备进入下一个计数周期。

如此往复,以实现待测信号频率的反复测量。

这几个信号的工作时序如图4.2所示。

选通信号

计数信号…

锁存信号

清零信号

图4.2控制电路各频率信号时序关系

当JK触发器的J、K端同时接高电平时,输出端的状态会随着每输入一个脉冲改变一次。

因此JK触发器输入端的频率是输出端的两倍,这就是通常认为的二分频。

将输出端加到下一个JK触发器的时钟端又可实现频率的再次二分频,以此类推可实现频率的逐次分频,电路连接图如图4.3。

图4.3JK触发器分频电路

工作时序如图4.4所示。

CP

Q1

Q2

图4.4JK触发器工作时序图

创建如图4.5所示的电路,根据控制电路各信号时序分析得知,选通信号的周期应大于等于锁存信号和清零信号,因此选用上述电路的Q2端作为选通信号的输出端,假定选通信号的高电平时间为1s,那Q2端的频率应为0.5Hz,由此可推出CP端和Q1端的信号频率分别为2Hz和1Hz。

在Q2端的选通信号为高电平时,允许计数,频率计开始工作,当Q2端进入低电平段,频率计转为锁存阶段,直至下一个Q2端高电平到来前需要一个清零信号。

观察图的工作时序可知,在Q2端的第二个高电平到来前,CP、Q1、Q2端均为低电平,用一个3输入的或门将这三个端口连接,输出一个低电平作为清零信号,加到计数译码显示电路的CLR端。

由此得到选通信号周期为2s,计数时间为1s,锁存时间为0.75s,清零时间为0.25s。

图4.5JK触发器构成的数字频率计电路原理图

5系统测试与数据分析

在系统各个模块电路设计完成后,根据所选择的电路方案和整机电路图,对应仿真链接,检查无误后进行数字电路连接。

其调试如下步骤:

(1)输入信号10Hz。

电路如图5.1所示。

图5.1输入信号为10Hz时电路显示

(2)输入信号1Hz,电路图如图5.2所示。

图5.2输入信号为1HZ时电路显示

(3)输入信号100Hz,电路图如图5.3所示。

图5.3输入信号为100Hz时电路显示

(4)输入信号900Hz,电路图如图5.4所示。

图5.4输入信号为900Hz电路显示

(5)输入信号500Hz,电路图如图5.5所示。

图5.5输入信号为500Hz时电路显示

(6)输入信号9999Hz,电路图如图5.6所示。

图5.6输入信号为9999Hz时电路显示

6课程设计总结与体会

通过此次课程设计作业,我们学会了很多东西。

6.1设计总结

经过了一段时间的努力我们终于合作完成了数字频率计的设计,从芯片的选择,再到设计与实现。

在这个过程中我们学习到了很多在课本上不能学习到的知识,对一个产品也有了一个新的认识,以前我们都很简单的认为一个产品很容易就做出来了,现在我们知道了每一个产品都需要很复杂的工序。

通过这次的课程设计我们学到了主要有如下几点:

(1)提前做好准备工作在开始动手之前,我们要把各芯片件的功能弄清楚,以及如何拓展,只有把这些真正的搞懂之后才能顺利完成设计;

(2)耐心分析,解决问题设计与实现的过程中我们会遇到一些困难这是很正常的事,但是不能一遇到问题就慌了,要耐心的分析问题并解决,这次课程设计的时候我就遇到了这样的情况;

(3)团队合作,不懂请教。

6.2设计体会

在此次的数字频率计设计过程中,进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。

在连接电路时,要求熟悉逻辑电路及其芯片各引脚的功能,那么在电路出错时便能准确地找出错误所在并及时纠正了。

在设计电路中,往往是先仿真后连接实物图,但有时候仿真和电路连接并不是完全一致的,对该设计的建议:

此次的频率计设计重在于仿真和接线,虽然能把电路图接出来,并能正常显示,但对于电路本身的原理并不是十分熟悉.总的来说,通过这次的设计实验更进一步地增强了实验的动手能力。

结束语

本次课程设计简单的说明了4位二进制计数器74160的功能和JK触发器的功能,并以此设计了数字时钟仿真电路,而且能够实现4位计数的功能,完成了此次课程设计,基本满足设计要求。

参考文献

[1]彭介华.电子技术课程设计指导[M].北京:

高等教育出版社.2004

[2]王连英.基于Multisim10的电子仿真实验与设计[M].北京:

北京邮电大学出版社.2011

[3]余孟尝.数字电子技术基础简明教程[M].北京:

高等教育出版社.2006

附录

各逻辑门的引脚图

(1)74160N的逻辑引脚图(图a)

图a74160N逻辑引脚图

74160N功能表如表b。

表b74160N功能表

CLK

RCD

LOAD

EP

ET

工作状态

×

0

×

×

×

置零

↑

1

0

×

×

预置零

×

1

1

0

1

保持

×

1

1

×

0

保持(但C=0)

↑

1

1

1

1

计数

(2)7473N的引脚图(图c)

图c7473N引脚图

7473N功能如表d。

表d7473N功能表

CLR

CLK

J

K

Q

Q

0

×

×

×

0

1

1

1

0

0

保持

1

1

1

0

1

0

1

1

0

1

0

1

1

1

1

1

切换

致谢

经过多天大家一起努力,本次课程设计任务终于完成。

首先,感谢老师给与的指导和帮助,才使我们的设计和报告撰写逐步趋于完善;其次就是大家的积极,团结,在设计过程中各负其责,到问题积极提出意见。

在此向老师和组员们致以感谢。

评语:

评阅教师签名:

年月日

成绩