step7基本讲解.docx

《step7基本讲解.docx》由会员分享,可在线阅读,更多相关《step7基本讲解.docx(61页珍藏版)》请在冰豆网上搜索。

step7基本讲解

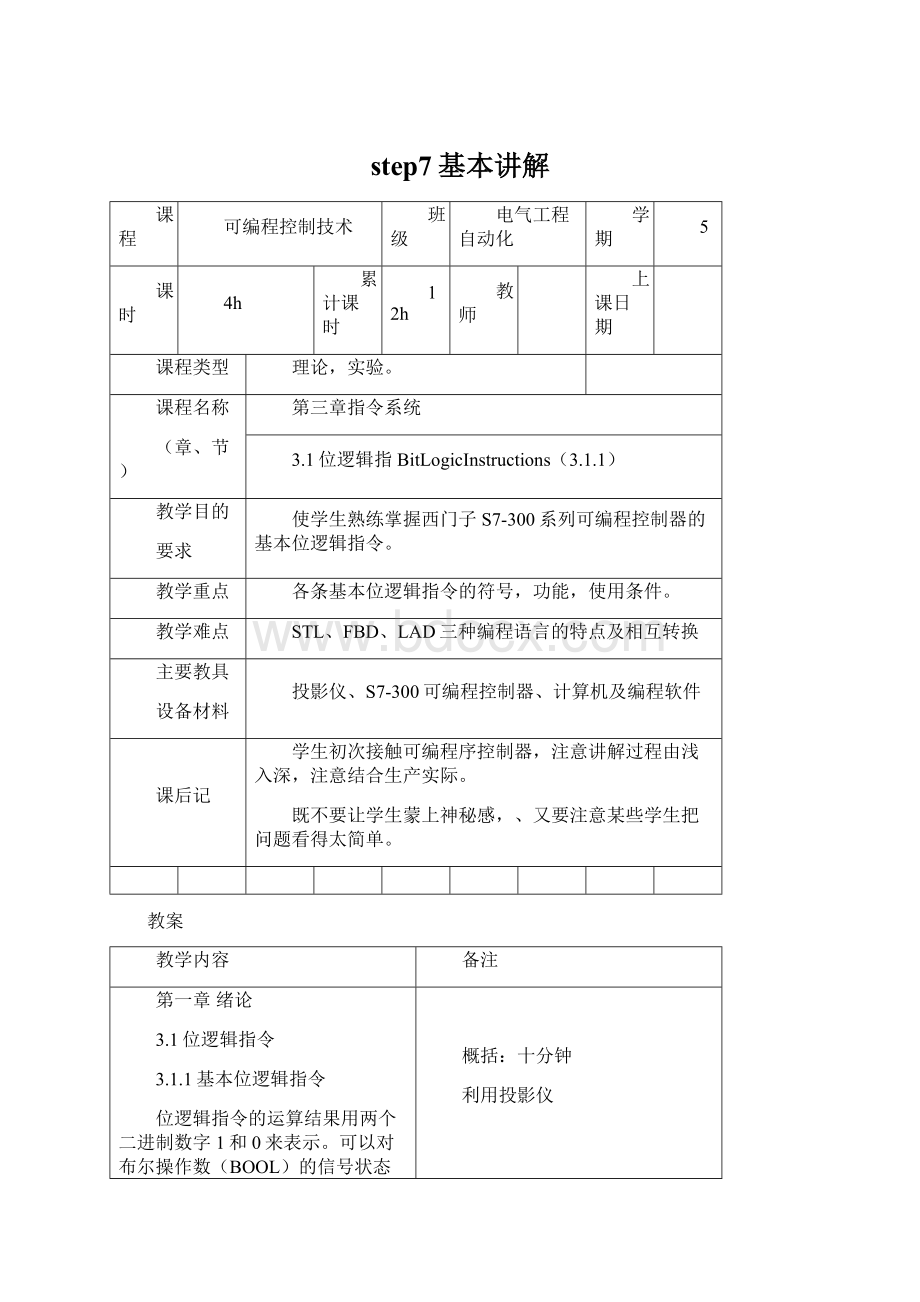

课程

可编程控制技术

班级

电气工程自动化

学期

5

课时

4h

累计课时

12h

教师

上课日期

课程类型

理论,实验。

课程名称

(章、节)

第三章指令系统

3.1位逻辑指BitLogicInstructions(3.1.1)

教学目的

要求

使学生熟练掌握西门子S7-300系列可编程控制器的基本位逻辑指令。

教学重点

各条基本位逻辑指令的符号,功能,使用条件。

教学难点

STL、FBD、LAD三种编程语言的特点及相互转换

主要教具

设备材料

投影仪、S7-300可编程控制器、计算机及编程软件

课后记

学生初次接触可编程序控制器,注意讲解过程由浅入深,注意结合生产实际。

既不要让学生蒙上神秘感,、又要注意某些学生把问题看得太简单。

教案

教学内容

备注

第一章绪论

3.1位逻辑指令

3.1.1基本位逻辑指令

位逻辑指令的运算结果用两个二进制数字1和0来表示。

可以对布尔操作数(BOOL)的信号状态扫描并完成逻辑操作。

逻辑操作结果称为RLO(resultoflogicoperation)。

语句表STL表示的基本位逻辑指令

●AAnd逻辑“与”

●ANAndNot逻辑“与非”

●OOr逻辑“或”

●ONOrNot逻辑“或非”

●XExclusiveOr逻辑“异或”

●XNExclusiveOrNot逻辑“异或非”

●=Assign赋值指令

●NOTNegateRLORLO取反

●SETSetRLO(=1)RLO=1

●CLRClearRLO(=0)RLO=0

●SAVESaveRLOinBRRegister将RLO的状态保存到BR。

边沿信号识别指令。

位逻辑指令的运算规则:

“先与后或”。

可以用括号将需先运算的部分括起来,运算规则为:

“先括号内,后括号外”。

梯形图LAD表示的基本位逻辑指令

●---||---NormallyOpenContact(Address)常开触点

●---|/|---NormallyClosedContact(Address)常闭触点

●---(SAVE)SaveRLOintoBRMemory

将RLO的状态保存到BR

●XORBitExclusiveOR逻辑“异或”

●---()OutputCoil输出线圈

●---(#)---MidlineOutput中间标志输出

●---|NOT|---InvertPowerFlowRLO取反

功能图FBD表示的位逻辑指令

将在后面的指令详解中给出

概括:

十分钟

利用投影仪

教案

教学内容

备注

1.逻辑“与”操作

当所有的输入信号都为“1”,则输出为“1”;只要输入信号有一个不为“1”,则输出为“0”。

例3.1.1:

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

语句表(STL)语言如下:

AI0.0

AI0.1

=Q4.0

2.逻辑“或”操作

只要有一个输入信号为“1”,则输出为“1”;所有输入信号都为“0”,输出才为“0”。

例3.1.2:

功能图(FBD)语言如下:

当输入信号I0.0和I0.1有一个以上为“1”时,输出信号Q4.0为“1”。

当输入信号I0.0和I0.1都为“0”时,输出信号Q4.0才为“0”。

梯形图(LAD)语言如下:

语句表(STL)语言如下:

OI0.0

OI0.1

=Q4.0

注意编程语言的三种表达方式及各自的特点。

教案

教学内容

备注

3.逻辑异或操作

当两个输入信号其中一个为“1”而另一个为“0”时,输出信号为“1”;当两个输入信号都为“0”或者都为“1”时,输出信号为“0”。

例3.1.3:

功能图(FBD)语言如下:

当输入信号I0.0为“1”而I0.2为“0”或者I0.0为“0”而I0.2为“1”时,输出信号Q3.1为“1”。

当输入信号I0.0和I0.2都为“0”或者I0.0和I0.2都为“1”时,输出信号Q3.1为“0”。

梯形图(LAD)语言如下:

语句表(STL)语言如下:

XI0.0

XI0.2

=Q3.1

4.逻辑取反操作

逻辑取反操作对逻辑运算结果RLO取反。

功能图(FBD)符号:

梯形图(LAD)符号:

---|NOT|---

语句表(STL)符号:

NOT

引导学生举出生活中异或关系的例子

教案

教学内容

备注

例3.1.4:

只有当I1.0和I1.1相与的结果为“0”并且I1.2和I1.3相与的结果为“1”或I1.4为“1”时,输出Q4.0才为“1”;否则Q4.0为“0”。

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

语句表(STL)语言如下:

AI1.0

AI1.1

NOT

A(

AI1.2

AI1.3

NOT

OI1.4

)

=Q4.0

5.中间输出符号

中间输出指令用于存储RLO的中间值,该值是中间输出指令前的位逻辑操作结果。

中间输出指令不能用于结束一个逻辑串,因此,中间输出指令不能放在逻辑串的结尾或分支的结尾处。

特别要讲清楚中间符号的作用

教案

教学内容

备注

例3.1.5

M0.0的缓存器中存放着I1.0和I1.1相与后取反的结果;

M1.1的缓存器中存放着I1.2和I1.3相与后取反的结果;

M2.2的缓存器中存放着I1.4的逻辑运算结果;

M3.3的缓存器中存放上述整个逻辑运算的结果。

例3.1.6

M0.0的缓存器中存放着I1.0和I1.1相与的结果;

M1.1的缓存器中存放着I1.0、I1.1、I1.2和I1.3四个输入信号相与后取反的结果;

M2.2的缓存器中存放着整个逻辑运算的结果。

6.位逻辑操作规则:

位逻辑指令的运算规则:

“先与后或”。

例3.1.7:

当输入信号I1.0和I1.1都为“1”,或输入信号I1.2和I1.3都为“1”时,输出信号Q3.1为“1”。

否则输出信号Q3.1为“0”。

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

重点强调

教案

教学内容

备注

语句表(STL)语言如下:

AI1.0

AI1.1

O

AI1.2

AI1.3

=Q3.1

例3.1.8:

当输入信号I1.0或I1.1为“1”,并且I1.2或I1.3为“1”时,输出信号Q3.1为“1”。

否则输出信号Q3.1为“0”。

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

语句表(STL)语言如下:

A(

OI1.0

OI1.1

)

A(

OI1.2

OI1.3

)

=Q3.1

牢记位逻辑运算的规则。

重点是在语句表中

课程

可编程控制技术

班级

电气工程自动化

学期

5

课时

4h

累计课时

16h

教师

上课日期

课程类型

理论,实验。

课程名称

(章、节)

第三章指令系统

3.1位逻辑指令BitLogicInstructions)

教学目的

要求

使学生熟练掌握西门子S7-300系列可编程控制器的置位/复位指令。

教学重点

置位/复位指令的符号,功能,使用条件。

教学难点

置位/复位指令的记忆功能。

主要教具

设备材料

投影仪、S7-300可编程控制器、计算机及编程软件

课后记

置位/复位指令对于较熟悉继电—接触器控制的学生来说是个较新的概念。

同时又是非常重要的指令。

注意引导学生结合数字电路的RS触发器以及继电—接触器系统中的“自保”结构充分理解。

教案

教学内容

备注

3.1.2置位/复位指令

置位/复位指令根据RLO的值,来决定被寻址位的信号状态是否需要改变。

若RLO的值为1,被寻址位的信号状态被置1或清0;若RLO是0,则被寻址位的信号保持原状态不变。

对于置位操作,一旦RLO为1,则被寻址信号(输出信号)状态置1,即使RLO又变为0,输出仍保持为1;对于复位操作,一旦RLO为1,则被寻址信号(输出信号)状态置0,即使RLO又变为0,输出仍保持为0。

语句表STL表示的置位/复位指令

●RReset复位指令

●SSet置位指令

梯形图LAD表示的置位/复位指令

●---(S)SetCoil线圈置位指令

●---(R)ResetCoil线圈复位指令

●SRSet-ResetFlipFlop复位优先型SR双稳态触发器指令

●RSReset-SetFlipFlop置位优先型RS双稳态触发器指令

功能图FBD表示的位逻辑指令

强调“记忆功能”

教案

教学内容

备注

1.置位/复位线圈指令

例3.1.9:

当I0.0和I0.1输入都为“1”或者I0.2输入为“0”时,Q4.0被置位,即输出为“1”;不满足上述条件时,Q4.0的输出状态不变。

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

语句表(STL)语言如下:

AI0.0

AI0.1

ONI0.2

SQ4.0

例3.1.10:

当I0.0和I0.1输入都为“1”或者I0.2输入为“0”时,Q4.0被复位,即输出为“0”;不满足上述条件时,Q4.0的输出状态不变。

功能图(FBD)语言如下:

梯形图(LAD)语言如下:

语句表(STL)语言如下:

AI0.0

AI0.1

ONI0.2

RQ4.0

注意与普通线圈符号的不同

教案

教学内容

备注

2.置位/复位双稳态触发器指令

如果置位输入端为“1”,复位输入端为“0”,则触发器被置位。

此后,即使置位输入端为0,触发器也保持置位不变。

如果复位输入端为1,置位输入端为“0”,则触发器被复位。

置位优先型RS触发器的R端在S端之上,当两个输入端都为1时,下面的置位输入端最终有效。

既置位输入优先,触发器被置位。

复位优先型SR触发器的S端在R端之上,当两个输入端都为1时,下面的复位输入端最终有效。

既复位输入优先,触发器被复位。

例3.1.11

如果输入信号I0.0=1,I0.0=0,则M0.0被复位,Q4.0=0;

I0.0=0,I0.0=1,则M0.0被置位,Q4.0=1;

I0.0=0,I0.0=0,则M0.0输出保持不变,Q4.0

输出不变;

I0.0=1,I0.0=1,则M0.0被置位,Q4.0=1。

例3.1.12

如果输入信号I0.0=1,I0.0=0,则M0.0被复位,Q4.0=0;

I0.0=0,I0.0=1,则M0.0被置位,Q4.0=1;

I0.0=0,I0.0=0,则M0.0输出保持不变,Q4.0

输出不变;

I0.0=1,I0.0=1,则M0.0被置位,Q4.0=0。

注意讲清楚置位优先型RS触发器和复位优先型SR触发器在功能图和语句表中的表示方法以及适用场合

教案

教学内容

备注

3.1.3边沿信号识别指令

1.RLO边沿信号识别指令

当信号状态变化时就产生跳变沿,当从0变到1时,产生一个上升沿(或正跳沿);若从1变到0,则产生一个下降沿(或负跳沿)。

跳变沿检测的原理是:

在每个扫描周期中把信号状态和它在前一个扫描周期的状态进行比较,若不同则表明有一个跳变沿。

因此,前一个周期里的信号状态必须被存储,以便能和新的信号状态相比较。

●下降沿信号识别指令

若CPU检测到输入有一个负跳沿,将使得输出线圈在一个扫描周期内通电。

对输入扫描的RLO值存放在存储位中。

在OB1的扫描周期中,CPU扫描并形成RLO值,若该RLO值是0且上次RLO值是1,这说明FN指令检测到一个RLO的负跳沿,那么FN指令把RLO位置1。

如果RLO在相邻的两