杭电数电习题解答.docx

《杭电数电习题解答.docx》由会员分享,可在线阅读,更多相关《杭电数电习题解答.docx(13页珍藏版)》请在冰豆网上搜索。

杭电数电习题解答

答案

数字逻辑基础

(一)将下列二进制数和十六进制数化成等值的十进制数

(1)(10110)2;

(2)(1011010)2;(3)(0.1011)2;(4)(0101.0110)2;

(5)(3B)16;(6)(FF)16;(7)(0.35)16;(8)(7A.C1)16

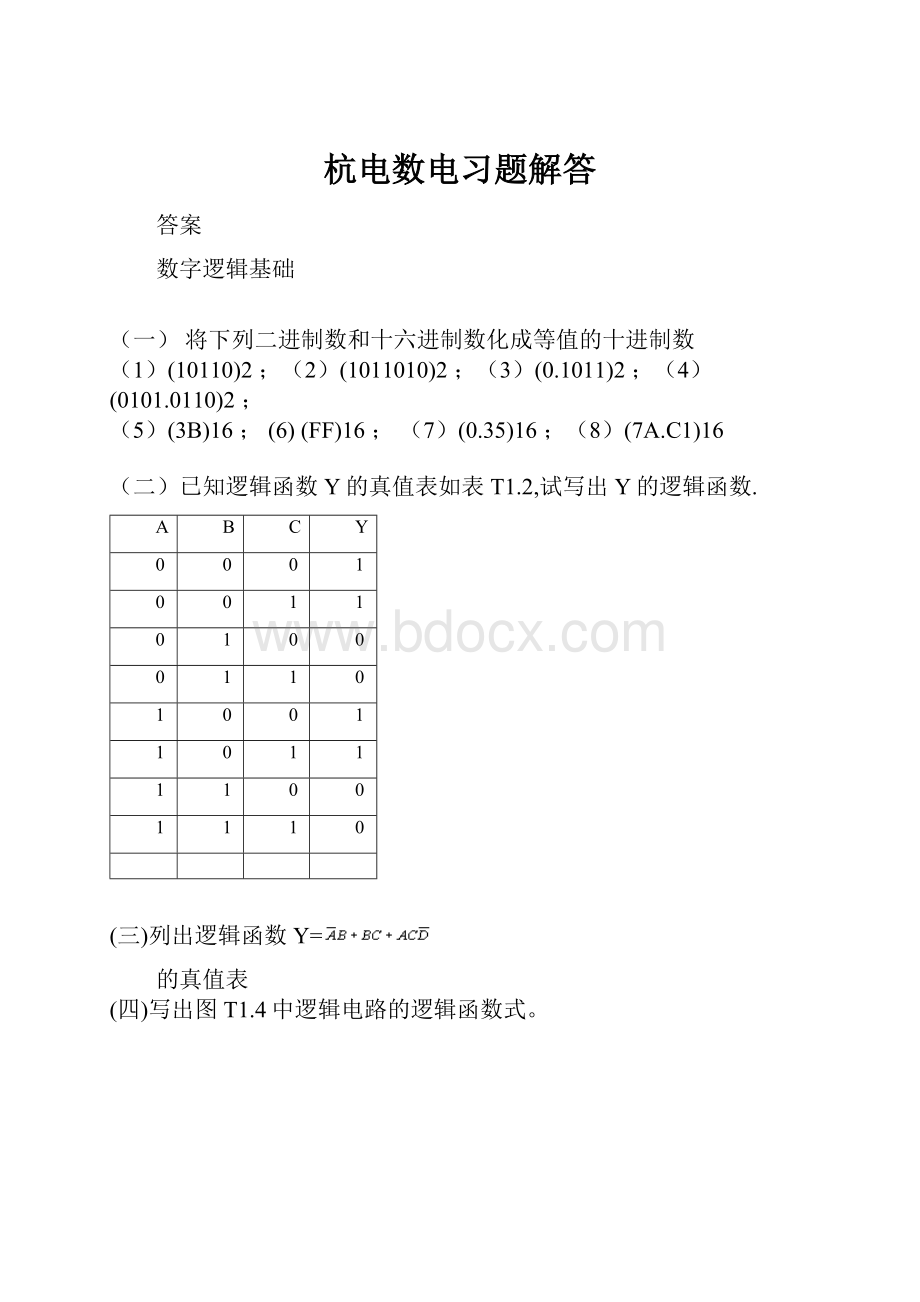

(二)已知逻辑函数Y的真值表如表T1.2,试写出Y的逻辑函数.

A

B

C

Y

0

0

0

1

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

0

(三)列出逻辑函数Y=

的真值表

(四)写出图T1.4中逻辑电路的逻辑函数式。

T1.4

(五)利用逻辑代数的基本公式和常用公式简化下列各式。

(六)指出下列各式中哪些是四变量A,B,C,D的最大项和最小项。

在最小项后的()里填m,在最大项后的()里填M,其他填X。

(七)写出图T1.7中各卡诺图所示的逻辑函数式。

T1.7

(八)用卡诺图化简以下逻辑函数

(九)化简逻辑函数

给定约束条件为

.

组合逻辑电路自我检测题

(一)分析图T3.1电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图T3.1

(二)图T3.2是一个多功能函数发生电路。

试写出当S0S1S2S3为0000~1111共16种不同状态时输出Y的函数逻辑式。

图T3.2

(三)试写出图T3.3电路输出Z的逻辑函数式。

4选1数据选择器74LS153的逻辑图见图

图T3.3

(四)写出图T3.4电路输出Y1,Y2的逻辑函数式。

3线-8线译码器74LS138的逻辑图见图3.4。

图T3.4

(五)试用数据选择器设计一个"逻辑不一致"电路,要求4个输入逻辑变量取值不一致时输出为1,取值一致时输出为0。

(六)什么叫竞争-冒险?

当门电路的两个输入端同时向相反的逻辑状态转换(即一个从0变成1,一个从1变成0)时,输出端输否一定有干扰脉冲产生?

时序逻辑电路

(一)触发器有哪几种常见的电路结构形式?

它们各有什么样的动作特点?

(二)分别写出RS触发器﹑JK触发器﹑T触发器和D触发器的特性表和特征方程。

(三)触发器的逻辑功能和电路结构形式之间的关系如何?

(四)在主从结构RS触发器电路中,若R﹑S﹑CP端的电压波形如图T4.4所示,试画出Q﹑端对应的电压波形。

假定触发器的初始状态为Q=0。

图T4.4

(五)在主从结构JK触发器中,已知J﹑K﹑CP端的电压波形如图T4.5所示,试画出Q﹑!

Q端对应的电压波形。

设触发器的初始状态为Q=0.

图T4.5

(六)在主从结构T触发器中,已知T﹑CP端的电压波形如图T4.6所示,试画出Q﹑!

Q端对应的电压波形。

设触发器的初始状态为Q=0。

图T4.6

(七)已知CMOS边沿触发器输入端D和时钟信号CP的电压波形如图T4.7所示,试画出Q和!

Q端对应的电压波形。

假定触发器的初始状态为Q=0。

图T4.7

(八)试比较路和时序逻辑电组合逻辑电路在逻辑功能上和电路结构上有何不同。

(九)指出下列各种电路结构类型的触发器中哪些能构成移位寄存器,哪些不能构成移位寄存器。

如果能够,请在()内画√,否则画×:

(1)基本RS触发器();

(2)同步RS触发器();(3)主从结构触发器( );

(4)维持阻塞触发器( );(5)用CMOS传输门的边沿触发器( )。

(十)分析图T4.10时序电路的逻辑功能,写出电路的驱动方程和输出方程,画出电路的状态转换图和时序图。

图T4.10

(十一)试画出用4片4位双向移位寄存器74LS194组成16位环行计数器的接线图。

74LS194的电路图和功能表见图T4.11和表4.11。

74LS194电路图和功能表

图T4.11

表4.11

(十二)画出用上升沿触发的维持阻塞触发起组成4位异步二进制加法计数器和减法计数器的逻辑图。

(十三)分析图T4.13时序逻辑电路功能,写出电路的驱动方程﹑状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

图T4.13

(十四)试用JK触发器和门电路设计一个同步七进制计数器。

(十五)试用同步十六进制计数器74LS161接成十二进制计数器。

74LS161的功能表见表4.15。

它的外部引线排列及功能与74161相同。

表4.15

(十六)画出用两片同步十进制计数器74LS160接成同步三十一进制计数器的接线图。

可以附加必要的门电路。

74160的逻辑图和功能表见图4.16和表4.15

图4.16

脉冲波形的产生和整形

(一)试述施密特触发器输入信号波形的工作特点和主要用途。

(二)若反响输出的施密特触发器输入波形如图T6.2所示,试画出输出信号的波形。

施密特触发器的转换电平VT+,VT-已在输入信号波形上标出。

图T6.2

(三)在图6.3用CMOS反相器组成的施密特触发器电路中,若R1=50KΩ,R2=100KΩ,VDD=5V,VTH=0.5VDD,试求电路的转换电平VT+,VT-以及回差电压ΔVT.

图6.3

(四)试说明单稳态触发器的工作特点和主要用途。

(五)试判断在图T6.5所使得单稳态触发器电路中,为加大输出脉冲宽度所采取得下列措施哪些是对的,哪些失措的。

如果是对的,在()内打√;如果失措的,在()内打×;

(1)加大Rd();

(2)减小R();(3)加大C();(4)提高VDD();(5)增加输入出发脉冲的脉冲的宽度()。

图6.5

(六)在图T6.6所使的对称式多谐振荡器电路中,是判断为提高振荡频率所采取得下列措施哪些是对的,哪些是错的。

如果是对的,在()内画√;如果是错的,在()内画×:

(1)加大电容C的电容量();

(2)见效电阻R的阻值;(3)提高电源电压()。

图6.6

(七)图T6.7是由同样的与非门结成的换行振荡器。

今测得输出信号的重复频率位10KHZ,是求每个门的平均传输延迟时间。

假定所有与非门接成的环形振荡器,今测得输出信号的重复频率位10MHZ,是求每个门的平均传输延迟时间。

假定所有与非门的传输延迟时间相同,而且tPHL=tPLH=tpd。

图6.7

(八)试画出用555定时器组成施密特触发器,单稳态触发器和多谐振荡器时电路的连接图。

集成数模转换器和模数转换器

(一)在图8.2.1所示的权电阻网络D/A转换器中,若取VREF=5V,试求当输入数字量为d3d2d1d0=0101时输出电压的大小。

(二)在图8.2.3给出的倒T形电阻网络D/A转换器中,若取VREF=-8V,试计算当d3﹑d2﹑d1﹑d0每一位输入代码分别为1时在输出端所产生的模拟电压值。

(三)在图8.2.5由CB7520所组成的D/A转换器中,已知VREF=-10V,试计算当输入数字量从全0变到全1时输出电压的变化范围。

如果想把输出电压的变化范围缩小一半,可以采取那些方法?

(四)影响D/A转换器精度的主要因素有哪些?

(五)D/A转换器的电路结构有哪些类型,各有和优缺点?

(六)什么是量化误差?

它是怎样产生的?

(七)若A/D转换器(包括取样-保持电路)输入模拟电压信号的最高变化频率为10KHz,试说明取样频率的下限是多少?

完成一次A/D转换器所用时间的上限是多少?

(八)说明影响A/D转换器精度的主要因素有哪些?

(九)比较并联型A/D转换器﹑逐次渐近型A/D转换器和双积分型A/D转换器的优缺点,指出它们各适于在哪些情况下采用。