现代微机原理与接口技术作业答案Word格式文档下载.docx

《现代微机原理与接口技术作业答案Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《现代微机原理与接口技术作业答案Word格式文档下载.docx(26页珍藏版)》请在冰豆网上搜索。

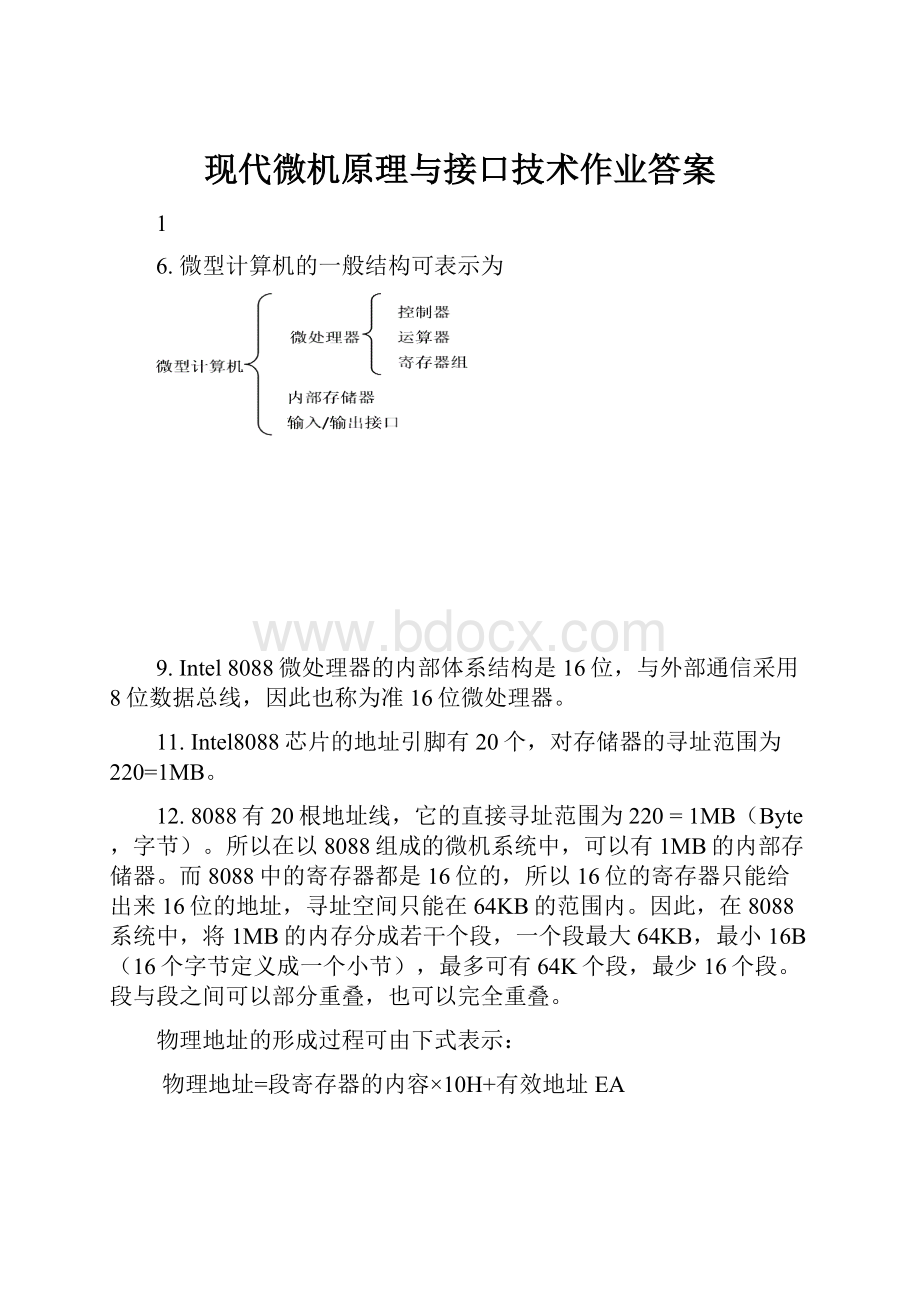

ADDR,9

MOVAX,W

SUBAX,X

SUBAX,R

(3)MOVAX,W

IMULX

ADDY,6

IDIVY

MOVR,DX

(4)假定运算过程中均不超过16位。

MOVAX,W

CWD

MOVBX,5

IDIVBX

IMULY

MOVBX,2

IMULBX

MOVZ,AX

11.解:

NOTAX

NOTDX

ADDAX,1

ADCDX,0

12.解:

(1)MOVAL,S

SUBAL,6

DAS

ADDAL,V

DAA

MOVU,AL

(2)MOVAL,X

ADDAL,W

MOVBL,AL

MOVAL,Z

SUBAL,V

XCHGAL,BL

SUBAL,BL

13.解:

MOVCL,4另解:

movcx,4

SHRAX,CLagain:

shrdx,1

MOVBL,DLrcrax,1

SHRDX,CLloopagain

SHLBL,CL

ORAH,BL

14.解:

MOVBYTEPTR[BP],20H;

字节操作,20H→(58200H),

MOVWORDPTR[BX],2000H;

字操作,2000H→(22400H),即

00H→(22400H),20H→(22401H)

16.解:

90000H,9E1FFH,9E200H

17.解:

(1)错。

码段段址寄存器CS不能出现在指令中。

(2)错。

双操作数指令中两操作数不能同为存储器寻址方式。

(3)错。

IP是指令指针寄存器,它的内容是下一条要取出的指令的偏移地址,不能为用户所用,故不能出现在指令中。

(4)(5)错。

原因同

(1)。

(6)错。

IN为输入指令,不能使用BX,只能使用累加器AX或AL,接受端口上的数据信息。

指令中DX内存放16位端口地址。

(7)错。

数据类型不匹配,“BYTEPTR[BX]”指示目的操作数将存放在一个字节的存储器内,源操作数为立即数1000为字数据。

(8)错。

(9)错。

SI和DI都是变址寄存器,不能同时使用。

(10)错。

双操作数指令中目的操作数不能为立即数。

18.答:

见表1

表1题18答案

AX

BX

JB

JNB

JBE

JNBE

JL

JNL

JLE

JNLE

1F52

√

88C9

FF82

007E

58BA

020E

FFC5

FF8B

09A0

1E97

8AEA

FC29

D367

32A6

19.答:

见表2

表2题19答案

指令

CX

DX

LOOPL20

0004H

000BH

0000H

LOOPNEL20

LOOPEL20

0002H

3

参考答案:

1.

(1)1

(2)2(3)7(4)208(5)1(6)1(7)100(8)100

2.

(1)1004H

(2)3000H(3)14FEH(4)152EH

4.(A)=30

此程序的功能是,将键盘输入的小写字母转换成大写字母在屏幕上显示出来。

其流程图如下:

6.答:

其功能是,采用冒泡法将100个数据从大到小排序。

编程如下:

(1)不用串处理指令,程序段如下:

MOVSI,1000H

MOVDI,2000H

MOVCX,100

AGAIN:

MOVAX,[SI]

MOVWORDPTR[DI],AX

ADDSI,2

ADDDI,2

LOOPAGAIN

(2)用单个传送的串处理指令,程序段如下:

CLD

LODSW

STOSW

(3)用REP前缀与串处理指令配合,程序段如下:

REPMOVSW

8.解:

对于源区和目的区有重叠的数据快的搬运,应从数据快的底部开始,程序如下:

DATASEGMENT

ORG1000H

DATA1DB1,2,3,……,50DUP(?

)

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA,ES:

DATA

START:

MOVAX,DATA

MOVDS,AX

MOVES,AX

MOVCX,100

LEASI,DATA1+99

LEADI,DATA+149

STD

REPMOVSB

MOVAH,4CH

INT21H

CODEENDS

ENDSTART

9.解:

源程序如下:

datasegment

org0500H

buffer1dbx1,x2,x3,……,x100

org1000H

buffer2db100dup(?

dataends

stacksegmentparastack‘stack’

db100dup(?

stackends

codesegment

assumecs:

code,ds:

data,es:

data,ss:

stack

startprocfar

begin:

pushds

movax,0

pushax

movax,data

movds,ax

moves,ax

movax,stack

movss,ax

movcx,100

cld

leasi,buffer1

leadi,buffer2

again:

lodsb

cmpal,0

jestop

stosb

loopagain

stop:

ret

startendp

codeends

endbegin

datasegment

arraydbx1,x2,……x100

sum_edb2dup(0)

sum_odb2dup(0)

data

start:

movax,data

movds,ax

movsum_e,0

movsum_e+1,0

movsum_o,0

movsum_o+1,0

movcx,100

movbx,0

moval,array[bx]

testal,01h

jnzodd

addsum_e,al

adcsum_e+1,0

jmpshortaddr

odd:

addsum_o,al

adcsum_o+1,0

addr:

incbx

loopagain

movah,4ch

int21h

endstart

15.解:

dsegsegment

bufferdbx1,x2,……,x100

resultdb3dup(0)

dsegends

csegsegment

assumecs:

cseg,ds:

dseg

start:

movax,dseg

movds,ax

movcx,100

movsi,0

next:

moval,buffer[si]

cmpal,85

jbb85

incresult

b85:

cmpal,60

jbb60

incresult+1

b60:

incresult+2

addr:

incsi

loopnext

movah,4ch

csegends

5

8088有三种工作周期:

指令周期、总线周期和T状态(时钟周期)。

CPU执行一条指令的时间(包括取指令、指令译码和执行该指令所需的全部时间)称为一个指令周期。

把通过系统总线对存储器或I/O端口进行一次读/写操作过程所需的称为总线周期,T状态就是CLK时钟周期。

一个指令周期由若干个总线周期组成。

每个总线周期通常包含4个T状态,即Tl、T2、T3、T4。

2.答:

8088的基本总线周期由Tl、T2、T3、T44个T状态(即时钟周期)组成。

当访问的是慢速存储器或是外设接口,因其工作速度与CPU不能匹配,则应该插人等待周期Tw。

3.解:

时钟周期T状态是CLK频率的倒数,即T=;

本题T==10ns,那么一个基本的总线周期为40ns。

4.答:

(见例题解析5)

8.答:

一般外设及其接口的工作速度总是跟不上CPU的工作速度,所以8088的I/O读写总线周期中总是要插入等待周期Tw。

9.答:

在最大组态工作方式中,8288将8088CPU输出的状态信号、、的状态信号转换成CPU系统所需要的总线命令和总线控制信号;

对存储器和I/O端口进行读写的信号、对地址锁存器8282和总线收发器8286的控制信号,以及中断控制器8259的控制信号。

6

参考答案:

2.答:

存储器的技术指标有存储容量、存储速度、存储器可靠性和性能/价格比。

1)存储容量指存储器可以容纳的二进制信息量,以存储单元的总位数表示,通常也用存储器的地址寄存器的编址数与存储字位数的乘积来表示。

如某存储芯片的容量为2K×

8位,即表示其地址寄存器为11位,编址能力为211=2×

1024=2048=2K,一个存储字为8位,也经常记为2KB。

2)存储速度有关存储器的存储速度主要有两个时间参数:

(1)TA:

访问时间(AccessTime),从启动一次存储器操作,到完成该操作所经历的时间。

(2)TMC:

存储周期(MemoryCycle),启动两次独立的存储器操作之间所需的最小时间间隔。

(3)1/TMC:

最大传输率,表示每秒钟从存储器输入或输出信息的最大速率。

(4)W/TMC:

存储器数据传输带宽,表示每秒钟存储器能并行传输多少位信息,其中W为存储器的数据总线宽度,反映了存储器传送信息的吞吐能力。

3)可靠性存储器的可靠性用MTBF来衡量,MTBF越长,可靠性越高。

MTBF——平均故障间隔时间(MeanTimeBetweenFailures)。

4)性能/价格比这是一个综合性指标,性能主要包括存储容量、存储速度和可靠性。

对不同用途的存储器有不同的要求,例如,对高速缓冲存储器主要要求存储速度快,而对辅助存储器主要要求存储容量大。

单译码方式中,存储体排列成2n×

m的二维存储矩阵,地址译码器只有一个,译码器输出线称为字选线(简称字线),数据线称为位线,字线选择某个字的所有位。

例如地址线n=4,经地址译码器译码,可译出24=16个状态,分别对应16个字(存储单元)的地址。

当某一状态有效时,对应一条字线有效,则一个字的信息由输出缓冲器读出。

双译码方式中,采用一个2n位的X-Y矩阵来代替单译码方式中的每一条位线,对于m位的存储器,共需采用m个X-Y矩阵。

为此需要提供X地址(行地址)、Y地址(列地址)及相应的X译码器(行译码器)、Y译码器(列译码器)。

若提供给X译码器的地址线有n1条,提供给Y译码器的地址线为n2条,当n=n1+n2时,则共可译出输出状态有

个,可见,在相同存储容量时,单译码方式和双译码方式所需地址线是相同的,只是双译码方式将地址线分成两组,分别进行译码,这使得地址译码器的输出线的数目大为减少。

例如,n=n1+n2=6+6=12,双译码输出的状态数为4096个,而译码输出线只需2×

26=128根。

12.答:

(1)地址线11条,数据线8条

(2)地址线12条,数据线8条

(3)地址线19条,数据线4条

(4)地址线16条,数据线1条

14.解:

可应用公式

芯片数=存储器系统的存储容量/芯片容量

(1)芯片数=16K×

8位/(0.5K×

4位)=64,需要5位地址作为片选地址译码。

(2)芯片数=64K×

8位/(2K×

15.解:

可列出地址线如下:

CBA

A19A18A17A16A15A14A13A12…………A0

10

1110010…………0

01110011…………1

可见图中RAM芯片的地址范围为72000H~73FFFH,其容量为213B,即8KB。

16.解:

(1)系统连线见题图红线部分。

(2)RAM3的地址范围为:

C000H~C3FFH。

17.解:

需要使用64片存储芯片,每两片组成一组,共32组,其数据线分别与数据总线的高4位和低4位连接。

存储系统的连接图如下(假定CPU地址线16位):

7

3.答:

两种I/O端口的编址方式:

统一编址方式(存贮器映象编址)和独立编址方式。

统一编址方式

特点:

I/O端口与系统中的存储器统一编址,每个I/O端口有一个存贮器地址,可以用访问存贮器的方法来访问I/O端口。

优点:

不需要专门的I/O指令及接口信号;

并且由于CPU对存贮器数据的处理的访内指令非常丰富,可以全部用于I/O操作,使I/O的功能更加灵活。

缺点:

真正的存储空间有所减少;

在程序中对I/O接口的操作不易看清,程序不够清晰。

独立编址方式

I/O端口和存贮器分别编址,各自都有完整的地址空间;

使用专用的I/O指令。

由于CPU使用专门的I/O指令及I/O控制信号来访问I/O端口,程序中对I/O端口的操作和对存贮器的操作一目了然。

I/O指令远不如访内指令丰富,所以编程不够灵活;

地址译码电路比较复杂。

CPU与外部设备之间数据传递有三种方式:

程序控制传递方式、DMA方式和I/O处理机方式。

I/O接口芯片的基本分类情况大致如下:

1)根据所用芯片的功能以及集成度高低的不同,可以将其区分为基本输入/输出接口电路和多功能可编程输入/输出接口电路两大类。

2)按照接口芯片所处理的信号类型区分,可以分为数字量输入/输出接口和模拟量输入/输出接口两大类。

3)按照接口芯片与外界进行数据传递方式的不同,又可以分为并行和串行接口两大类。

4)当接口芯片与微控制器(MCU)连接时,根据接口芯片与MCU的连接方式的不同还可以区分为并行总线方式和串行总线方式两大类。

9.解:

根据题意8255A的I/O端口地址的分配为

PAF4H

PBF5H

PCF6H

控制端口F7H

从题给电路看,开关K闭合,A点为低电平(0),开关K断开,A点为高电平

(1);

在此应用中8255A的PB和PC并未使用,而A组的应为工作方式0,PA作输入口使用,故控制字为10010000B,即90H。

程序段应先对8255A进行初始化,进行控制字的设置,然后从PA输入开关K的状态,依其状态确定2040H存储单元的内容。

程序如下:

MOVAL,90H

OUT0F7H,AL

INAL,0F4H

TESTAL,80H

JZON

OFF:

MOVBYTEPTR[2040H],0FFH

JMPEXIT

ON:

MOVBYTEPTR[2040H],00H

EXIT:

HLT

10.解:

根据要求解题如下:

(1)需使用地址译码器,如74LS138,连线如下:

(2)8255A的各端口的地址如下:

PA280H

PB281H

PC282H

控制口283H

(3)方式控制字为:

10010101B,即95H。

(4)当打印机的(连向8255A的PC2)负脉冲时,表示表示可以接受8255A送来的下一个数据,8255A向CPU发中断请求INTR信号,CPU如响应中断,则进入中断服务程序,向打印机输送下一个字符。

假定送打印机的字符存放在寄存器DL中,查询方式下输出一个字符至打印机的程序段如下:

主程序:

MOVAL,95H;

初始化8255A

MOVDX,0283H

OUTDX,AL

STI;

开中断

WAITT:

JMPWAITT

中断服务程序:

CLI

MOVDX,0282H

POLL:

INAL,DX

TESTAL,08H

JNZPOLL

MOVAL,DL

DECDX

OUTDX,AL

INCDX

INCDX

MOVAL,08H;

给负脉冲

OUTDX,AL;

NOP

MOVAL,09H

MOVAL,08H

IRET

16.答:

8253内部包含三个独立的结构功能完全相同的16位可预置的递减计数通道。

每个计数通道都有三条引线,其名称和作用如下:

CLK:

时钟输入端,计数脉冲或定时脉冲由该端引入。

GATE:

门控输入端,它是由外部引入的控制信号,用于启动或终止计数/定时。

OUT:

输出端,当计数至0时,输出中断信号。

21.答:

中断服务程序的入口地址叫作中断向量。

存放中断向量的内存区称为中断向量表,8088的中断向量表的地址范围为00000H~003FFH,共1KB。

题中的1CH是中断类型码,中断类型码乘以4即为该中断类型码所对应的中断向量存放单元的地址,那么对应于1CH的中断向量存放在地址00700H开始的4个字节单元中,即:

(00070H)=30H,(00071H)=20H,(00072H)=10H,(00073H)=51H

出师表

两汉:

诸葛亮

先帝创业未半而中道崩殂,今天下三分,益州疲弊,此诚危急存亡之秋也。

然侍卫之臣不懈于内,忠志之士忘身于外者,盖追先帝之殊遇,欲报之于陛下也。

诚宜开张圣听,以光先帝遗德,恢弘志士之气,不宜妄自菲薄,引喻失义,以塞忠谏之路也。

宫中府中,俱为一体;

陟罚臧否,不宜异同。

若有作奸犯科及为忠善者,宜付有司论其刑赏,以昭陛下平明之理;

不宜偏私,使内外异法也。

侍中、侍郎郭攸之、费