计算机组成原理第四版课后题答案五六章Word下载.docx

《计算机组成原理第四版课后题答案五六章Word下载.docx》由会员分享,可在线阅读,更多相关《计算机组成原理第四版课后题答案五六章Word下载.docx(11页珍藏版)》请在冰豆网上搜索。

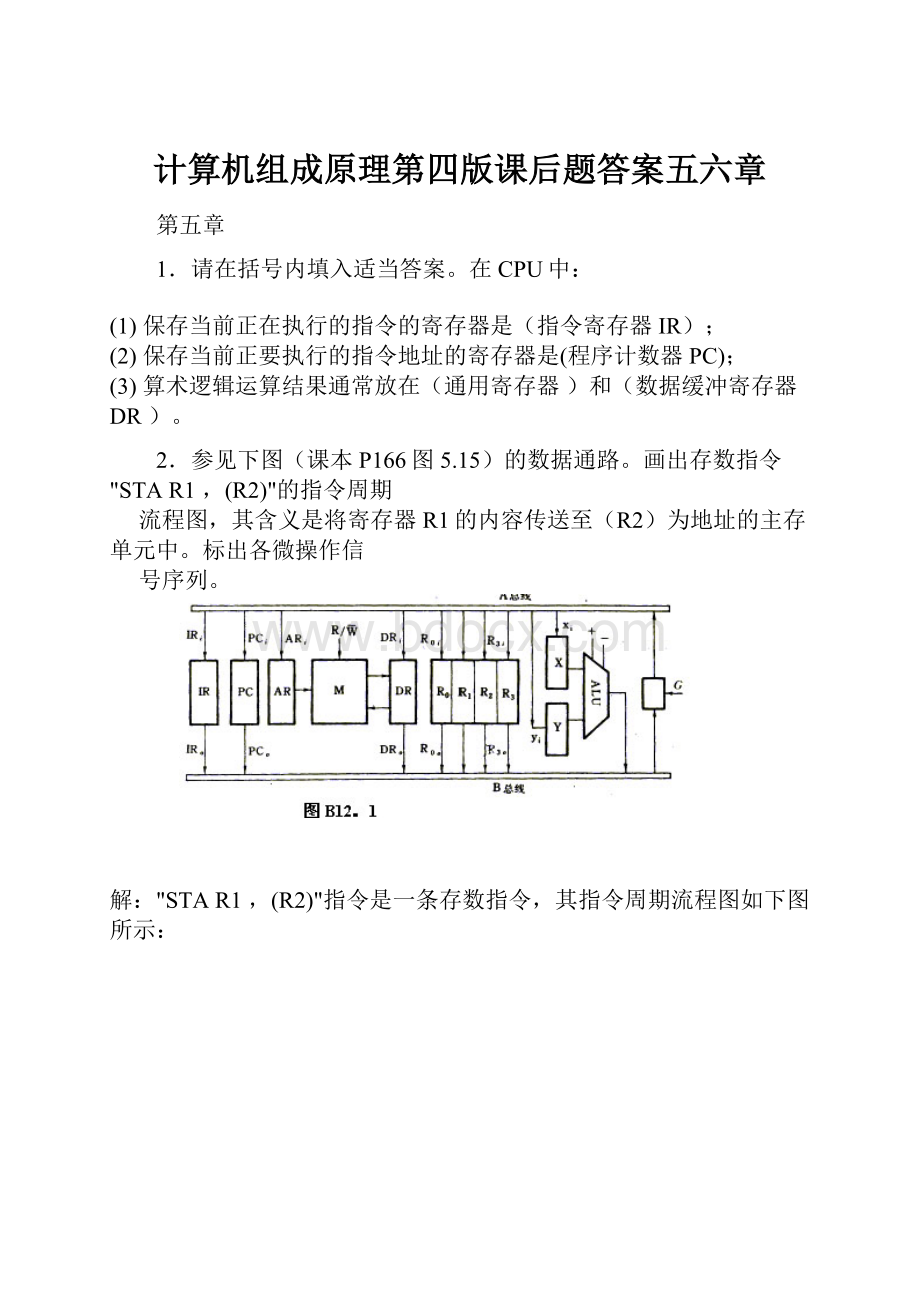

其含义是将(R3)为地址的主存单元的内容取至寄存器R0中,标出各微操作控制信号序列。

5.如果在一个CPU周期中要产生3个脉冲T1=200ns,T2=400ns,T3=200ns,试画出

时序产生器逻辑图。

节拍脉冲T1,T2,T3的宽度实际等于时钟脉冲的周期或是它的倍数,此时T1=T3=200ns,

T2=400ns,所以主脉冲源的频率应为f=1/T1=5MHZ。

为了消除节拍脉冲上的毛刺,环

型脉冲发生器可采用移位寄存器形式。

下图画出了题目要求的逻辑电路图和时序信号关系。

根据关

系,节拍脉冲T1,T2,T3的逻辑表达式如下:

T1=C1·

,T2=

,T3=

6.假设某机器有80条指令,平均每条指令由4条微指令组成,其中有一条取指微指令是所有指

令公用的。

已知微指令长度为32位,请估算控制存储器容量。

微指令条数为:

(4-1)×

80+1=241条

取控存容量为:

256×

32位=1KB

7.某ALU器件使用模式控制码M,S3,S2,S1,C来控制执行不同的算术运算和逻辑操作。

下表列出各条指令所要求的模式控制码,其中y为二进制变量,F为0或1任选。

试以指令码(A,B,H,D,E,F,G)为输入变量,写出控制参数M,S3,S2,S1,C的逻

辑表达式。

M=G

S3=H+D+F

S2=1

C=H+D+(E+F)y

8.某机有8条微指令I1-I8,每条微指令所包含的微命令控制信号如下表所示。

a-j分别对应10种不同性质的微命令信号。

假设一条微指令的控制字段为8位,请安排微指 令的控制字段格式。

经分析,(e,f,h)和(b,i,j)可分别组成两个小组或两个字段,然后进行译码,可得六个

微命令信号,剩下的a,c,d,g四个微命令信号可进行直接控制,其整个控制字段组成如

下:

11.已知某机采用微程序控制方式,其控制存储器容量为512×

48(位)。

微程序可在整个控

制存储器中实现转移,可控制微程序转移的条件共4个,微指令采用水平型格式,后继微

指令地址采用断定方式。

请问:

(1)微指令中的三个字段分别应为多少位?

(2)画出围绕这种微指令格式的微程序控制器逻辑框图。

(l)假设判别测试字段中每一位作为一个判别标志,那么由于有4个转移条件,故该字段为4位;

又因为控存容量为512单元,所以下地址字段为9位,。

微命令字段则是:

(48-4-9)=35位。

(2)对应上述微指令格式的微程序控制器逻辑框图如下图所示。

其中微地址寄存器对应下地址

字,P字段即为判别测试字段,控制字段即为微命令字段,后两部分组成微指令寄存器。

地 址转移逻辑的输入是指令寄存器的OP码、各种状态条件以及判别测试字段所给的判别标志

(某一位为1),其输出用于控制修改微地址寄存器的适当位数,从而实现微程序的分支转移 (此例微指令的后继地址采用断定方式)。

12.今有4级流水线分别完成取值、指令译码并取数、运算、送结果四步操作,

今假设完成各步操作的时间依次为100ns,100ns,80ns,50ns。

请问:

(1)流水线的操作周期应设计为多少?

(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么第二条指令要

推迟多少时间进行。

(3)如果在硬件设计上加以改进,至少需推迟多少时间?

(1)流水线的操作时钟周期t应按四步操作中最长时间来考虑,所以t=100ns;

(2)两条指令发生数据相关冲突情况:

:

ADDR1,R2,R3;

R2+R3→R1

SUBR4,R1,R5;

R1-R5→R4

两条指令在流水线中执行情况如下表所示:

ADD指令在时钟4时才将结果写入寄存器R1中,但SUB指令在时钟3时就需读寄存器R1了,显然发生

数据相关,不能读到所需数据,只能等待。

如果硬件上不采取措施,第2条指令SUB至少应推迟2个

操作时钟周期,即t=2×

100ns=200ns;

(3)如果硬件上加以改进(采取旁路技术),这样只需推迟1个操作时钟周期就能得到所需数据,

即t=100ns。

15.用定量描述法证明流水计算机比非流水计算机具有更高的吞吐率。

衡量并行处理器性能的一个有效参数是数据带宽(最大吞吐量),它定义为单位时间内可以产生

的最大运算结果个数。

设P1是有总延时T1的非流水处理器,故其带宽为1/T1。

又设Pm是相当于P1m段流水处理器延迟时 间Tr,故Pm的带宽为1/(Tc+Tr)。

如果Pm是将P1划分成相同延迟的若干段形成的,则T1≈mTc因

此P1的带宽接近于1/mTc,由此可见,当mTc>

Tc+Tr满足时,Pm比P1具有更大的带宽。

16.流水线中有三类数据相关冲突:

写后读(RAW)相关;

读后写(WAR)相关;

写后写

(WAW)相关。

判断以下三组指令各存在哪种类型的数据相关。

(1)I1LADR1,A;

M(A)→R1,M(A)是存储器单元

I2ADDR2,R1;

(R2)+(R1)→R2

(2)I3ADDR3,R4;

(R3)+(R4)→R3

I4MULR4,R5;

(R4)×

(R5)→R4

(3)I5LADR6,B;

M(B)→R6,M(B)是存储器单元

I6MULR6,R7;

(R6)×

(R7)→R6

(1)写后读(RAW)相关;

(2)读后写(WAR)相关,但不会引起相关冲突;

(3)写后读(RAW)相关、写后写(WAW)相关

17.参考教科书图5.42所示的超标量流水线结构模型,现有如下6条指令序列:

I1LADR1,B;

M(B)→R1,M(B)是存储器单元

I2SUBR2,R1;

(R2)-(R1)→R2

I3MULR3,R4;

(R3)×

(R4)→R3

I4ADDR4,R5;

(R4)+(R5)→R4

I5LADR6,A;

M(A)→R6,M(A)是存储器单元

I6ADDR6,R7;

(R6)+(R7)→R6

请画出:

(1)按序发射按序完成各段推进情况图。

(2)按序发射按序完成的流水线时空图。

(1)

(2)

第六章

1.比较单总线、双总线、三总线结构的性能特点。

3.用异步通信方式传送字符"

A"

和"

8"

,数据有7位,偶校验1位。

起始位1位,

停止位l位,请分别画出波形图。

字符A的ASCII码为41H=1000001B;

字符8的ASCII码为38H=0111000B;

串行传送波形图为:

注:

B:

起始位

C:

校验位

S:

停止位

8.同步通信之所以比异步通信具有较高的传输频率,是因为同步通信____。

A.不需要应答信号;

B.总线长度较短;

C.用一个公共时钟信号进行同步;

D.各部件存取时间比较接近。

C

9.在集中式总线仲裁中,____方式响应时间最快,____方式对____最敏感。

A.菊花链方式B.独立请求方式C.电路故障D.计数器定时查询方式

BAC

10.采月串行接口进行7位ASCII码传送,带有1位奇校验位,l位起始位和1位停止位,当传输率为9600波特时,字符传送速率为____。

A.960B.873.C.1372D.480

A

11.系统总线中地址线的功能是______。

A.选择主存单元地址

B.选择进行信息传输的设备

C.选择外存地址

D.指定主存和I/O设备接口电路的地址

D

12.系统总线中控制器的功能是______。

A.提供主存、I/O接口设备的控制信号和响应信号

B.提供数据信息

C.提供时序信号

D.提供主存、I/O接口设备的响应信号

14.PCI是一个与处理器无关的_____,它采用____时序协议和____式仲裁策略,并具有____能力。

A.集中B.自动配置C.同步D.高速外围总线

DCAB

15.PCI总线的基本传输机制是____传送。

利用____可以实现总线间的____传送,使所有的存取都按CPU的需要出现在总线上。

PCI允许____总线____工作。

A.桥B.猝发式C.并行D.多条E.猝发式

BACDE

17.PCI总线中三种桥的名称是什么?

桥的功能是什么?

PCI总线有三种桥,即HOST/PCI桥(简称HOST桥),PCI/PCI桥和PCI/LAGACY桥。

在PCI总线体系结构中,桥起着重要作用:

(1)接两条总线,使总线间相互通信;

(2)是一个总线转换部件,可以把一条总线的地址空间映射到另一条总线的地址空间上,

从而使系统中任意一个总线主设备都能看到同样的一份地址表。

(3)利用桥可以实现总线间的卒发式传送。

19.总线的一次信息传送过程大致分哪几个阶段?

若采用同步定时协议,请画出

读数据的同步时序图。

分五个阶段:

请求总线、总线仲裁、寻址(目的地址)、信息传送、状

态返回(错误报告)。

读数据的同步时序图为:

20.某总线在一个总线周期中并行传送8个字节的数据,假设一个总线周期等于一个总线时钟周期,总线时钟频率为70MHZ,求总线带宽是多少?

设总线带宽用Dr表示,总线时钟周期用T=1/f表示,一个总线周期传送的数据量用D表示,

根据定义可得:

Dr=T/D=D×

1/f=8B×

70×

106/s=560MB/