S接线器及T接线器Word下载.docx

《S接线器及T接线器Word下载.docx》由会员分享,可在线阅读,更多相关《S接线器及T接线器Word下载.docx(7页珍藏版)》请在冰豆网上搜索。

空间接线器用来完成对传送同步时分复用信号的不同复用线之间的交换功能,而不能改变其时隙位置,可简称为S接线器。

而对同步时分复用信号来说,用户信息固定在某个时隙里传送,一个时隙就对应一条话路。

因此,对用户信息的交换就是对时隙里容的交换,即时隙交换。

可以说,同步时分复用信号交换实现的关键是时隙交换,时间接线器用来完成在一条复用线上时隙交换的根本功能,可以简称为T接线器。

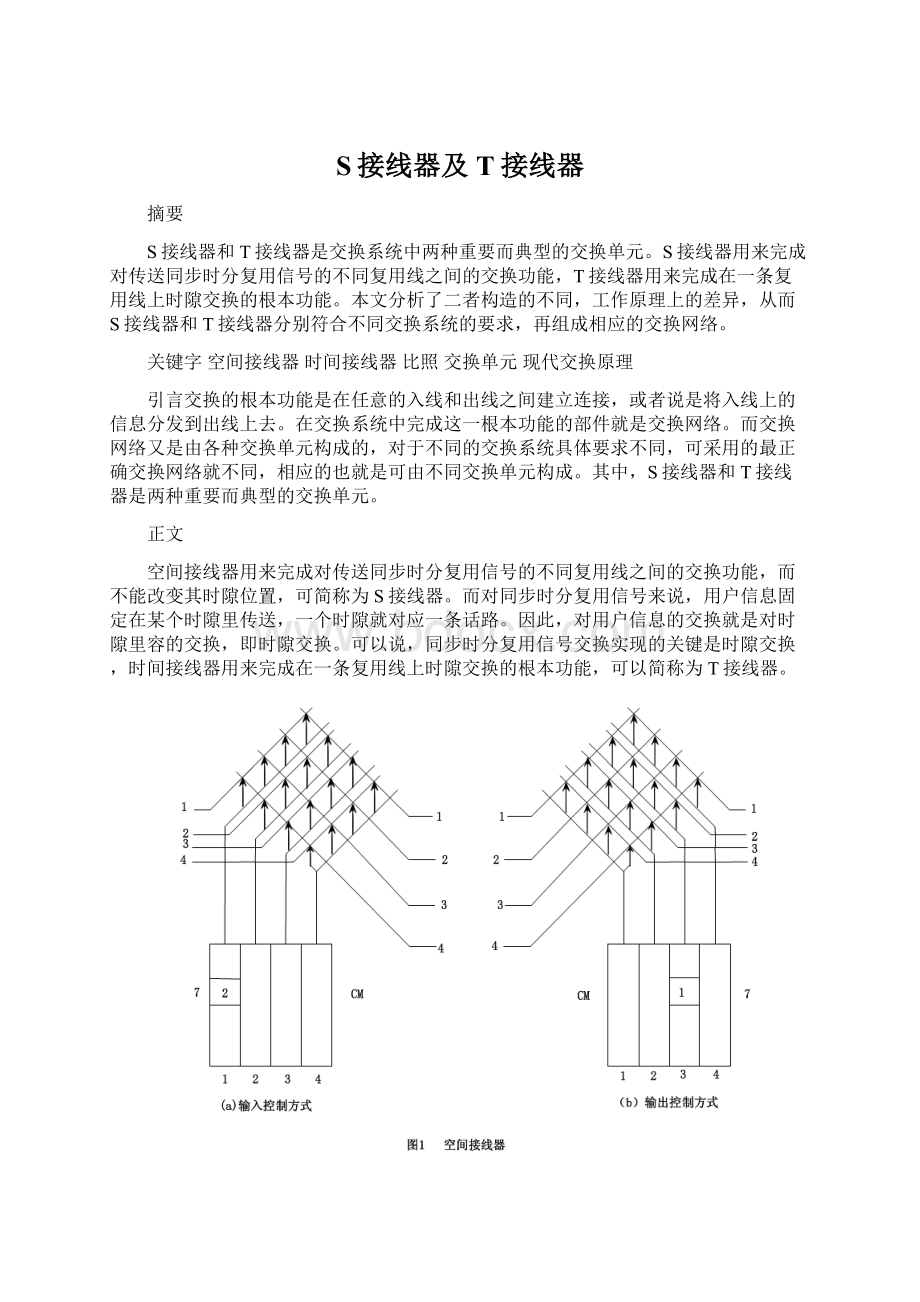

从构造上看,空间接线器由电子穿插矩阵和控制存储器〔CM〕构成,图1所示为基于两种控制方式的空间接线器。

它包括一个4×

4的电子穿插矩阵和对应的控制存储器。

4×

4的穿插矩阵有4条输入复用线和4条输出复用线,每条复用线上传送由假设干个时隙组成的同步时分复用信号,任一条输入复用线可以选通任一条输出复用线。

这里我们说成复用线,而不一定是一套32路的PCM系统,是因为实际上还要将各个PCM系统进一步复用,使一条复用线上具有更多的时隙,以更高的码率进入电子穿插矩阵,从而提高性能。

因为每条复用线上具有假设干个时隙,也即每条复用线上传送了假设干个用户的信息,所以,输入复用线与输出复用线应在某一个指定时隙接通。

例如,第1条输入复用线的第1个时隙可以选通第2个输出复用线的第1个时隙,它的第2个时隙可能选通第3条输出复用线的第2个时隙,它的第3个时隙可能选通第1条输出复用线的第3个时隙,等等。

所以说,空间接线器不进展时隙交换,而仅仅实现同一时隙的空间交换。

当然,对应于一定出入线的各个穿插点是按复用时隙而高速工作;

而在这个意义上,空间接线器是以时分方式工作的。

各个穿插点在哪些时隙应闭合,在哪些时隙应断开,这决定于处理机通过控制存储器所完成的选择功能。

如图1〔a〕所示,对应于每条入线有一个控制存储器〔CM〕,用于控制该入线上每个时隙接通哪一条出线。

控制存储器的地址对应时隙号,其容为该时隙所应接通的出线编号,所以其容量等于每一条复用线上时隙数,每个存储单元的字长,即比特数那么决定于出线地址编号的二进制码位数。

例如,假设穿插矩阵是32×

32,每条复用线有512个时隙,那么应有32个控制存储器,每个控制存储器有512个存储单元,每个单元的字长为5比特,可选择32条出线。

图1〔b〕与〔a〕根本一样,不同的是这时每个控制存储器对应一条出线,用于控制该出线在每个时隙接通哪一条入线。

所以,控制存储器的地址仍对应时隙号,其容为该时隙所应接通的入线编号,字长为入线地址编号的二进制码位数。

电子穿插矩阵在不同时隙闭合和断开,要求其开关速度极快,所以它不是普通的开关,通常,它是电子选择器组成的。

电子选择器也是一种多路选择交换器,只不过,其控制信号来源于控制存储器。

图1〔b〕中的4×

4电子穿插矩阵的构成可以表示为图2。

由图可知,4×

4电子穿插矩阵可采用4片4选1的选择芯片,各负责一条输出复用线。

每片的4条输入复用线按输入线号复接起来,形成4条输入复用线。

4个控制存储器对应4条出线,每个控制存储器存储2个入线地址,并输出至相应选择器作为控制信号。

选择器的选通端决定选择器是否工作,以免选择器将控制存储器无输入误认为输出0,而将此时的入线与出线0接通。

构造上,时间接线器采用缓冲存储器暂存话音的数字信息,并用控制读出或控制写入的方法来实现时隙交换,因此,时间接线器主要由话音存储器〔SM〕和控制存储器〔CM〕构成,如图3所示。

其中,话音存储器和控制存储器都采用随机存取存储器〔RAM〕构成。

话音存储器用来暂存数字编码的话音信息。

每个话路时隙有8位编码,故话音存储器的每个单元应至少具有8比特。

话音存储器的容量,也就是所含的单元数应等于输入复用线上的时隙数,假定输入复用线上有512个时隙,那么话音存储器要有512个单元。

控制存储器的容量通常等于话音存储器的容量,每个单元所存储的容是由处理机控制写入的。

在图3中,控制存储器的输出控制话音存储器的读出地址。

如果要将话音存储器输入TS49的容a在TS58中输出,可在控制存储器的第58单元中写入49。

现在来观察完成时隙交换的过程。

各个输入时隙的信息在时钟控制下,依次写入话音存储器的各个单元,时隙1的容写入第1个存储单元,时隙2的容写入第2个存储单元,以此类推。

控制存储器在时钟控制下依次读出各单元容,读至第58单元时〔对应于话音存储器输出TS58〕,其容49用于控制话音存储器在输出TS58读出第49单元的容,从而完成了所需的时隙交换。

输入时隙选定了输出时隙后,由处理机控制写入控制存储器的容在整个通话期间是保持不变的。

于是,每一帧都重复以上的读写过程,输入TS49的话音信息,在每一帧中都在TS58中输出,直到通话终止。

显然,控制存储器每单元的比特数决定于话音存储器的单元数,也就是决定于复用线上的时隙数。

应该注意到,每个输入时隙都对应着话音存储器的一个单元数,这意味着由空间位置的划分而实现时隙交换,从这个意义上说,时间接线器带有空分的性质,是按空分方式工作。

S接线器工作原理方面,参考图1,空间接线器有两种工作方式,是按照存储器配置的不同而划分的。

①按输入线配置的称为输入控制方式〔见图1〔a〕〕

②按输出线配置的称为输出控制方式〔见图1〔b〕〕

在图1〔a〕中,第1个存储器第7单元由处理机控制写入了2。

第7单元对应于第7个时隙,当每帧的第7个时隙到达时,读出第7单元中的2,表示在第7个时隙应将第1条入线与第2条出线接通,也就是第1条入线与第2个出线的穿插点在第7时隙中应该接通。

在图1〔b〕中,如果仍然要使第1输入线与第2输出线在第7时隙接通,应由处理机第2个控制存储器的第7单元写入输入线1,然后,在第7个时隙到达时,读出第7单元中的1,控制第2条出线与第1条入线的穿插点在第7时隙接通。

在同步时分复用信号的每一帧期间,所有控制存储器的各单元的容依次读出,控制矩阵中各个穿插点的通断。

输出控制方式有一个优点:

某一输入线上的某一个时隙的容可以同时在几条输出线上输出,即具有同步和播送功能。

例如,在4个控制存储器的第K个单元中都写入了输入线i,使得输入线i的第K个时隙中的容同时在输出线1~4上输出,而在输入控制方式时,假设在多个控制存储器的一样单元中写入一样的容,只会造成重接或出线冲突,这对于正常的通话是不允许的。

T接线器工作原理方面就控制存储器对话音存储器的控制而言,可有两种控制方式:

①顺序写入,控制输出,简称“输出控制〞。

②控制写入,顺序写出,简称“输入控制〞。

图4〔a〕所示为输出控制方式,即话音存储器的写入是由时钟脉冲控制按顺序进展,而其读出要受控制存储器的控制,由控制存储器提供写出地址。

控制存储器那么只有一种工作方式,它所提供的读出地址是由处理机控制写入,按顺序读出的。

例如,当有时隙容a需要从时隙i交换到时隙j时,在话音存储器的第i个单元顺序写入容a,由处理机控制在控制存储器的第j个单元写入地址i作为话音存储器的输出地址。

当第j个时隙到达时,从控制存储器中去取出输出地址i,从话音存储器第i个单元中取出容a输出,完成交换。

图4〔b〕所示为输入控制方式,即话音存储器是控制写入,顺序读出的,其工作原理与输出控制方式相似,不同之处不过是控制存储器用于控制话音存储器的写入。

当第i个输入时隙到达时,由于控制存储器第i个单元写入的容是j,作为话音存储器的写入地址,就使得第i个输入时隙中的话音信息写入话音存储器的第j个单元。

当第j个时隙到达时,话音存储器按顺序读出容a,完成交换。

实际上,在一个时钟脉冲周期,由RAM构成的话音存储器和控制存储器都要完成写入和读出两个动作,这是由RAM本身提供的读、写控制线控制,在时钟脉冲的正、负半周分别完成的。

特别的是,T接线器还存在时延。

时间接线器的容量等于话音存储器的容量及控制存储器的容量,也即等于输入复用线上的时隙数,一个输入N路复用信号的时间接线器就相当于一个N×

N交换单元。

因此,增加N就可以增加交换单元的容量。

当然,在输入复用信号帧长确定时,N越大,存储器读、写数据的速度就要越快,所以,N的增加是有限制的。

假设单路信号的速率为v,采用的存储器为双向数据总线,数据总线的宽度〔即每次存储数据的比特数〕B比特,需要时间t,那么有下述关系成立

2×

N×

v=B÷

t

由上式可知,增加时间接线器的容量的方法包括:

①使用快速的存储器。

这相当于减少上式中的t;

②增加存储器数据总线的宽度,即增加上式中的B;

③使用单项数据总线的存储器。

这相当于去掉上式中的因子2。

因为经过时间接线器进展的是时隙交换,所以每个时隙的信号都会在存储器中产生大小不等的时延。

同步时分复用信号经过一个时间接线器的时延包括:

①信号进展串并交换时的时延。

这项延时与存储器的数据总线宽度成正比。

因此,在通过增加存储器数据总线的宽度来增加时间接线器容量时,也同时增加了信号经过时间接线器的时延。

②在存储器中的时延。

因为时隙互换的关系,所以每个时隙的信号在经过存储器后都会有大小不等的延迟。

延迟最小的情况发生在一个时隙的信号在写入存储器后立即被读出时,延迟最大的情况发生在一个时隙的信号在写入存储器后要等待一帧后才可读出时。

因为有各种各样可能的时隙互换方式,所以时间接线器需要等到一帧中各时隙的信号都到齐后才能输出,假设时间接线器在一帧各时隙的信号都到齐后经过τ时间后开场输出,那么信号经过时间接线器的平均时延为

T=τ+NW

其中,N是每帧中的时隙数,W是一个时隙的时间长度。

但应注意,各时隙中的单路信号经过的时延各不一样。

结论

T接线器是以空间位置的划分来实现时隙交换,而S接线器却以时分方式完成复用线之间的空间交换。

由于构造和工作原理的不同,所以S接线器和T接线器有不同的应用。

而在不同的应用中,两者的输出和输入控制方式又有所区别。

如在典型的TST网络中,两侧为T接线器,中间一级为S接线器。

其中,S接线器采用输出控制方式,输入侧T接线器采用顺序写入、控制读出方式,输出侧T接线器采用控制写入、顺序读出方式。

参考文献

1金惠文,建亚,纪红,春燕.现代交换原理〔第二版〕电子工业,2007