逐次逼近寄存器型ADC设计报告最新Word文档格式.docx

《逐次逼近寄存器型ADC设计报告最新Word文档格式.docx》由会员分享,可在线阅读,更多相关《逐次逼近寄存器型ADC设计报告最新Word文档格式.docx(24页珍藏版)》请在冰豆网上搜索。

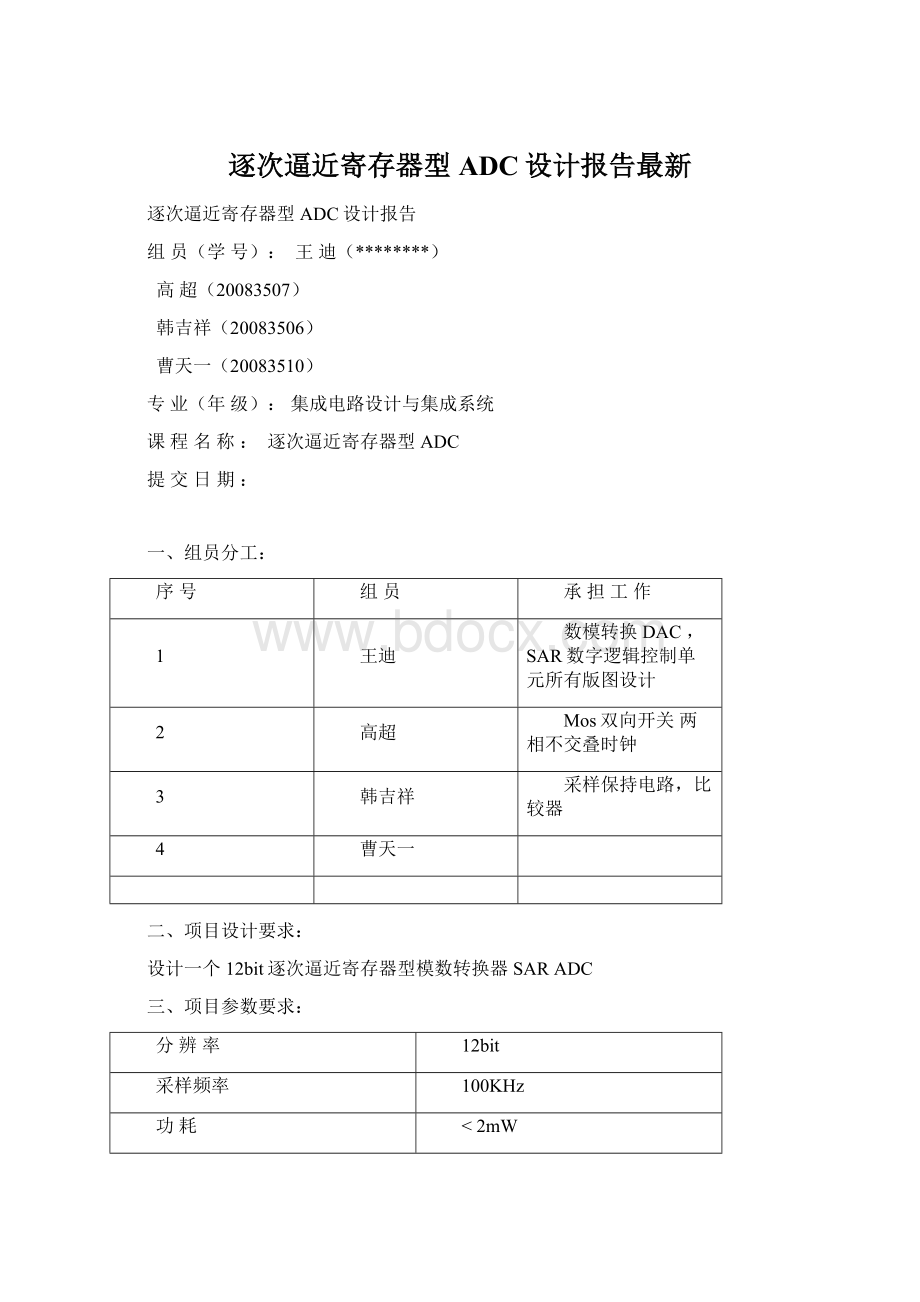

采样频率

100KHz

功耗

<

2mW

电源电压

2.5V

面积

3mm2

工作温度

0~80℃

工艺技术

0.25um

四、项目设计内容:

1.逐次逼近寄存器型模数转换器(SARADC)整体结构:

2.逐次逼近寄存器型模数转换器(SARADC)的特点及应用:

特点:

中级转换速度,低功耗,高精度,小尺寸

应用:

便携式仪表、笔输入量化器,工业控制和数据/信号采集器等

3.逐次逼近寄存器型模数转换器(SARADC)工作原理:

SARADC其基本结构如图1所示,包括采样保持电路(S/H)、比较器(COMPARE)、数/模转换器(DAC)、逐次逼近寄存器(SARREGISTER)和逻辑控制单元(SARLOGIC)。

模拟输入电压VIN由采样保持电路采样并保持,为实现二进制搜索算法,首先由SARLOGIC控制N位寄存器设置在中间刻度,即令最高有效位MSB为“1”电平而其余位均为“0”电平,此时数字模拟转换器DAC输出电压VDAC为0.5VREF,其中VREF为提供给ADC的基准电压。

由比较器对VIN和VDAC进行比较,若VIN>

VDAC,则比较器输出“1”电平,N位寄存器的MSB保持“1”电平;

反之,若VIN<

VDAC,则比较器输出“0”电平,N位寄存器的MSB被置为“0”电平。

一次比较结束后,MSB被置为相应的电平,同时逻辑控制单元移至次高位并将其置“1”,其余位置“0”,进行下一次比较,直至最低有效位LSB比较完毕。

整个过程结束,即完成了一次模拟量到数字量的转换,N位转换结果存储在寄存器内,并由此最终输出所转化模拟量的数字码。

4.逐次逼近寄存器型模数转换器(SARADC)各子模块设计:

●子模块1:

比较器(COMPARE)

(1)电路结构:

(给出电路结构图)

(2)工作原理:

电路为两级运算放大器,第一级是电流镜做负载的差分放大器。

第二级是电流漏做负载的反相放大器,M8管和M5构成一个电流镜结构,由M8给M5镜像电流作为第一级放大器的尾电流。

M8和M7也是一个电流镜结构,其功能也是为M7提供个横定的电流。

该电路实现的功能是vin2与vin1做比较,若vin2>

vin1则vout输出高点平,若vin2<

vin1则输出低电平。

(3)参数设定:

管子名称

管子类型

宽(um)

长(um)

M1

NMOS

M2

M3

PMOS

5

M4

M5

M6

10

M7

2.4

M8

14

(4)仿真网表:

功能仿真网表:

*Subcktinverter

.lib'

mix025_1.l'

tt

Vddvdd02.5V

.paramcom=1.25v

xinvin1in2voutvddinv

.subcktinvin1in2voutvdd

vin_n1in10com

vin_n2in20pwl00v20u2.5v

ibiasvddvbias30u

M1vm1in1vn1gndnchL=1uW=3u

M2vf1in2vn1gndnchL=1uW=3u

M3vm1vm1vddvddpchL=1uW=5u

M4vf1vm1vddvddpchL=1uW=5u

M5vn1vbiasgndgndnchL=1uW=3u

M6voutvf1vddvddpchL=1uW=10u

M7voutvbiasgndgndnchL=1uW=2.4u

M8vbiasvbiasgndgndnchL=1uW=14u

Ccvf1020fF

CLvout020fF

.ends

.tran1n20u

.printtranV(vout)V(in2)v(in1)

.end

精度仿真网表

vin_n2in20pwl01.2497v10u1.2503v

M7voutvbiasgndgndnchL=1uW=2.6u

.tran1n10u

.printtranV(vout)V(in2)V(in1)

传播延时网表:

vin_n2in20pulse(02.5v1n1n0.2u0.4u)

.tran1n1u

.printtranV(vout)V(in2,in1)

(4)仿真结果:

(要求给出仿真结果图,并对结果图中所显示的功能或结果数值进行说明)

功能仿真结果:

该图为比较器功能仿真图像,由图像可以看出,VOUT已经达到满量程了,并且实现了比较器的功能:

当vin2<

vin1时输出为低电平,当vin2>

vin1时输出为高电平。

精度仿真结果:

该图像为精度仿真结果图,从图中可以看出在我们设定的1.25V,在1.25V上下波动0.3mV(1.2497-1.2503V)之间输出波形发生了翻转,说明该比较器精度满足0.6mV的精度要求。

但是从输出波形在翻转时有一定的延迟。

传播延时仿真:

传播延时由输出图像翻转的50%的点与输入图像翻转的50%的点之间的时间差,他翻译的是比较器的速度,由图中可以得出传播延时约等于33ns。

(5)版图:

(要求在版图中标出该模块与外界连接的各端口名称,用标尺标出版图尺寸值)

●子模块2:

采样保持电路(S/H)

有CLK端输入选通脉冲,当clk处于高点平时传输门导通vin输入,电路处于采样阶段,当clk由高电平跳转到低电平后,传输门闭合,由于有保持电容的存在,是电路出于保持阶段。

(3)参数设定:

M9

4.5

.lib'

tt

vinin0sin1.251.25100k

Vkk0PULSE(02.500.1n0.1n1u5u)

Ccvf1vout3pF

CLvout03pF

C3in201pF

M1vm1voutvn1gndnchL=1uW=3u

M7voutvbiasgndgndnchL=1uW=3u

M9in2kin0nchL=1uW=4.5u

.tran10n40u

.printv(in)v(k)v(vout)

(5)仿真结果:

该采样保持电路采用高电平采样低电平保持,在几个采样周期内基本满足了采样的要求,采样频率为100KHz。

(6)版图:

●子模块3:

数模转换器DAC

采用的电荷按比例缩放的DAC中并没有清零开关,如果输出接到比较器那么电容在通断的过程中会自动放电清零,也就是说,输出端是一个封闭的区域的电荷量是不会变化的,产生的电压完全是外部因素产生的感应电压。

双向传输门中使用的PMOS和NMOS的所有参数均一样,宽长比为1:

2,12组电容的电容值是依次按比例增加的,剩余的一个电容的电容值和12组电容中最小的一个相等,因为DAC的输出电压为0-2.5V,所以VREF可以连接到GND,VREF可以连接到VDD,调节VREF和VREF可以调节DAC的输出范围和精度,比如,VREF加载1V,VREF加载2V,那么输出电压为1-3V。

●子模块4:

其他子模块(如:

MOS开关、两相不交叠时钟、运算放大器、偏置电路、逻辑门电路等等)

MOS双向开关:

当输入D是1时,经过反相器输出为0,此时PMOS管导通NMOS管截止,输出为IN。

当输入D是0时,经过反相器输出为1,此时NMOS管导通PMOS管截止,输出为0。

设反相器的PMOS的L=0.25u,W=2u,由于反相器的P管与N管尺寸比为2比1,则反相器的NMOS的L=0.25u,W=1u。

设MP2的L=0.25u,W=1u。

MN2的L=0.25u.W=1u。

仿真结果说明:

当输入D是高电平时,MP2管导通,输出为IN,IN为2.5v。

当输入为低电平时,MN2管导通,输出为0。

两相不交叠时钟:

输出端CLK1由输入CLK和另一个反馈来的输入经过三个反相器得出。

输出端CLK2由经过一个反相器的CLK输入端和反馈来的另一个输入端经过三个反相器得出。

反相器:

N管:

W=1uL=0.25uP管:

W=2uL=0.25u

与非门:

NMOS:

W=1uL=0.25uPMOS:

W=4uL=0.25u

.lib"

mix025_1.l"

.globalvdd

vdvdd02.5v

vclkclk0PULSE(02.500.1n0.1n0.05u0.1u)

.subcktinvinout

mp1outinvddvddpchw=4ul=0.25u

mn1outin00nchw=1ul=0.25u

.subcktnandin1in2out

mp1outin1vddvddpchw=2ul=1u

mp2outin2vddvddpchw=2ul=1u

mn1outin122nchw=1ul=0.5u

mn22in200nchw=1ul=0.5u

xinv1clkout1inv

xinv2out1out2inv

xinv3out2out3inv

xinv4out4out5inv

xinv5out5clk1inv

xinv6clkout6inv

xinv7out6out7inv

xinv8out8out9inv

xinv9out9clk2inv

xandout3clk2out4nand

xand1out7clk1out8nand

.tran0.1u2u

.printv(clk)v(clk1)v(clk2)

输入CLK与输出CLK1和CLK2的关系是,CLK1与CLK2不交叠的时钟输出。

时钟周期是0.1us。

即采样周期

(7)版图:

●子模块5:

SAR数字逻辑控制单元

(1)工作原理:

实现二进制搜索算法,完成逐次逼近的功能

(2)Verilog网表:

modulewangdi(clk,reset,ena,dout,dq,dcomp,count);

inputclk,reset,dcomp;

outputena;

output[3:

0]count;

output[11:

0]dout,dq;

reg[11:

reg[3:

0]count;

regena;

parameter

A0=4'

b0000,A1=4'

b0001,A2=4'

b0010,A3=4'

b0011,A4=4'

b0100,A5=4'

b0101,A6=4'

b0110,

A7=4'

b0111,A8=4'

b1000,A9=4'

b1001,A10=4'

b1010,A11=4'

b1011,A12=4'

b1100,A13=4'

b1101;

always@(posedgeclk)

if(reset)

begin

dout=12'

b000000000000;

count=4'

b0000;

end

else

case(count)

A0:

count=3'

b000;

dout=6'

b10000000;

if(ena)

begin

count<

=count+1;

elsebegin

dout=dout;

count=A0;

dq=dout;

A1:

dout[11]=dcomp;

dout[10]=1;

dout[9]=0;

dout[8]=0;

dout[7]=0;

dout[6]=0;

dout[5]=0;

dout[4]=0;

dout[3]=0;

dout[2]=0;

dout[1]=0;

dout[0]=0;

count=A2;

A2:

dout[11]=dout[11];

dout[10]=dcomp;

dout[9]=1;

count=A3;

A3:

dout[10]=dout[10];

dout[9]=dcomp;

dout[8]=1;

count=A4;

A4:

dout[9]=dout[9];

dout[8]=dcomp;

dout[7]=1;

count=A5;

A5:

dout[8]=dout[8];

dout[7]=dcomp;

dout[6]=1;

count=A6;

A6:

dout[7]=dout[7];

dout[6]=dcomp;

dout[5]=1;

count=A7;

A7:

dout[6]=dout[6];

dout[5]=dcomp;

dout[4]=1;

count=A8;

A8:

dout[5]=dout[5];

dout[4]=dcomp;

dout[3]=1;

count=A9;

A9:

dout[4]=dout[4];

dout[3]=dcomp;

dout[2]=1;

count=A10;

A10:

dout[3]=dout[3];

dout[2]=dcomp;

dout[1]=1;

count=A11;

A11:

dout[2]=dout[2];

dout[1]=dcomp;

dout[0]=1;

count=A12;

A12:

dout[1]=dout[1];

dout[0]=dcomp;

count=A13;

A13:

dout[11]=do