ChipScope9使用方法文档格式.docx

《ChipScope9使用方法文档格式.docx》由会员分享,可在线阅读,更多相关《ChipScope9使用方法文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

好了下面开始我们的旅程!

!

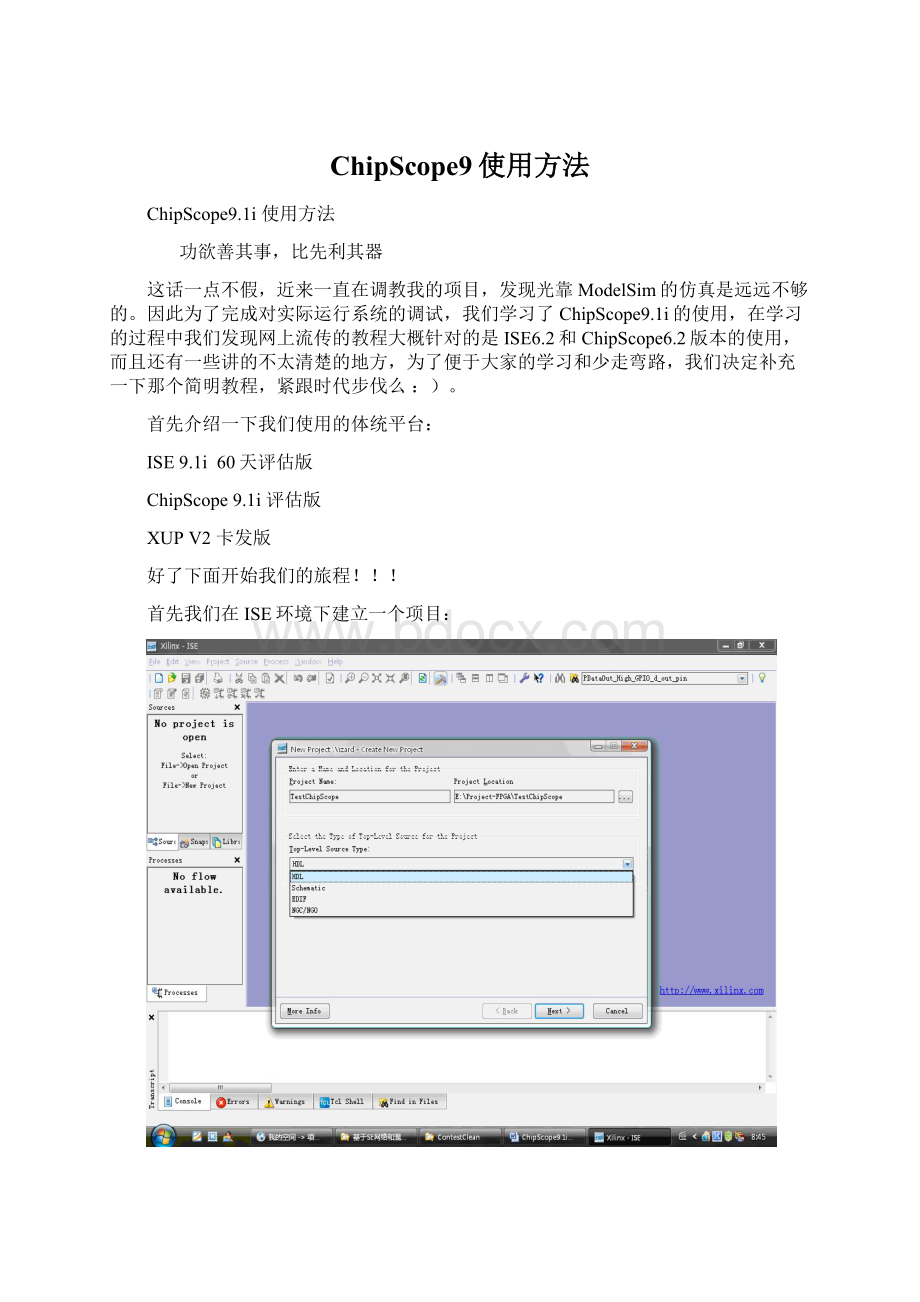

首先我们在ISE环境下建立一个项目:

在弹出的下拉列表里我们可以选择项目类型,这里我们可以选择两种:

一种是HDL,这样我们就可以在ISE下建立VHDL、Verilog文件然后综合实现了;

另一种是老版本的简明教程所推荐的EDIF项目,这种项目是使用其他的综合工具(如SynplifyPro)来生成综合文件的,然后通过ISE完成对项目Netlist文件和ChipScope生成的Netlist文件的整合以生成实现文件的。

这里我们仅使用ISE来完成整个设计,所以选择HDL项目文件。

接下来添加一些VHDL源代码,www.asic-

这个网站不错里面有些很好的VHDL源代码,我们借用其中的gray_counter.vhd来生成项目。

添加一个Top文件来集成这个模块和将要加入的逻辑分析仪模块。

接下来就要用ChipScope来生成逻辑分析仪的核,首先打开XilinxChipScopeProCoreGenerator。

如下图,选择第一项先生成一个逻辑分析仪控制器。

之后的窗口是指定输出网表文件、目标平台以及icon的一些参数。

其中最主要的是NumberofControlPorts它指定了一个icon可以挂载几个ila而ila就是我们链接在信号上的探测点所以这个控制端口的数量一定要考虑清楚。

另外绝对不能忽略生成的*.Edn文件的存放的位置,一定要在当前的项目目录下,要不然在implement阶段会找不到Netlist而无法通过编译的。

我们的配置如下图所示:

再接下来就是设置生成HDL例子文件,高手们不需要例子,我们大家都是高手,所以我们都不需要例子。

呵呵。

最后选择GeneratorCore来生成icon所要的文件。

包括(*.edn、*.ncf、*.arg等)

完成上面的工作后就是生成ILA,基本流程和ICON的生成几乎一样,要注意输出文件的位置和刚才生成的ICON是一样的。

另外这个过程中会多出来很多选项,每个选项的含义可以参考Xilinx网站提供的chipscope_pro_sw_cores_9_1i_ug029.pdf或者参看老版本的简明教程。

当然了现在我要的版本是这个,若干年后是什么样就不知道了,不过可以推测出来的,因为大家都是牛人么。

其实话说回来,不用查那些文档也可以,看选项名大概就能猜出是干什么的,最重要的无非就是设置一些输出目录,添加一些Trig端口资源,再或者选择数据存储什么的挺简单的。

上述工作之后,在原来建立的项目里就有了两个重要的文件产生icon.edn和ila.edn。

接下来我们修改原来的顶层文件,引入两个component,修改结果如下,红色部分为额外加入的语句,具体项目可以斟酌考虑修改。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

----Uncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entityTop_Grayis

port(

clk

:

in

std_logic;

--Inputclock

reset

std_logic

--Inputreset

);

endTop_Gray;

architectureBehavioralofTop_Grayis

componentgray_counteris

cout

outstd_logic_vector(7downto0);

--Outputofthecounter

enable:

--Enablecounting

endcomponent;

-------------------------------------------------------------------

--

--

ILAcorecomponentdeclaration

-------------------------------------------------------------------

componentila

port

(

control

in

std_logic_vector(35downto0);

trig_out

outstd_logic;

trig0

std_logic_vector(7downto0)

);

ICONcorecomponentdeclaration

componenticon

control0

outstd_logic_vector(35downto0)

signalcontrol0,trig0,tmp

:

signalenable:

std_logic:

='

1'

;

signaltrig_out

begin

uut:

gray_counterportmap(

cout=>

tmp,

enable=>

enable,

clk=>

clk,

reset=>

reset

ILAcoreinstance

i_ila:

ila

portmap

=>

control0,

trig_out

trig_out,

trig0

trig0<

=tmp;

ICONcoreinstance

i_icon:

icon

control0

endBehavioral;

这样就完成了项目的建立,可以开始综合与实现生成bit文件了。

当然一定要注意UCF文件的建立和正确配置。

一切安静下来后,从ISE启动ChipScopeProAnalyzer,选择左上角的那个下载按钮,然后选择要下载的器件,在NewProject里出现的器件中选择要下载的,在弹出的鼠标右键菜单里选择configure如下图:

在我们的设备里就出现了四个选项,双击任意一个就会出现相应的窗口,最常用的就是TriggerSetup和waveForm如图:

之后就是参考xilinx提供的ChipScope提供的文档来设置各个Trig了,都走到了这步剩下的就轻松多了。

最后,最上面的那个开始按钮,再按一下板子上的Reset按钮就可以等待结果了。