系统结构期末考试试题及答案Word下载.docx

《系统结构期末考试试题及答案Word下载.docx》由会员分享,可在线阅读,更多相关《系统结构期末考试试题及答案Word下载.docx(13页珍藏版)》请在冰豆网上搜索。

A.可以并行执行B.不可能并行C.任何情况均可交换串行D.必须并行执行

6、计算机使用的语言是(B)

A.专属软件范畴,与计算机体系结构无关B.分属于计算机系统各个层次

C.属于用以建立一个用户的应用环境D.属于符号化的机器指令

7、指令执行结果出现异常引起的中断是(C)

A.输入/输出中断B.机器校验中断C.程序性中断D.外部中断

8、块冲突概率最高的Cache地址映象方式是(A)

A.直接B.组相联C.段相联D.全相联

9、组相联映象、LRU替换的Cache存储器,不影响Cache命中率的是(B)

A.增大块的大小B.增大主存容量C.增大组的大小D.增加Cache中的块数

10、流水处理机对全局性相关的处理不包括(C)

A.猜测法B.提前形成条件码C.加快短循环程序的执行D.设置相关专用通路

二填空题:

(20分,每题2分)

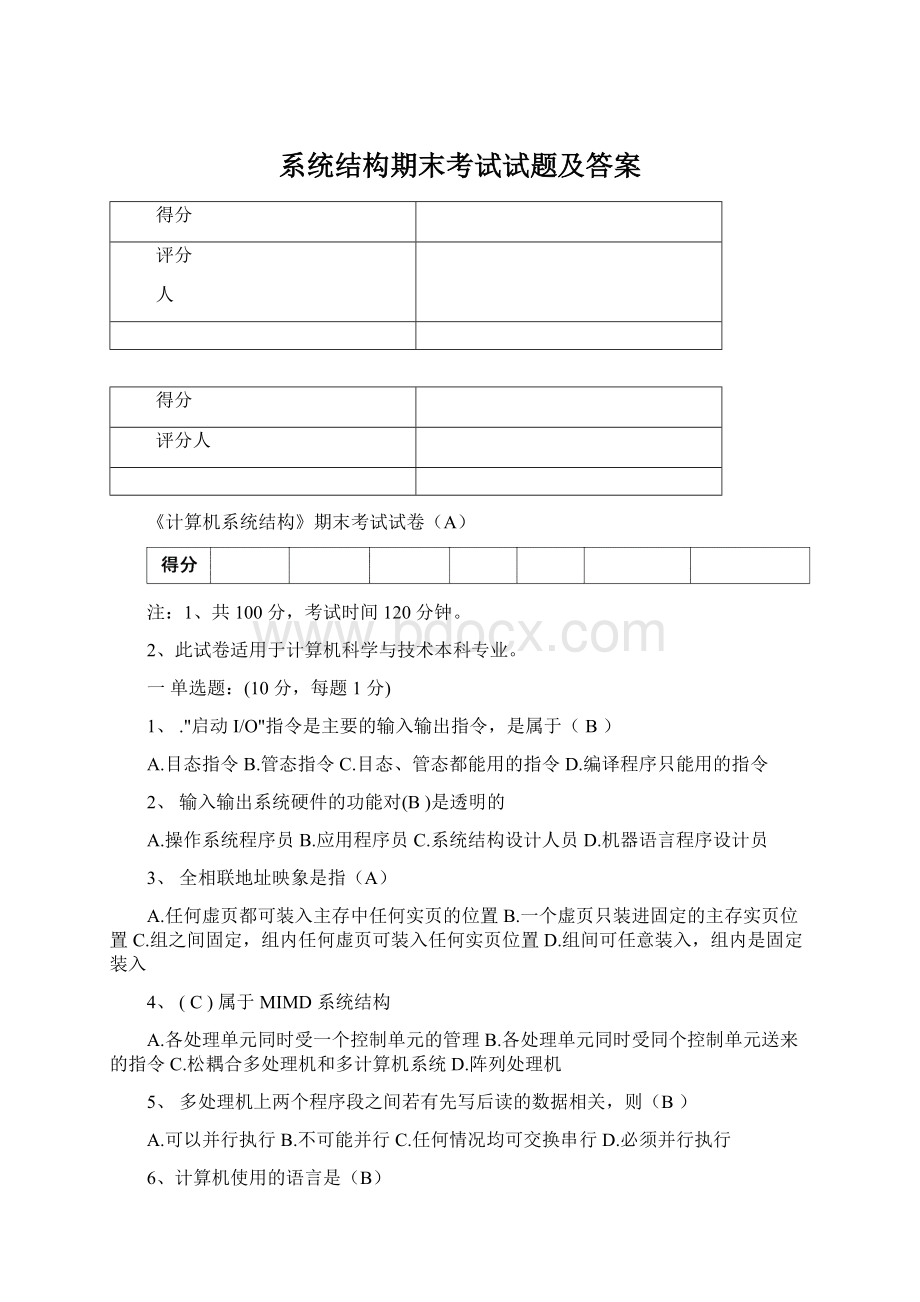

《计算机系统结构》期末考试试卷A卷第1页共11页

1、数据通路宽度就是数据总线上一次并行传送的信息位数。

2、计算机仿真用微程序解释,计算机模拟用机器语言解释

3、阵列处理机按存贮器的组成方式可分为两种构形,分别为:

分布式存储器

和集中共享式。

4、按弗林的观点,计算机系统可分为SISD、SIMD、

MISD

和MIMD

四大类

5、浮点数尾数的下溢处理方法有:

截断法,舍入法,恒置1法,查表舍入法。

6、流水线消除速度瓶颈的方法有瓶颈子过程_拆分_和瓶颈子过程_并联_

____两种。

7、具有相同“系统结构”(如指令系统相同)的计算机可以因为速度要求等因素的不同而采用计算机组成。

8.在非线性流水线机器中,可能发生的数据相关有:

先读后写相关,写写相关和先写后读相关。

8、互连网络的交换方法主要有线路交换、包交换、线路/包交换,SIMD互连网络

多采用线交换,多处理机常采用包

交换。

9、Cache存储器写操作时,只写入Cache,仅当需要块替换时,才将其写回主存,称这种修改主存块内容的方法为__写回法____。

三简答题:

(40分,每题4分)

1.计算机系统结构研究的是什么?

软、硬件之间的功能分配以及对传统机器级界面的确定。

2.计算机组成和计算机实现有什么关系?

计算机组成指的是计算机系统结构的逻辑实现。

计算机实现指的是计算机组成的物理实现。

计算机组成和计算机实现关系密切,有人将它们和称为计算机实现。

3.器件的发展对系统结构的影响?

器件的发展改变了逻辑设计的传统方法。

器件的发展也使系统结构的“下移”速度加快。

器件的发展还促进了算法、语言和软件的发展。

4.解决计算机主存与CPU的速度差对机器性能的影响,可采用哪些解决方法?

设置Cache,采用并行主存系统

5.简述设计RISC结构使用的基本技术。

(1)按设计RISC的一般原则来设计

(2)逻辑实现上采用硬联和微程序相结合(3)设置大量工作寄存器并采用重叠寄存器窗口(4)指令用流水和延迟转移(5)采用Cache(6)优化设计编译系统

《计算机系统结构》期末考试试卷A卷第2页共11页

6.什么是软件的可移植性?

软件不修改或只经少量修改就可由一台机器移植到另一台机器上运行

7.请解释说明常用的4种基本单级互联网络.

立方体单级网络,PM2I网络,混洗交换单级网络,蝶形单级网络

8.什么是中断响应次序和处理次序?

中断响应次序是在同时发生多个不同种类的中断请求时,中断响应硬件中排队器所决定的响应次序.处理次序是各个中断请求实际被处理完毕的顺序.

9.请解释存储系统和存储体系的区别.

存储系统是将多种不同工艺的存储器组织在一起,但从逻辑上还不能成为一个整体.而存储体系就是从程序员角度来看,各种不同工艺的存储器在逻辑上是一个整体.10.请说明一次重叠中通用寄存器组相关的处理办法.

处理办法有推后读和设置相关通路

四计算题:

(30分,每题6分)

1.

经统计,某机器14条指令的使用频率分别为:

0.01,0.15,0.12,0.03,0.02,

0.04,0.02,

0.04,0.01,0.13,0.15,0.14,0.11,0.03。

请分别求出用等长码,哈夫曼码,只有两种码长的扩展操作码的操作码平均码长。

等长码码长为4位,哈夫曼码平均码长为3.38位,两种码长的扩展操作码的操作码平均码长为3.4位

2.设有两个向量C和D,各有4个元素,在图中的静态双功能流水线上工作。

其中,1->

2->

3->

5组成加法流水线,1->

4->

5组成乘法流水线。

设每个流水线所经过的时间均为Δt,而且流水线的输出结果可以直接返回到输入或暂存于相应的缓冲寄存器中,其延迟时间和功能切换所需要的时间都可以忽略不计。

求:

该流水线的实际吞吐率TP和效率η。

5

4

3

2

1

012345678910111213141516实际吞吐率TP=7/(15Δt)

《计算机系统结构》期末考试试卷A卷第3页共11页

时间Δt

η=32%

3.在一个5段的流水线处理机上需经9拍才能完成一个任务,其预约表如下表所示。

(1)分别写出延迟禁止表F、初始冲突向量C;

(2)画出流水线状态转移图;

(3)求出最小平均延迟、调度最佳方案。

分别写出延迟禁止表F={1,5,6,8},初始冲突向量C={10110001},

最小平均延迟:

3.5拍

流水线状态转移图调度最佳方案 (3,4)

4.如果设一个系统有四个中断级,中断响应次序为1->

4。

现要求中断处理次序改为1->

2,

(1)请画出中断级屏蔽位表。

(2)如果在运行用户程序的过程中同时发生了1,2,3,4级中断,请画出此程序运行过程示意图。

(3)如果在运行用户程序的过程中同时发生了2,3级中断,而在3级中断未处理完毕又发生了4级中断,最后回到用户程序时又同时发生了1,2级中断,请画出此程序运行过程示意图。

(1)

《计算机系统结构》期末考试试卷A卷第4页共11页

(2) (3)

5.计算多级立方体互连网络。

见图N=8多级立方体互连网络,求当输入端级控制信号为S2S1S0=010时,输入端为01234567时,输出端为:

23016745。

6

7

s0s1s2

《计算机系统结构》期末考试试卷A卷第5页共11页

计算机科学系《计算机系统结构》期末考试试卷(B卷)

年级:

___专业:

_____班级:

_

学号:

___姓名:

_____

题号

一

二

三

四

五

总分

签名

11、.计算机中优化使用的操作码编码方法是(D)

A.哈夫曼编码B.ASCII码C.BCD码D.扩展操作码

12、对系统程序员不透明的应当是 (B)

A.Cache存储器B.虚拟存储器C.指令缓冲寄存器D.数据通路宽度

13、全相联地址映象是指(A)

14、(C)属于MIMD系统结构

15、多处理机上两个程序段之间若有先写后读的数据相关,则(B)

16、系列机软件必须保证(C)

A.向前兼容,并向上兼容 B.向前兼容,并向下兼容

C.向后兼容,力争向上兼容D.向后兼容,力争向下兼容

17、指令执行结果出现异常引起的中断是(C)

18、在Cache存储器中常用的地址映象方式是(C)

A.全相联映象B.页表法映象C.组相联映象D.段页表映象

19、组相联映象、LRU替换的Cache存储器,不影响Cache命中率的是(B)

20、流水处理机对全局性相关的处理不包括(D)

《计算机系统结构》期末考试试卷A卷第6页共11页

10、数据宽度就是I/O设备取得I/O总线后所传送数据的总量

。

11、计算机仿真用微程序解释,计算机模拟用机器语言解释

12、固件就是 一种具有软件功能的硬件

13、按弗林的观点,计算机系统可分为SISD、SIMD

、

14、浮点数尾数的下溢处理方法有:

截断法,舍入法,恒置1法,查表舍

入法。

15、实现软件移植的基本技术有 同一高级语言, 采用系列机, 模拟和

仿真。

16、并行主存系统包括单体多字,多体单字 和 多体多字交叉存储器 。

17、在非线性流水线机器中,可能发生的数据相关有:

先读后写相关,写

写相关

和先写后读相关。

18、互连网络的交换方法主要有线路交换、包交换、线路/包交换,SIMD互连

网络多采用线交换,多处理机常采用包

19、Cache存储器写操作时,在写入Cache的同时将其写回主存,称这种修改主存块内容的方法为__写直达法____。

5.计算机系统结构研究的是什么?

6.计算机组成设计要解决的问题是什么?

在所希望能达到的性能和价格比的前提下,怎样最佳、最合理地把各种设备和部件组织成为一台计算机,以实现所确定的系统结构。

7.举例说明几种指令级高度并行的超级处理机?

超标量处理机、超长指令字处理机、超流水线处理机、超标量超流水线处理机8.解决计算机主存与CPU的速度差对机器性能的影响,可采用哪些解决方法?

《计算机系统结构》期末考试试卷A卷第7页共11页

11.CISC指令系统的含义?

复杂指令系统计算机,即机器指令系统变得越来越庞杂,这就是所谓的CISC指令系统。

12.什么是软件的可移植性?

13.请解释说明常用的4种基本单级互联网络.

14.什么是并行性?

只要在同一时刻或是在同一时间间隔内完成两种或两种以上性质相同或不同的工作,它们在时间上能相互重叠,都体现了并行性。

15.请解释存储系统和存储体系的区别.

存储系统是将多种不同工艺的存储器组织在一起,但从逻辑上还不能成为一个整体.而存储体系就是从程序员角度来看,各种不同工艺的存储器在逻辑上是一个整体.16.请说明一次重叠中通用寄存器组相关的处理办法.

设一台模型机有7条指令,其使用频度为:

指令

使用频度|

使用频度

I10.03|I40.05I20.03|I50.15I30.04|I60.3

|I70.4

《计算机系统结构》期末考试试卷A卷第8页共11页

《计算机系统结构》期末考试试卷A卷第9页共11页

4.若机器共有5级中断,中断响应优先次序为l→2→3→4→5,现要求其实际的中断处理次序为l→4→5→2→3。

(1)设计各级中断处理程序的中断级屏蔽位(令“1”对应于屏蔽,“0”对应于开放);

(2)若在运行用户程序时,同时出现第4、2级中断请求,

而在处理第2级中断未完成序运行过程示意图。

时,又同时出现第l、3、5级中断请求,请画出此程

中断处理程

序级别

中断级屏蔽位

1

2

3

4

0

《计算机系统结构》期末考试试卷A卷第10页共11页

《计算机系统结构》期末考试试卷A卷第11页共11页