信息化实训教学大赛资料数字时钟的制作与调试_精品文档.doc

《信息化实训教学大赛资料数字时钟的制作与调试_精品文档.doc》由会员分享,可在线阅读,更多相关《信息化实训教学大赛资料数字时钟的制作与调试_精品文档.doc(9页珍藏版)》请在冰豆网上搜索。

数字时钟的电路原理与制作

——全国职业院校信息化实训教学大赛参考电路

一、数字时钟的设计制作

1.1设计目的

通过设计与实践,制作出具有准确显示时、分、秒的可调数字时钟。

1.2 设计要求

数字时钟的功能要求:

准确计时,以数字形式显示时、分、秒的时间,要求有校准时间电路。

1.3 设计方案及论证

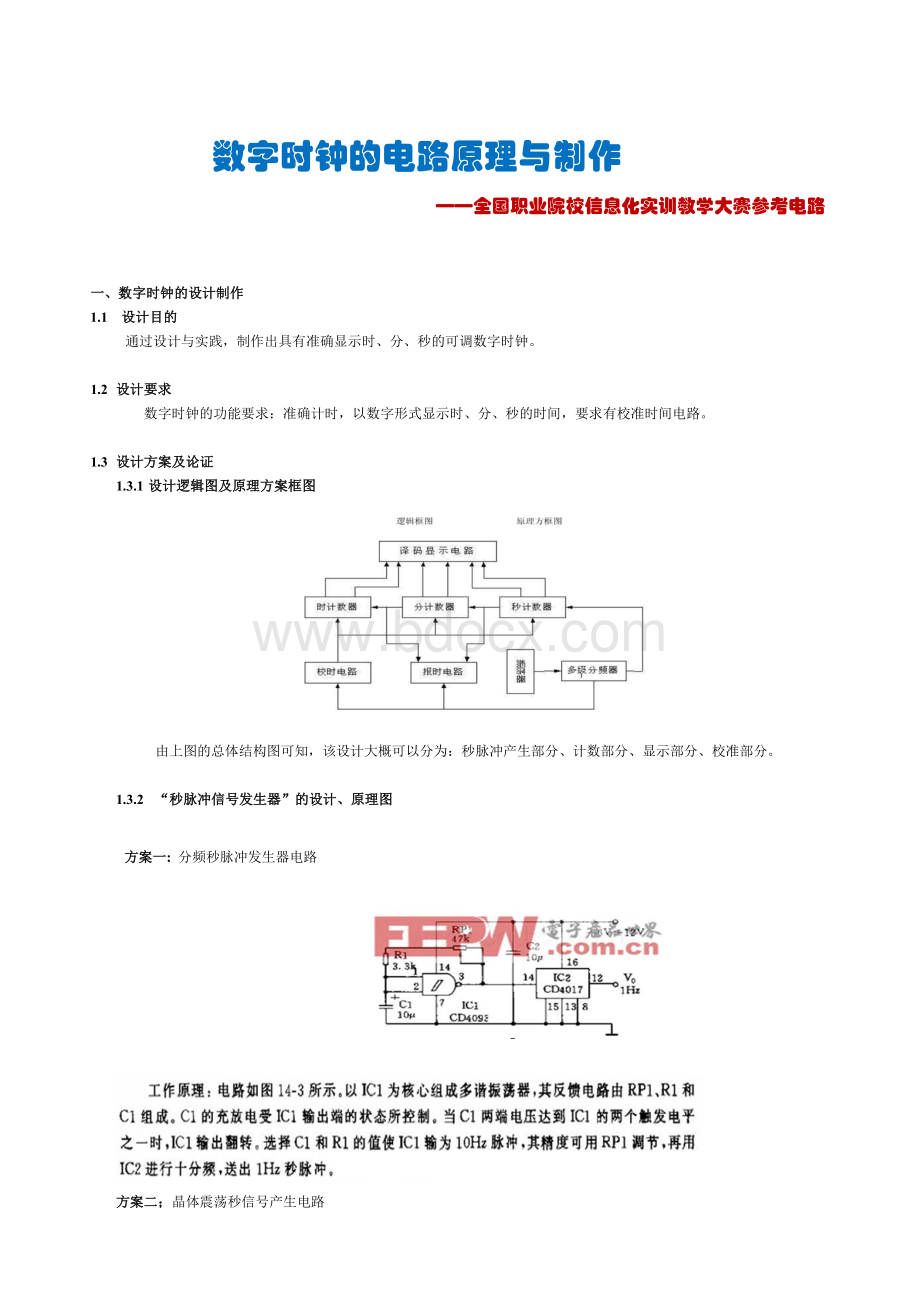

1.3.1 设计逻辑图及原理方案框图

由上图的总体结构图可知,该设计大概可以分为:

秒脉冲产生部分、计数部分、显示部分、校准部分。

1.3.2 “秒脉冲信号发生器”的设计、原理图

方案一:

分频秒脉冲发生器电路

方案二;晶体震荡秒信号产生电路

方案三:

555多谐振荡器

震荡器是数字钟的核心部分。

振荡器的稳定性及频率的精确度决定了数字时钟计时的准确程度,一般来说555产生的秒脉冲不太稳定,但是由于本实验中对秒脉冲稳定度要求不高,方案三采用555定时器简单易实现,成本更低且满足实验要求。

其中要求电阻为100K,电容为4.7uF、0.01Uf,Vcc为+5V电源,GND接地。

1.3.3 计数、译码、驱动及显示部分的设计

方案一:

74LS160、74LS247和共阳数码管SM4105组成的计数译码驱动显示电路

方案二:

CD4518、CD4511和共阴数码管组成的计数译码驱动显示电路

由原理图可知:

方案二的电路更简单易于PCB版的制作,CD4511驱动效果更好;方案一要多一块芯片,电路更复杂。

所以我选择方案二,且用两位数码管代替两个一为的数码管。

1.3.4 秒计数、译码、驱动及显示部分的设计

秒、分、时分别为六十、六十、二十四进制(十二进制亦可)计数器那么“秒”和“分”计数器用两块十进制计数器级连来实现,它们的个位为十进制,十位为六进制,这样符合人们通常计数的习惯。

“时”计数也用两个十进制集成块,只是做成二十四进制,上述计时器均可用反馈清零法来实现。

秒计数采用两位共阴管、两个CD4511和一个CD4518来实现,将“秒”信号送人“秒”计数器,秒计数器采用60进制计数器,每累计60秒发出一个“分”脉冲信号,该信号将作为“分”计数器的时钟脉冲,进位脉冲最终用CD4518的一个与门来实现。

而CD4511芯片具有锁存、译码、计数的功能,可以外接电阻驱动数码管显示出来。

1.3.5 分计数、译码、驱动及显示部分的设计

分计数和秒计数的原理差不多,也是采用两位共阴数码管、两个CD4511和一个CD4518来实现,将“秒”计数器的进位脉冲送人“分”计数器,每累计60分发出一个“时”脉冲信号,该信号将作为“时”计数器的时钟脉冲,进位脉冲最终用CD4518的一个与门来实现。

同样采用CD4511芯片驱动数码管显示出来。

1.3.6 时计数、译码、驱动及显示部分的设计

时计数和分计数的原理差不多,也是采用两位共阴数码管、两个CD4511和一个CD4518来实现,将“分”计数器的进位脉冲送人“时”计数器,但是计数器采用的是24进制且不需要进位脉冲,同样采用CD4511芯片驱动数码管显示出来。

1.3.7 分、时校准电路的设计

校准电路是用秒信号去代替分计数信号和是时计数信号,使分或时计数快速进行,因此校准电路实际上是一个数字信号的转换开关,以下给出了三种校准电路。

图(a)是一种简单的手动开关电路,正常工作时S指向A,需要校准时按下S,使S指向B,用秒信号作为分或时的计数信号,这种电路时分简单,但是开关的通断产生随机的机械抖动信号,使校准不易控制,轻轻按动开关可消除或减少这种机械抖动。

图(b)是用桑与非门和一个可调电位器实现信号的转换,当正常工作时电位器动滑头指向B,此时CP=Co‘。

当需要校准时,动滑头指向A,此时CP等于秒信号,两个0.033的电容可虑去滑动中产生的干扰信号,偶然也会产生抖动干扰。

图(c)是由三个与非门和基本RS触发器组成的,基本RS触发器可完全消除开关的机械抖动,是最佳的一种校准电路,当然电路要比较复杂。

分时校准电路的原理是一样的,为简化电路本实验均是采用瓷片电容103、与门电路和开关组成的电路来代替与非门和基本RS触发器组成的电路来实现,具体电路如下

CP时/分脉冲Co进位

CP秒脉冲

平常计时状态下,开关处于断开状态,当需要校时时,按下开关,瓷片电容则放电,CD4011的引脚1、2是低电平,3引脚输出高电平,此时8引脚送人时钟脉冲,则10输出低电平,那么4输出一定是高电平,而且这个高电平被送人CD4518的1管脚,此时“分”必定加1,同理,若连续按下开关则“分”就会连续加1,即完成分校时。

时校时电路的原理和分笑时是一样的,不多做解释。

1.4 调试及故障排除

本实验调试简单,只需检查电路无误后接入+5V电源,查看数码管显示是否正常。

发现时分显示部位不能正常工作:

分部位不能正常显示;校准电路不能正常校准;时部位显示10到19中数码管产生鬼影现象。

用万用表检查发现:

秒部位电路中漏焊一根跳线;按钮开关接反成常闭开关;时部位的数码管的十位部分的A、B两线太过接近。

经改正后电路能正常工作且能对时分位正常校准。

1.5 附图

1.6.1 一些芯片的引脚及功能

① 数码管是数字时钟的显示部分,其引脚图如图

② CD4511是BCD锁存、7段译码器、驱动器,常用的显示芯片,其引脚图如图

③ CD4518是十进制双BCD同步加法计时器,内部含有两个的加计数器,其引脚图如图

CD4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器。

每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。

若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。

RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。

这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。

若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。

CD4520/CC4520为二进制加计数器,由两个相同的内同步4级计数器构成。

计数器级为D型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数。

在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。

CR线为高电平时,计数器清零。

计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平。

④CD4081是四2输入与门电路,其结构如图

⑤CD4011是四2输入与门电路,其结构如图

1.6.2 原理图

8