EDA技术课程设计报告.docx

《EDA技术课程设计报告.docx》由会员分享,可在线阅读,更多相关《EDA技术课程设计报告.docx(22页珍藏版)》请在冰豆网上搜索。

EDA技术课程设计报告

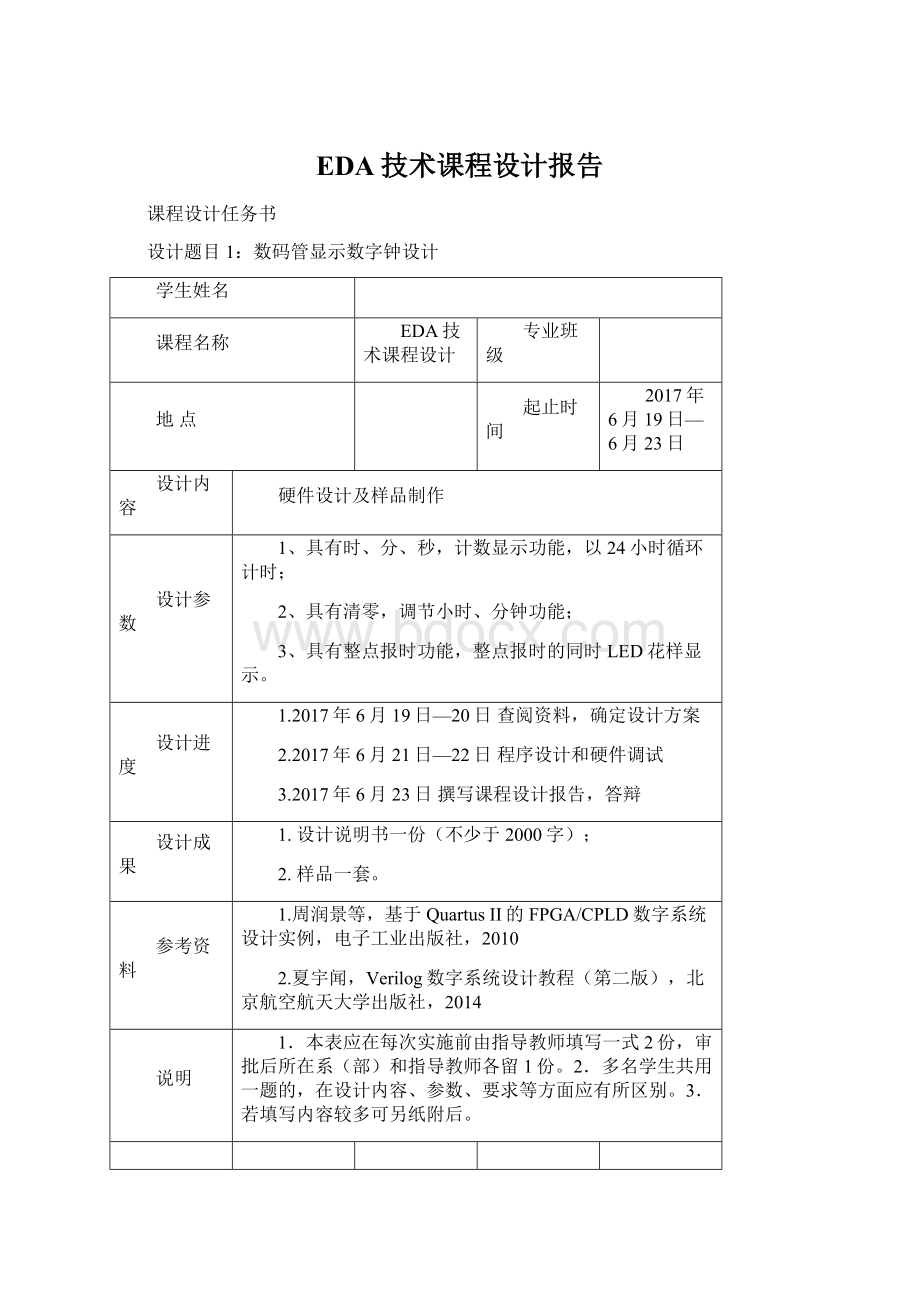

课程设计任务书

设计题目1:

数码管显示数字钟设计

学生姓名

课程名称

EDA技术课程设计

专业班级

地点

起止时间

2017年6月19日—6月23日

设计内容

硬件设计及样品制作

设计参数

1、具有时、分、秒,计数显示功能,以24小时循环计时;

2、具有清零,调节小时、分钟功能;

3、具有整点报时功能,整点报时的同时LED花样显示。

设计进度

1.2017年6月19日—20日查阅资料,确定设计方案

2.2017年6月21日—22日程序设计和硬件调试

3.2017年6月23日撰写课程设计报告,答辩

设计成果

1.设计说明书一份(不少于2000字);

2.样品一套。

参考资料

1.周润景等,基于QuartusII的FPGA/CPLD数字系统设计实例,电子工业出版社,2010

2.夏宇闻,Verilog数字系统设计教程(第二版),北京航空航天大学出版社,2014

说明

1.本表应在每次实施前由指导教师填写一式2份,审批后所在系(部)和指导教师各留1份。

2.多名学生共用一题的,在设计内容、参数、要求等方面应有所区别。

3.若填写内容较多可另纸附后。

院(系)分管领导:

教研室主任:

指导教师:

2017年6月23日

第1章引言

EDA是电子设计自动化(ElectronicDesignAutomation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL或者VerilogHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

VerilogHDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

此次课程设计我们运用QuartusⅡ这个软件,使用VerilogHDL语言进行编程。

数字钟是一种用数字电路技术实现时、分、秒计时的钟表。

与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟,也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟,还可以利用单片机来实现电子钟等等。

这些方法都各有其特点,其中利用单片机实现的电子钟具有编程灵活,以便于功能的扩展。

本次课程设计要求利用EDA技术,设计一个数码管显示数字钟的样品,数字钟要求具备以下功能:

1、具有时、分、秒,计数显示功能,以24小时循环计时;

2、具有清零,调节小时、分钟功能;

3、具有整点报时功能,整点报时的同时LED花样显示。

第2章电路原理

数码管显示数字钟设计,运用到8位数码管,要求其中6位数码管动态显示,分别显示时、分、秒的计数,同时对时间进行设置,数字钟的总体功能按照要求可以分为基本的数字时钟显示(具有时、分、秒,计数显示功能,以24小时循环计时)、手动校准(具有清零,调节小时、分钟功能)、整点报时、LED灯花样显示四大部分。

其总体功能设计框图如图2.1所示:

第3章程序设计

其中,“时钟分频模块”用于对芯片晶振提供的时钟信号进行分频,然后给其他模块分配需要的时钟频率。

按键输入的信号经过按键去抖后传送给“时钟计数模块”。

正常计数时,“时钟计数模块”将处理好的时、分、秒数据实时传送给“数码管显示模块”,当有来自“按键驱动模块”的信号时,改变相应的时、分、秒计数器中的值,实现调整时间的作用。

“数码管显示模块”实时将“时钟计数模块”的数据转换成数码管动态显示信号进行显示。

最后,加上一个“整点报时”模块和“LED灯花样显示模块”经过时钟分频信号,传递给“数码管显示模块”,实现所需功能。

数字钟设计原理如图3.1所示:

3.1顶层模块设计

顶层模块设计如附录图3所示,其RTL电路图如附录图4所示。

顶层模块包含四个输入:

系统时钟输入“clk”,秒设置信号“sset”,分钟设置信号“mmset”,小时设置信号“hset”。

一个8位的段选数码管显示值输出“seg”,一个8位的片选数码管显示哪一个数码管输出“dig”,将输出给数码管进行动态显示。

“时钟分频模块”电路符号名为“int_div”,“按键驱动模块”电路符号名慰“an_jian”,“时钟计数模块”内部采用三格计数器级联的方式分别驱动时、分、秒计数,秒计数器和分计数器均为60进制计数器,小时计数器为24进制计数器,电路符号名分别为两个“ji_shu_60”和一个“ji_shu_24”。

3.2时钟分频模块设计

“时钟分频模块”直接使用老师上课所给的分频程序,加入两个分频模块,与“时钟计数模块”和“按键驱动模块”进行连接。

3.3按键驱动模块设计

按键驱动模块使用原理图方法设计,采用在按键信号传输过程中串联触发器实现按键去抖,保证触发器两次触发的间隔远大于按键抖动的时间,而远小于人动作反应的时间。

另外因为实例用独立按键按下后是低电平,所以在触发器后面串联一个非门,使其变为高电平有效。

附录图1所示为按键驱动模块原理图,图3.2所示为按键驱动模块封装而成的电路元件。

该模块包括四个输入,时钟信号clk,秒设置输入s_in,分钟设置输入m_in,小时设置输入h_in;三个输出,秒设置输出s_out,分钟设置输出m_out,小时设置输出h_out。

从该模块的原理图可以看出,时、分、秒三个按键的去抖原理完全一样,这里提取小时输入和输出进行仿真验证,得到的结果如图4.1所示,每一个时钟上升沿h_out的值都保持和h_in的值相反,该设计能够达到预期设计要求。

3.4时钟计数模块设计

如附录图2所示。

“时钟计数模块”内部采用三个计数器级联的方式分别驱动时、分、秒计数,秒计数器和分钟计数器均为60进制计数器,小时计数器为24进制计数器,为方便驱动数码管,三个计数器的输出均为两位的十进制数据。

秒调整信号通过一个或门和秒进位信号一起驱动分钟计数器;小时调整和分钟调整同理。

60进制计数器主要VerilogHDL代码如下:

begin

if(!

rst)//0

begin

q1<=0;q2<=0;

end

else

beginq1[3:

0]=q1[3:

0]+1;co<=0;

if(q1[3:

0]>9)beginq1[3:

0]=0;

q2[3:

0]=q2[3:

0]+1;

if(q2[3:

0]>5)beginq2[3:

0]=0;co<=1;end

end

elseq1=q1;

end

end

24进制计数器主要VerilogHDL代码如下:

begin

co=0;

q1[3:

0]=q1[3:

0]+1;

if(q1[3:

0]>9)beginq1[3:

0]=0;q2[3:

0]=q2[3:

0]+1;end

if(q1==4)if(q2==2)beginq1=0;q2=0;end

end

如图4.2所示该模块中60进制模块与24进制模块的仿真波形,60进制模块设置qs0、qs1分别为个位、十位,个位计数到9之后清零,十位计数到5之后清零,24进制模块设置qh0、qh1分别为个位、十位,个位计数到9之后清零,十位计数到2之后清零。

3.5整点报时模块

整点报时模块的设计思路是当数字钟计数到一个整点时间时,蜂鸣器开始响鸣。

蜂鸣器的封装设计如图3.3所示,程序设计为一段乐谱,主要VerilogHDL代码如下:

always@(posedgeclk_4Hz)

begin

case(j)

'd1:

origin='d4916;//low

'd2:

origin='d6168;

'd3:

origin='d7281;

'd4:

origin='d7791;

'd5:

origin='d8730;

'd6:

origin='d9565;

'd7:

origin='d10310;

'd8:

origin='d010647;//middle

'd9:

origin='d011272;

'd10:

origin='d011831;

'd11:

origin='d012087;

'd12:

origin='d012556;

'd13:

origin='d012974;

'd14:

origin='d013346;

'd15:

origin='d13516;//high

'd16:

origin='d13829;

'd17:

origin='d14108;

'd18:

origin='d11535;

'd19:

origin='d14470;

'd20:

origin='d14678;

'd21:

origin='d14864;

default:

origin='d011111;

endcase

end

always@(posedgeclk_4Hz)//乐谱

begin

if(len==63)

len=0;

else

len=len+1;

case(len)

0:

j=3;1:

j=3;2:

j=3;3:

j=3;4:

j=5;5:

j=5;6:

j=5;7:

j=6;8:

j=8;9:

j=8;10:

j=8;11:

j=6;12:

j=6;13:

j=6;14:

j=6;15:

j=12;16:

j=12;17:

j=12;18:

j=15;19:

j=15;20:

j=15;21:

j=15;22:

j=15;23:

j=9;24:

j=9;25:

j=9;26:

j=927:

j=9;28:

j=9;29:

j=9;30:

j=9;31:

j=9;32:

j=9;33:

j=9;34:

j=10;35:

j=7;36:

j=7;37:

j=6;38:

j=6;39:

j=5;40:

j=5;41:

j=5;42:

j=6;43:

j=8;44:

j=8;45:

j=9;46:

j=9;47:

j=3;48:

j=3;49:

j=8;50:

j=8;51:

j=8;52:

j=5;53:

j=5;54:

j=8;55:

j=5;56:

j=5;57:

j=5;58:

j=5;59:

j=5;60:

j=5;61:

j=5;62:

j=5;63:

j=5;

endcase

end

3.6LED灯花样显示模块

LED灯花样显示模块是与整点报时模块同时工作,当蜂鸣器响鸣时LED灯闪烁。

该模块设计思路较为简单,只需在时分秒的时钟输出端接入一个以低电平驱动的LED邓即可实现。

3.7数码管显示模块设计

数码管动态显示的原理是利用人眼的视觉停留,依次点亮每个数码管的位选信号,当第一个数码管被点亮时,将段选信号变为第一个数码管要显示的信息,当第二个数码管被点亮时,将段选信号变为第二个数码管要显示的信息,以此类推,循环扫描。

当循环扫描一次所有数码管所用的时间在人眼能反应出图像变化的时间(约为0.02秒)之内时,人自然就会在视觉上看到完整的图像,而不会感到闪烁。

“数码管显示模块”的作用就是将6位10进制的时间数据BCD码转化成供数码管动态显示的位选和段选数据。

该模块在VerilogHDL语言描述下的主要段落如下:

always@(posedgeclk_1k)

begin

case(count)//选择扫描显示数据

3'd0:

disp_dat=d0;