实验一4位全加器的设计概论Word下载.docx

《实验一4位全加器的设计概论Word下载.docx》由会员分享,可在线阅读,更多相关《实验一4位全加器的设计概论Word下载.docx(13页珍藏版)》请在冰豆网上搜索。

port

(

a:

instd_logic;

b:

ci:

y:

outstd_logic;

co:

outstd_logic

);

endentity;

architecturertloff_addis

begin

(co,y)<

=('

0'

a)+('

b)+('

ci);

endrtl;

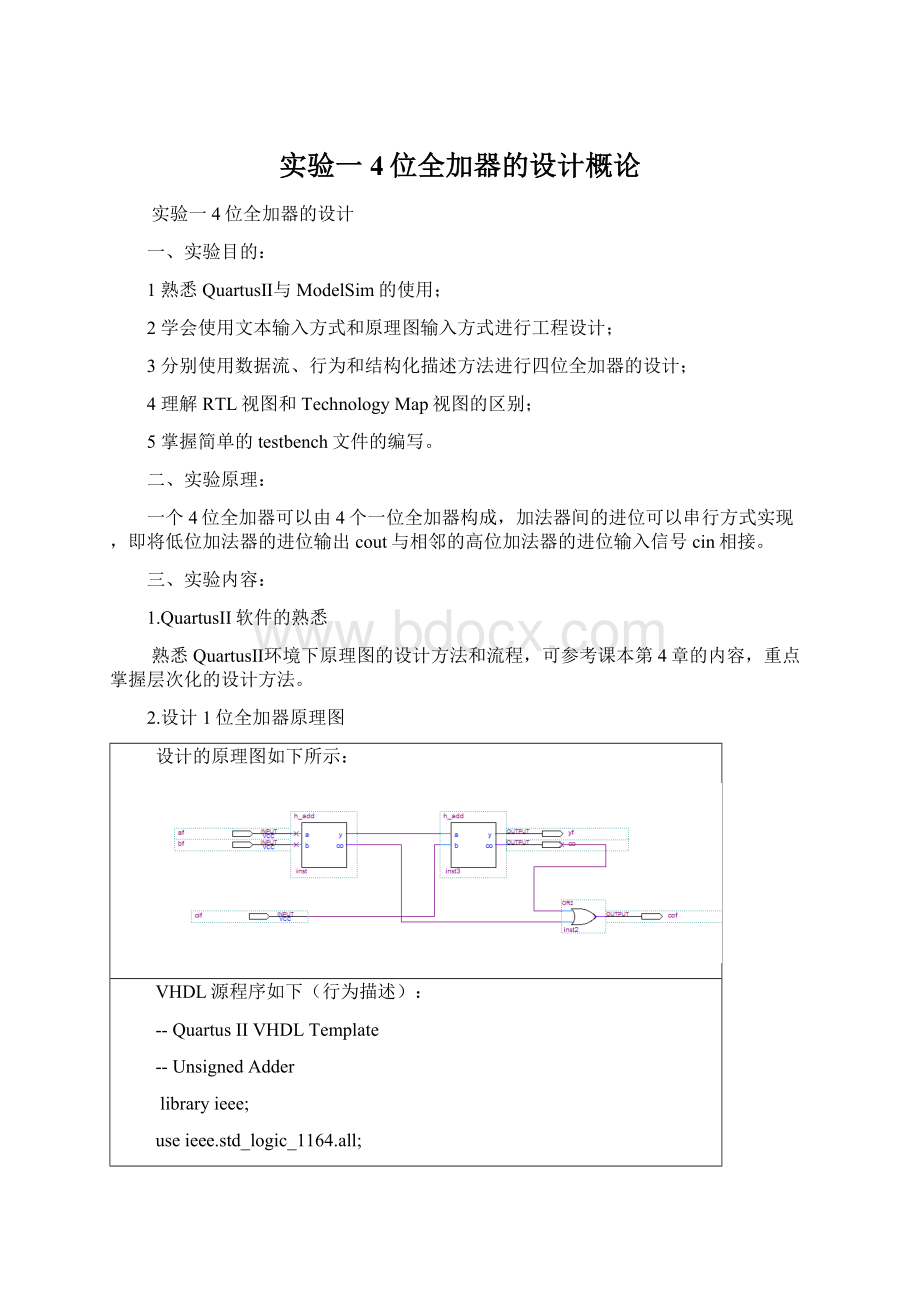

VHDL源程序如下(行为描述)的RTL与technologymap视图

VHDL源程序如下(数据流描述):

libraryieee;

entityf_add_dfis

(

a:

b:

ci:

co:

);

architecturertloff_add_dfis

y<

=axorbxorci;

co<

=((axorb)andci)or(aandb);

VHDL源程序如下(数据流描述)的RTL与technologymap视图:

VHDL源程序如下(结构化描述):

entityf_add_stis

port

af:

bf:

cif:

yf:

cof:

architecturertloff_add_stis

COMPONENTh_add

PORT

a:

INSTD_LOGIC;

b:

y:

OUTSTD_LOGIC;

OUTSTD_LOGIC

ENDCOMPONENT;

signals1:

std_LOGIC;

signalco1:

signalco2:

U1:

h_addportmap(a=>

af,b=>

bf,y=>

s1,co=>

co1);

U2:

h_addportmap(a=>

s1,b=>

cif,y=>

yf,co=>

co2);

cof<

=co1orco2;

VHDL源程序如下(结构化描述)的RTL与technologymap视图:

Testbench文件源程序如下:

LIBRARYcycloneiii;

LIBRARYieee;

USEcycloneiii.cycloneiii_components.all;

USEieee.std_logic_1164.all;

ENTITYf_add_st_tbIS

END;

ARCHITECTUREf_add_st_tb_archOFf_add_st_tbIS

SIGNALbf:

STD_LOGIC:

='

;

SIGNALcof:

STD_LOGIC;

SIGNALcif:

SIGNALaf:

SIGNALyf:

COMPONENTf_add_st

PORT(

bf:

inSTD_LOGIC;

cof:

outSTD_LOGIC;

cif:

af:

outSTD_LOGIC);

ENDCOMPONENT;

BEGIN

DUT:

f_add_st

PORTMAP(

bf=>

bf,

cof=>

cof,

cif=>

cif,

af=>

af,

yf=>

yf);

af<

='

1'

after400ns;

bf<

after200ns,

'

after400ns,

after600ns;

cif<

=notcifafter100ns;

END;

功能仿真波形如下:

时序仿真波形如下:

3.利用层次化原理图方法设计4位全加器

(1)生成新的空白原理图,作为4位全加器设计输入

(2)利用已经生成的1位全加器作为电路单元,设计4位全加器。

原理图设计如下(结构化描述):

原理图设计如下(结构化描述)的RTL与technologymap视图:

entityf4_add_bhis

instd_logic_vector(3downto0);

outstd_logic_vector(3downto0);

architecturebhoff4_add_bhis

signalyin:

std_logic_vector(4downto0);

yin<

&

a)+('

b)+('

ci);

y<

=yin(3downto0);

co<

=yin(4);

endbh;

Testbench源程序如下:

USEieee.std_logic_unsigned.all;

ENTITYf4_add_bh_tbIS

ARCHITECTUREf4_add_bh_tb_archOFf4_add_bh_tbIS

SIGNALci:

SIGNALa:

std_logic_vector(3downto0):

="

0000"

SIGNALy:

std_logic_vector(3downto0);

SIGNALb:

SIGNALco:

COMPONENTf4_add_bh

ci:

a:

instd_logic_vector(3downto0);

outstd_logic_vector(3downto0);

b:

co:

f4_add_bh

ci=>

ci,

a=>

a,

y=>

y,

b=>

b,

co=>

co);

a<

1100"

"

1110"

after600ns;

b<

=b+"

0010"

after100ns;

最终的功能仿真波形如下:

最终的时序仿真波形如下:

四、思考题

1、试着论述功能仿真和时序仿真的差别?

2、试着论述结构体的行为描述、数据流描述和结构描述的区别?

3、如何构建四位并行加法器?