基于VHDL语言的交通灯设计DEA.docx

《基于VHDL语言的交通灯设计DEA.docx》由会员分享,可在线阅读,更多相关《基于VHDL语言的交通灯设计DEA.docx(19页珍藏版)》请在冰豆网上搜索。

基于VHDL语言的交通灯设计DEA

交通信号控制器的VHDL的设计

1.设计任务

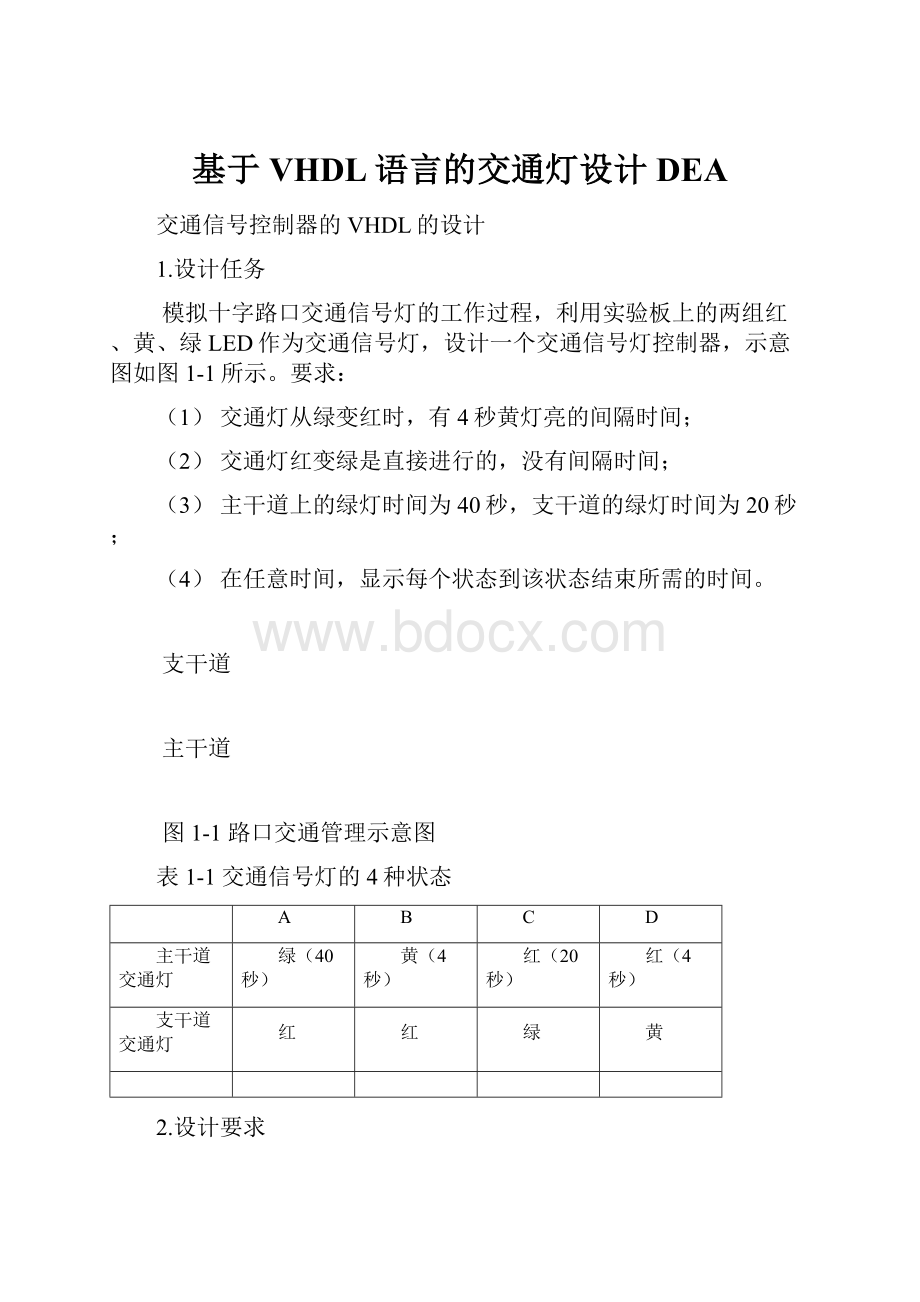

模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED作为交通信号灯,设计一个交通信号灯控制器,示意图如图1-1所示。

要求:

(1)交通灯从绿变红时,有4秒黄灯亮的间隔时间;

(2)交通灯红变绿是直接进行的,没有间隔时间;

(3)主干道上的绿灯时间为40秒,支干道的绿灯时间为20秒;

(4)在任意时间,显示每个状态到该状态结束所需的时间。

支干道

主干道

图1-1路口交通管理示意图

表1-1交通信号灯的4种状态

A

B

C

D

主干道交通灯

绿(40秒)

黄(4秒)

红(20秒)

红(4秒)

支干道交通灯

红

红

绿

黄

2.设计要求

采用VHDL语言编写程序,并在QuartusII工具平台中进行开发,下载到EDA实验箱进行验证。

编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

3.设计方案

状态寄存器

秒脉冲信号发生器

计数器

CLK

时间显示数据输出

次态发生器

信号灯输出信号

信号灯输出

图3-1交通信号灯控制器程序原理框图

进程将CLK信号分频后产生1秒信号,然后构成两个带有预置数功能的十进制计数器,并产生允许十位计数器计数的控制信号。

状态寄存器实现状态转换和产生状态转换的控制信号,下个模块产生次态信号和信号灯输出信号,以及每一个状态的时间值。

经过五个模块的处理,使时间计数、红绿灯显示能够正常运行。

程序原理图如图3-1所示。

4.各模块具体设计

4.1顶层文件的设计

顶层文件的原理图可以依据系统的框图进行,由控制模块JTD_CTRL、计时模块JTD_TIME、译码驱动模块JTD_LIGHT、显示模块JTD_DIS和分频模块JTD_FQU五部分组成,其顶层原理图文件如图3-1所示。

图4-1交通灯顶层文件原理图

顶层模块的程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYTRAFFICIS

PORT(

CLK1K,CLR:

INSTD_LOGIC;

M:

INSTD_LOGIC_VECTOR(2DOWNTO0);

LED:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

SEL:

OUTSTD_LOGIC_VECTOR(2DOWNTO0);

ABL:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDTRAFFIC;

ARCHITECTUREBEHAVEOFTRAFFICIS

COMPONENTJTD_FQUIS--分频器元件的例化

PORT(

CLK1K:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC

);

ENDCOMPONENT;

COMPONENTJTD_DISIS--数码显示的元件例化

PORT(

CLK1K,CLK,CLR:

INSTD_LOGIC;

M:

INSTD_LOGIC_VECTOR(2DOWNTO0);

AT,BT:

INSTD_LOGIC_VECTOR(7DOWNTO0);

LED:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

SEL:

OUTSTD_LOGIC_VECTOR(2DOWNTO0)

);

ENDCOMPONENT;

COMPONENTJTD_LIGHTIS--译码驱动的元件例化

PORT(

CLR:

INSTD_LOGIC;

M,S:

INSTD_LOGIC_VECTOR(2DOWNTO0);

ABL:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDCOMPONENT;

COMPONENTJTD_TIMEIS--计时元件的例化

PORT(

CLK,CLR:

INSTD_LOGIC;

M,S:

INSTD_LOGIC_VECTOR(2DOWNTO0);

AT,BT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDCOMPONENT;

COMPONENTJTD_CTRLIS--控制模块的元件例化

PORT(

CLK,CLR:

INSTD_LOGIC;

AT,BT:

INSTD_LOGIC_VECTOR(7DOWNTO0);

M:

INSTD_LOGIC_VECTOR(2DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(2DOWNTO0)

);

ENDCOMPONENT;

SIGNALCLK:

STD_LOGIC;

SIGNALAT:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALBT:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALS:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

U1:

JTD_FQUPORTMAP(--名字关联方式赋值

CLK1K=>CLK1K,

CLK=>CLK

);

U2:

JTD_TIMEPORTMAP(

CLR=>CLR,

AT=>AT,

BT=>BT,

CLK=>CLK,

M=>M,

S=>S

);

U3:

JTD_CTRLPORTMAP(

M=>M,

S=>S,

CLK=>CLK,

CLR=>CLR,

AT=>AT,

BT=>BT

);

U4:

JTD_DISPORTMAP(

CLK1K=>CLK1K,

CLK=>CLK,

CLR=>CLR,

AT=>AT,

BT=>BT,

LED=>LED,

SEL=>SEL,

M=>M

);

U5:

JTD_LIGHTPORTMAP(

CLR=>CLR,

S=>S,

ABL=>ABL,

M=>M

);

ENDBEHAVE;

4.2控制模块JTD_CTRL的设计

控制的模块根据外部输入信号M2~M0和计时模块JTD_TIME的输入信号,产生系统的状态机,控制其他部分协调工作。

控制模块的源文件程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJTD_CTRLIS

PORT(

CLK,CLR:

INSTD_LOGIC;

M:

INSTD_LOGIC_VECTOR(2DOWNTO0);--用M来表示系统的8种工作状态

AT,BT:

INSTD_LOGIC_VECTOR(7DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(2DOWNTO0)

);

ENDJTD_CTRL;

ARCHITECTUREJTD_1OFJTD_CTRLIS

SIGNALQ:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

PROCESS(CLR,CLK,M,AT,BT)

BEGIN

IFCLR='1'THENQ<="000";--清'0'处理

ELSIF(CLK'EVENTANDCLK='1')THEN--时钟上升沿信号一来,M控制系统的8种状态

IFM="000"THENQ<="001";

ENDIF;

IFM="001"THENQ<="011";

ENDIF;

IFM="010"THENQ<="101";

ENDIF;

IFM="011"THENQ<="111";

ENDIF;

IFM>="100"THEN

IF(AT=X"01")OR(BT=X"01")THENQ<=Q+1;

ELSEQ<=Q;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

S<=Q;--M的控制端转向控制口S

ENDJTD_1;

该模块的时序仿真和功能仿真波形图如图4-2

图4-2功能仿真

4.3计时模块JTD_TIME的设计

计时模块用来设定A和B两个方向计时器的初值,并为显示模块JTD_DIS提供倒计时时间。

当正常计时开始后,需要进行定时计数操作,由于东西和南北两个方向上的时间显示器是由两个LED七段显示数码管组成的,因此需要产生两个2位的计时信息:

2个十位信号,2个个位信号,这个定时计数操作可以由一个定时计数器来完成,又因为交通灯的状态变化是在计时为0的情况下才能进行的,因此需要一个计时电路来产生使能信号,因此定时计数的功能就是用来产生2个2位计时信息和使能信号。

计时模块的源文件程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJTD_TIMEIS

PORT(

CLK,CLR:

INSTD_LOGIC;

M,S:

INSTD_LOGIC_VECTOR(2DOWNTO0);

AT,BT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDJTD_TIME;

ARCHITECTUREJTD_2OFJTD_TIMEIS

SIGNALAT1,BT1:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALART,AGT,ALT,ABYT:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALBRT,BGT,BLT:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

ART<=X"55";--ART<=“01010101”A方向红灯亮

AGT<=X"40";--AGT<=“01000000”A方向绿灯亮

ALT<=X"15";--ALT<=“00010101”灯间歇闪烁

ABYT<=X"05";--ABYT<=“00000101”AB两方向黄灯亮

BRT<=X"65";--BRT<=“01100101”B方向红灯亮

BGT<=X"30";--BGT<=“00110000”B方向绿灯亮

BLT<=X"15";--BLT<=“00010101”B方向灯闪烁

PROCESS(CLR,CLK,M,S)

BEGIN

IFCLR='1'THENAT1<=X"01";BT1<=X"01";

ELSIF(CLK'EVENTANDCLK='1')THEN

IFM="000"THENAT1<=X"01";BT1<=X"51";--M=0时,A方向的计时器计时,B方向的红灯亮

ENDIF;

IFM="001"THENAT1<=X"01";BT1<=X"06";--M=1时,A方向的计时器计时,B方向绿灯亮

ENDIF;

IFM="010"THENAT1<=X"41";BT1<=X"01";--B方向的计时器计时,A方向的黄灯亮

ENDIF;

IFM="011"THENAT1<=X"06";BT1<=X"01";--B方向的计时器计时,A方向的红灯亮

ENDIF;

IFM>="100"THEN

IF(AT1=X"01")OR(BT1=X"01")THEN

CASESIS

WHEN"000"=>AT1<=ALT;BT1<=BRT;--当S=0时,AB两方向的计时器计时,A方向车左转,B方向的红灯亮

WHEN"001"=>AT1<=ABYT;--当S=1时,A方向计时器计时,A方向黄灯亮

WHEN"010"=>AT1<=AGT;--当S=2时,A方向计时器计时,A方向绿灯亮

WHEN"011"=>AT1<=ABYT;--当S=3时,AB两方向黄灯亮,A方向计时器计时

WHEN"100"=>AT1<=ART;BT1<=BLT;--当S=4时,A方向计时,红灯亮,B方向车左转,B方向计时器计时

WHEN"101"=>BT1<=ABYT;--当S=5时,B方向计时器计时,AB两方向黄灯亮

WHEN"110"=>BT1<=BGT;--当S=6时,B方向计时器计时,B方向绿灯亮

WHEN"111"=>BT1<=ABYT;--当S=7时,B方向计时器计时,AB两方向车右转

WHENOTHERS=>AT1<=AT1;BT1<=BT1;

ENDCASE;

ENDIF;

IFAT1/=X"01"THEN

IFAT1(3DOWNTO0)="0000"THEN

AT1(3DOWNTO0)<="1001";--第四位数码管显示

AT1(7DOWNTO4)<=AT1(7DOWNTO4)-1;高四位数码管减一显示

ELSEAT1(3DOWNTO0)<=AT1(3DOWNTO0)-1;低四位数码管减一显示

AT1(7DOWNTO4)<=AT1(7DOWNTO4);高四位数码管显示不变

ENDIF;

ENDIF;

IFBT1=X"01"THEN

IFBT1(3DOWNTO0)="0000"THEN

BT1(3DOWNTO0)<="1001";--B方向计数器低四位数码管显示‘9’

BT1(7DOWNTO4)<=BT1(7DOWNTO4)-1;--B方向计数器高四位数码管减一计数

ELSEBT1(3DOWNTO0)<=BT1(3DOWNTO0)-1;-B方向计数器低四位数码管减一计数

BT1(7DOWNTO4)<=BT1(7DOWNTO4);

ENDIF;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

AT<=AT1;

BT<=BT1;

ENDJTD_2;

该模块是为节省资源而设的,实验中有四个LED七段数码管显示计数,点亮一个LED需电流5-50mA,同时点亮4个LED,CPLD可能无法负荷这样的电流驱动,而且功率太大,散热也是问题。

同时这么做也容易造成电路被烧毁,因此需要逐个循环点亮。

又为使显示结果持续不致闪烁抖动,只需每个扫描频率超过人眼视觉暂留频率24Hz以上,就能达到。

选择1kHz作为时钟,分到4个数码管,每个数码管50Hz(大于24Hz),故不会有闪烁。

该模块的功能仿真波形图如图4-4所示

图4-4功能仿真

4.4译码驱动模块JTD_LIGHT的设计

译码驱动模块根据控制信号,驱动交通灯的显示。

该模块的源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJTD_LIGHTIS

PORT(

CLR:

INSTD_LOGIC;

M,S:

INSTD_LOGIC_VECTOR(2DOWNTO0);

ABL:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDJTD_LIGHT;

ARCHITECTUREJTD_3OFJTD_LIGHTIS

SIGNALLT:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

PROCESS(CLR,S,M)

BEGIN

IFCLR='1'THENLT<="00000000";--清'0'时系统状态全部处于关闭状态

ELSEIFM="000"THENLT<="10000001";

ENDIF;

IFM="001"THENLT<="00100001";

ENDIF;

IFM="010"THENLT<="00011000";

ENDIF;

IFM="011"THENLT<="00010010";

ENDIF;

IFM>="100"THEN

CASESIS--八种情况下的状况显示

WHEN"000"=>LT<="00010100";

WHEN"001"=>LT<="10000001";

WHEN"010"=>LT<="01000001";

WHEN"011"=>LT<="00100001";

WHEN"100"=>LT<="01000001";

WHEN"101"=>LT<="00011000";

WHEN"110"=>LT<="00010100";

WHEN"111"=>LT<="00010010";

WHENOTHERS=>LT<=LT;

ENDCASE;

ENDIF;

ENDIF;

ENDPROCESS;

ABL<=LT;

ENDJTD_3;

该模块的功能仿真波形图如图4-5:

图4-5功能仿真

4.5显示模块JTD_DIS的设计

显示模块用来显示倒计时时间和系统的工作状态。

其输出用来驱动六位数码管,其中四位用于显示倒计时时间,两位显示工作状态,采用动态扫描显示。

该模块的源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJTD_DISIS

PORT(

CLK1K,CLK,CLR:

INSTD_LOGIC;

M:

INSTD_LOGIC_VECTOR(2DOWNTO0);

AT,BT:

INSTD_LOGIC_VECTOR(7DOWNTO0);

LED:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

SEL:

OUTSTD_LOGIC_VECTOR(2DOWNTO0)

);

ENDJTD_DIS;

ARCHITECTUREJTD_4OFJTD_DISIS

SIGNALOU,STL,STH,MM:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALDIS,DS:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALSL:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

MM<="0"&M;

STH<=X"A";

PROCESS(CLR,CLK1K)

BEGIN

IFCLR='1'THENSL<="000";

ELSIF(CLK1K'EVENTANDCLK1K='1')THEN

IFSL="101"THENSL<="000";--清'0'

ELSESL<=SL+1;--计数

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(SL)

BEGIN

CASESLIS--数码管的位选

WHEN"000"=>OU<=BT(3DOWNTO0);

WHEN"001"=>OU<=BT(7DOWNTO4);

WHEN"010"=>OU<=AT(3DOWNTO0);

WHEN"011"=>OU<=BT(7DOWNTO4);

WHEN"100"=>OU<=STL;

WHEN"101"=>OU<=STH;

WHENOTHERS=>OU<=X"0";

ENDCASE;

ENDPROCESS;

PROCESS(OU)

BEGIN

CASEOUIS--数码管的译码

WHENX"0"=>DS<="00111111";--显示'0'

WHENX"1"=>DS<="00000110";--显示'1'

WHENX"2"=>DS<="01011011";--显示'2'

WHENX"3"=>DS<="01001111";--显示'3'

WHENX"4"=>DS<="01100110";--显示'4'

WHENX"5"=>DS<="01101101";--显示'5'

WHENX"6"=>DS<="01111100";--显示'6'

WHENX"7"=>DS<="00000111";--显示'7'

WHENX"8"=>DS<="01111111";--显示'8'

WHENX"9"=>DS<="01101111";--显示'9'

WHENOTHERS=>DS<="00000000";

ENDCASE;

ENDPROCESS;

PROCESS(MM,CLK)

BEGIN

IFMM>=X"4"THENSTL<=X"5";--数码管产生进位

ELSESTL<=MM+1;

ENDIF;

IFCLR='1'THENDIS<=X"00";

ELSIFMM>=X"4"THENDIS<=DS;

ELSIFSL<="100"THEN

IFCLK='0'THENDIS<=DS;

ELSIFDIS<=X"00"THEN

ENDIF;

ELSEDIS<=DS;

ENDIF;

ENDPROCESS;

LED<=DIS(6DOWNTO0);

SEL<=SL;

ENDJTD_4;

该模块的功能仿真波形图如图4-6所示

图4-6功能仿真

4.6分频模块JTD_FQU的设计

本系统提供动态扫描需要的1kHz的脉冲,而系统时钟需要1Hz的脉冲。

分频器主要为系统提供所需的时钟脉冲。

该模块将1kHz的脉冲进行分频,产生1S的方波,作为系统时钟信号和特殊情况下的倒计时闪烁信号。

其源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJTD_FQUIS

PORT(

CLK1K:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC

);

ENDJTD_FQU;

ARCHITECTUREJTD_5OFJTD_FQUIS

SIGNALQ:

STD_LOGIC_VECTOR(9DOWNTO0);

BEGIN

PROCESS(CLK1K)

BEGIN

IF(CLK1K'EVENTANDCLK1K='1')THENQ<=Q+1;--计数

ENDIF;

ENDPROCESS;

CLK<=Q(9);

ENDJTD_5;

该模块的时序仿真图如图4-7所示