EDA设计自动电子钟.docx

《EDA设计自动电子钟.docx》由会员分享,可在线阅读,更多相关《EDA设计自动电子钟.docx(10页珍藏版)》请在冰豆网上搜索。

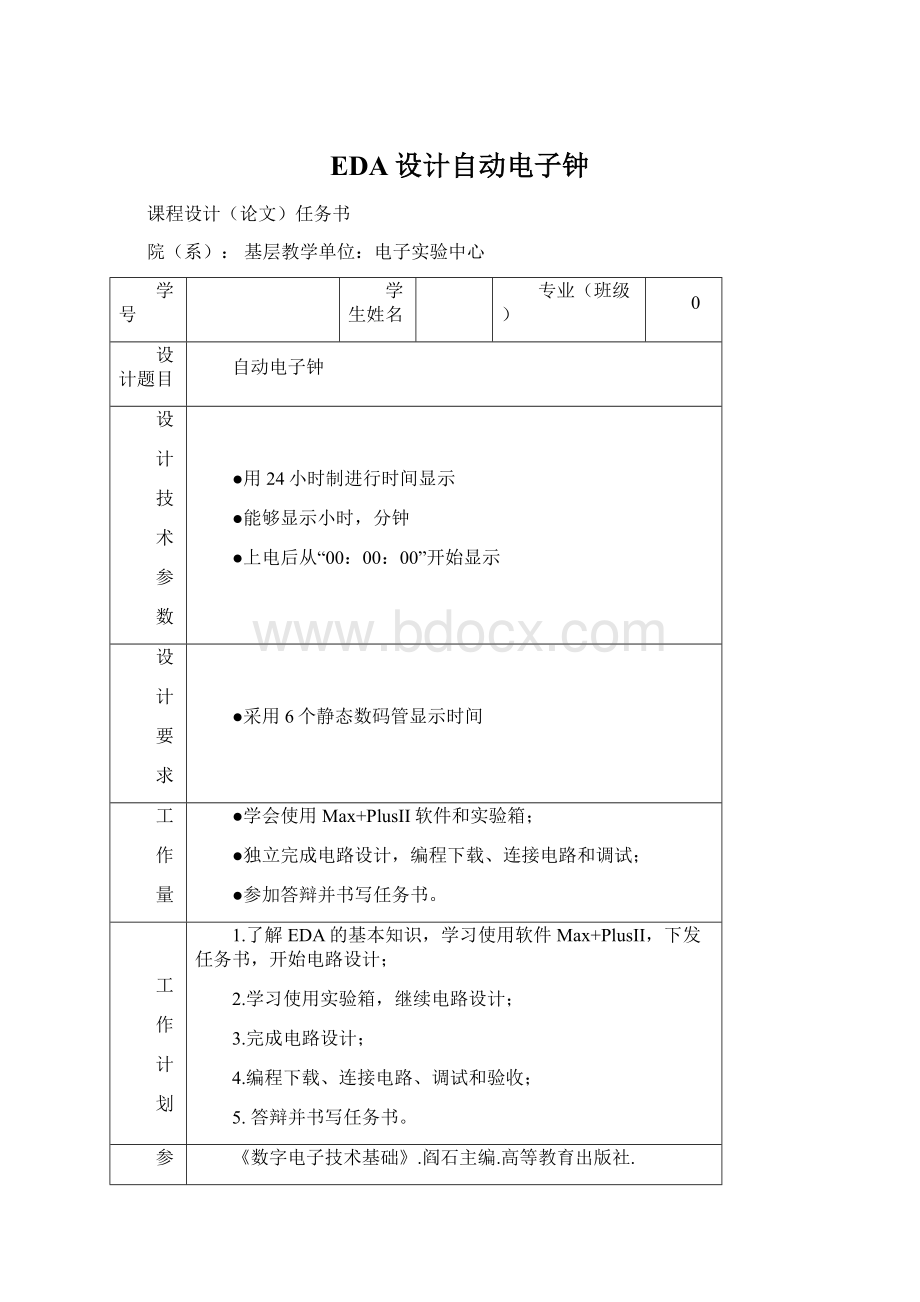

EDA设计自动电子钟

课程设计(论文)任务书

院(系):

基层教学单位:

电子实验中心

学号

学生姓名

专业(班级)

0

设计题目

自动电子钟

设

计

技

术

参

数

●用24小时制进行时间显示

●能够显示小时,分钟

●上电后从“00:

00:

00”开始显示

设

计

要

求

●采用6个静态数码管显示时间

工

作

量

●学会使用Max+PlusII软件和实验箱;

●独立完成电路设计,编程下载、连接电路和调试;

●参加答辩并书写任务书。

工

作

计

划

1.了解EDA的基本知识,学习使用软件Max+PlusII,下发任务书,开始电路设计;

2.学习使用实验箱,继续电路设计;

3.完成电路设计;

4.编程下载、连接电路、调试和验收;

5.答辩并书写任务书。

参

考

资

料

《数字电子技术基础》.阎石主编.高等教育出版社.

《EDA课程设计指导书》.

指导教师签字

基层教学单位主任签字

说明:

此表一式四份,学生、指导教师、基层教学单位、系部各一份。

2012年12月12日

第一章自动电子钟设计说明…………………………………………………………2

1.1设计思路…………………………………………………………………………2

1.2模块介绍…………………………………………………………………………2

1.3真值表…………………………………………………………………………3

第二章原理图……………………………………………………………………………5

第三章波形仿真图……………………………………………………………………7

第四章管脚锁定及硬件连线…………………………………………………………9

第五章总结……………………………………………………………………………10

参考文献…………………………………………………………………………………11

燕山大学评审意见表……………………………………………………………………12

第一章自动电子钟设计说明

1.1设计思路

这个自动电子钟的基本功能为采用6个静态数码管显示时、分、秒,其中时、分、秒的显示分别对应两个静态数码管。

秒钟利用60进制循环计数器(使用2个10进制计数器74160并行接成),从00到59后产生进位信号到分钟,并重新循环秒钟;分钟构成原理与秒钟相同,同样在进位后,并重新循环;时钟则采用24进制循环计数器(使用2个10进制计数器74160并行接成),在状态循环到23后置00,达到自动电子钟整体循环的功能,而74160的脉冲信号用1HZ提供,则基本周期为1秒,为电子钟的变化周期。

附加功能为整点报时:

采用1个10进制计数器74160自接成5进制计数器,作为蜂鸣器的触发时间控制,而触发信号则通过分钟向时钟进位时,自己整体置0,这个条件来控制。

1.2模块介绍

74160十进制计数器

LDN置数端

A、B、C、D输入端

ENT、ENP使能端

CLRN清零端

CLK时钟信号输入端

QA、QB、QC、QD输出端

RCO进位输出端

1.3真值表

1、74160十进制计数器

输入

输出

CLK

LDN

CLRN

ENP

ENT

D

C

B

A

QD

QC

QB

QA

RCO

×

×

L

×

×

L

L

L

L

L

↑

L

H

×

×

d

c

b

a

d

c

b

a

*

↑

H

H

×

L

QD

QC

QB

QA

*

↑

H

H

L

×

QD

QC

QB

QA

L

↑

H

H

H

H

L

L

L

L

L

↑

H

H

H

H

L

L

L

H

L

↑

H

H

H

H

L

L

H

L

L

↑

H

H

H

H

L

L

H

H

L

↑

H

H

H

H

L

H

L

L

L

↑

H

H

H

H

L

H

L

H

L

↑

H

H

H

H

L

H

H

L

L

↑

H

H

H

H

L

H

H

H

L

↑

H

H

H

H

H

L

L

L

L

↑

H

H

H

H

H

L

L

H

H

2、或非门

A

B

Y

0

0

1

0

1

0

1

0

0

1

1

0

3、或门

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

1

4、与门

A

B

Y

0

0

0

0

1

0

1

0

0

1

1

1

5、非门

A

Y

0

1

1

0

第二章原理图

1、秒钟:

60进制循环计数器(由2个74160采用整体置数法接成)

2、分钟:

同秒钟

3、时钟:

24进制循环计数器(由2个74160采用整体置数法接成)

4、整点报时:

5进制循环计数器(由1个74160采用整体置数法接成)

5、整体电路如下

第三章波形仿真图

1、秒钟个位向十位进位(1D3→1D4)

2、秒钟十位向分钟个位进位(1D6→2D0)

3、分钟个位向十位进位(2D3→2D4)

4、分钟十位向时钟个位进位(2D6→3D0)

5、时钟个位向十位进位(3D3→3D4)

第四章管脚锁定及硬件连线

管脚名称

引脚pin值

备注(部分硬件连线)

CLK

8

1D0

127

1D1

128

1D2

131

1D3

132

1D4

133

1D5

134

1D6

135

2D0

139

2D1

140

2D2

141

2D3

142

2D4

143

2D5

144

2D6

147

3D0

190

接到试验箱的3D0

3D1

191

接到试验箱的3D1

3D2

192

接到试验箱的3D2

3D3

193

接到试验箱的3D3

3D4

195

接到试验箱的3D4

3D5

196

接到试验箱的3D5

3D6

197

接到试验箱的3D6

3D7

198

接到试验箱的3D7

DS1

94

DS2

95

DS3

96

DS4

97

3

DS5

99

DS6

100

FM

38

第五章总结

参考文献

1、阎石数字电子技术基础高等教育出版社2010年

2、张强、周莲莲、郑兆兆EDA课程设计B指导书燕山大学教务处2010年

课程设计评审意见表

指导教师评语:

①该生学习态度(认真较认真不认真)

②该生迟到、早退现象(有无)

③该生依赖他人进行设计情况(有无)

平时成绩:

指导教师签字:

2011年12月16日

图面及其它成绩:

答辩小组评语:

①设计巧妙,实现设计要求,并有所创新。

②设计合理,实现设计要求。

③实现了大部分设计要求。

④没有完成设计要求,或者只实现了一小部分的设计要求。

答辩成绩:

组长签字:

2012年12月12日

课程设计综合成绩:

答辩小组成员签字:

2012年12月12日