EP1C6Q240C8封装和部分引脚的功能分析教程文件.docx

《EP1C6Q240C8封装和部分引脚的功能分析教程文件.docx》由会员分享,可在线阅读,更多相关《EP1C6Q240C8封装和部分引脚的功能分析教程文件.docx(10页珍藏版)》请在冰豆网上搜索。

EP1C6Q240C8封装和部分引脚的功能分析教程文件

EP1C6Q240C8封装和部分引脚的功能分析

EP1C6Q240C8封装和部分引脚的功能分析

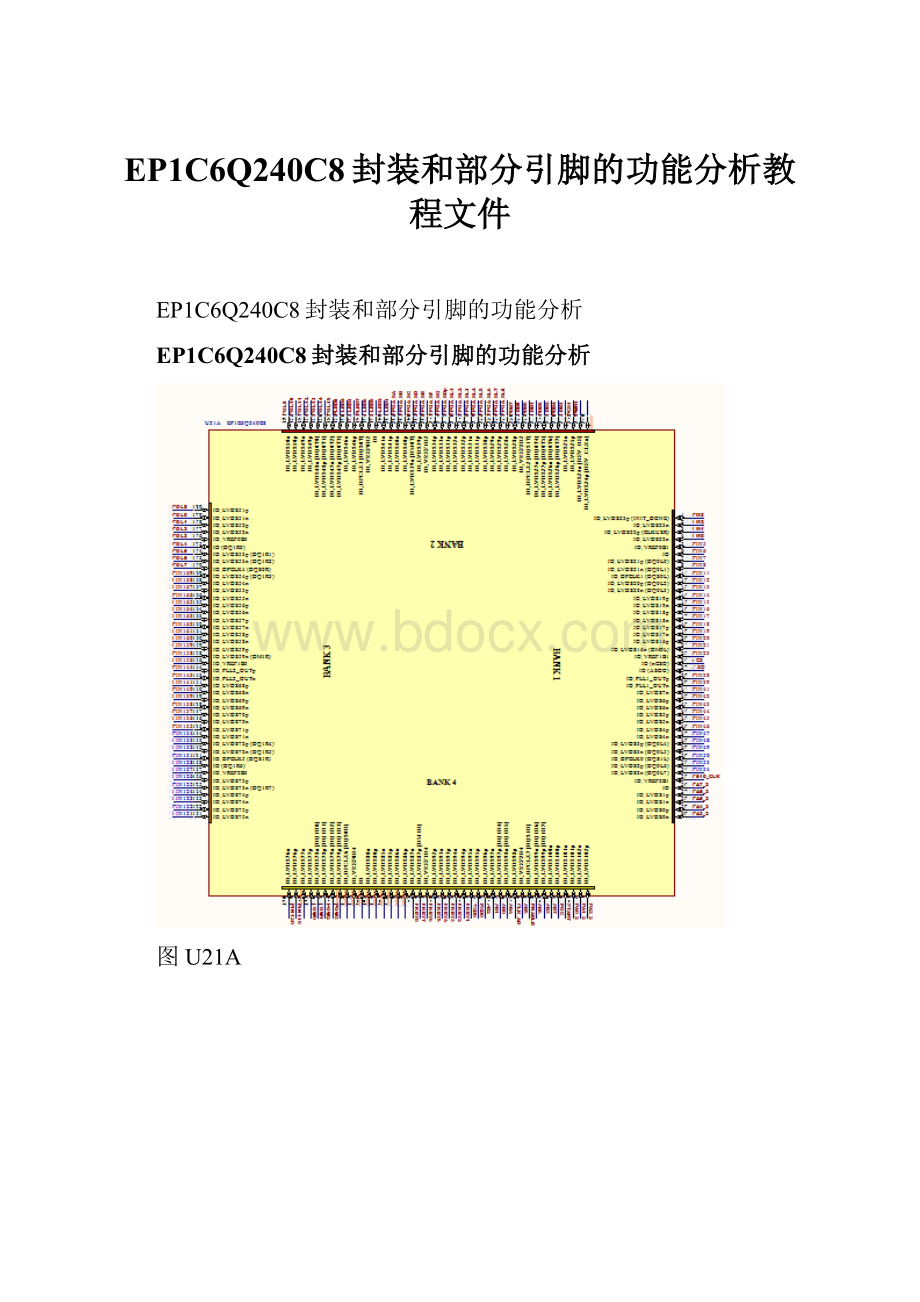

图U21A

图U21B

图U21C

图U21D

第一部分:

封装

图U21A、U21B、U21C、U21D表示的是同一块芯片EP1C6Q240C8,有240个引脚,采用的是PQFP封装(即PlasticQuadFlatPackage,塑料方块平面封装),PQFP封装的芯片的四周均有引脚,而且引脚之间距离很小,管脚也很细,一般大规模或超大规模集成电路采用这种封装形式。

用这种形式封装的芯片必须采用SMT(SurfaceMountTechnology,表面组装技术)将芯片边上的引脚与主板焊接起来。

对于SMT技术,个人理解,即表面组装技术,一般用来焊接一些引脚在几百以上的芯片,比如说BGA,PGA一般都采用这种技术;

例如笔记本主板上的intel北桥芯片,一般都采用球形封装,又如比较古老的Intel965底部球形引脚大约有600多个,现在笔记本流行用的P43、P45、P55、X58,从P43一代引脚多达几千个甚至更多,这样做的好处是节约面积,坏处是测试的时候比较麻烦,像BGA这种封装的芯片一般焊上去之后,顶部要引出几个接点,以防止在使用过程中坏掉,方便用万用表或者示波器来测试各个通路便于修理。

对于这几种类型的芯片,除了PQFP少数罕见的高手能手工焊接之外,一般都采用贴片机来进行专门的焊接工作。

这里简单介绍一下这两种封装:

PQFP/PFP封装具有以下特点

1.适用于SMD表面安装技术在PCB电路板上安装布线。

2.适合高频使用。

2.操作方便,可靠性高。

3.芯片面积与封装面积之间的比值较小。

4.Intel系列CPU中80286、80386和某些486主板采用这种封装形式。

这里的SMD表示的是贴片组装器件;

BGA球栅阵列封装

随着集成电路技术的发展,对集成电路的封装要求更加严格。

这是因为封装技术关系到产品的功能性,当IC的频率超过100MHz时,传统封装方式可能会产生所谓的“CrossTalk(串扰)”现象,而且当IC的管脚数大于208Pin时,传统的封装方式有其困难度。

因此,除使用QFP封装方式外,现今大多数的高脚数芯片(如图形芯片与芯片组等)皆转而使用BGA(BallGridArrayPackage)封装技术。

BGA一出现便成为CPU、主板上南/北桥芯片等高密度、高性能、多引脚封装的最佳选择。

第二部分:

电路图

关于原理图:

当我们把原理图元件库做好以后,在原理图中,对于已有的原理图,我们可以选择makelibrary选项即可生成要引用的原理图元件库,我们可以使用自动编号来对每隔模块进行编号,也可以手动的进行编号,然后在工具选项卡中找到footprintsmanager可以用来检查各个器件的封装,若发现器件没有封装,可以在library中找一个与该器件引脚数目一样的同类型的芯片封装来对该器件进行封装操作;封装完成之后进行DRC检测,然后更新到PCB,由于目前只做原理图分析,这里就不做详细介绍了。

在原理图中,细心的人会发现,不能单独的看只看U21A这块“芯片”,其实这只是芯片的一部分,为了便于观察,我们把电源、时钟频率、JTAG下载口和AS下载口单独出来作为4大部分;

一、U21A是该芯片的主体部分:

即EP1C6Q240C8主体部分,该部分引脚有点多(稍后介绍);

二、U21B模块表示的是JTAG和AS下载电路:

1、AS简介:

AS(ActiveSerial)是FPGA重要的配置方式,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

其他配置方式还有JTAG、PS等。

2、JTAG模式

JTAG主要用于芯片内部测试。

TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

在EP1C6Q240C8芯片上,我们可以找到对应的是148、147、155、149这四个引脚,JTAG是串行接口,使用打印口的简单JTAG电缆,利用的是打印口的输出带锁存的特点,使用软件通过I/O产生JTAG时序。

由JTAG标准决定,通过JTAG写/读一个字节要一系列的操作,根据我的分析,使用简单JTAG电缆,利用打印口,通过JTAG输出一个字节到目标板,平均需要43个打印口I/O,在我机器上(P41.7G),每秒大约可进行660K次I/O操作,所以下载速度大约在660K/43,约等于15KByte/S.对于其他机器,I/O速度大致相同,一般在600K~800K.

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程后再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对PSD芯片内部的所有部件进行编程。

在嵌入式系统设计中,一些高档的微处理器都带有JTAG接口,方便多目标系统进行测试,同时还可以实现flash编程。

(即norflash容量较小,相当于内存,nandflash相当于计算机上的硬盘,容量较大)

3、U21C模块表示的是该芯片的电源和接地

如果没记错的话,一般芯片都采用的是TTL电平,这种电平能提供几种不同的电压来满足不同的需要。

这个在数电里面应用比较广泛。

图中有14个引脚是接的+1.5V,另外12个引脚接的是+3.3V,我们可以把电源的供电部分用一个电容接到地,这样的好处是能过滤掉电源内部产生的一些高频串扰信号,接地部分有的是模拟地,有的是数字地,这样单独起来的好处是防止信号干扰,中间用一个电感来连接,这样能阻碍高频信号直接耦合;

4、U21D表示的是时钟信号输入

图中我们发现,对于四个时钟输入引脚我们只用了CLK2一个引脚,这样的好处是以后我们还能够扩展焊接一些不同频率的信号留作备用;

时钟信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。

时钟信号是指有固定周期并与运行无关的信号量,时钟频率(clockfrequency,CF)是时钟周期的倒数。

时钟边沿触发信号意味着所有的状态变化都发生在时钟边沿到来时刻。

在边沿触发机制中,只有上升沿或下降沿才是有效信号,才能控制逻辑单元状态量的改变。

至于到底是上升沿还是下降沿作为有效触发信号,则取决于逻辑设计的技术。

在FPGA中还有电平触发方式,这里就不作介绍,仅做了解。

三、关于EP1C6Q240C8的内部功能部件:

第二部分我从原理图的角度来分析了这块芯片,下面我们就从整体上来观察整个芯片的

一、EP1C6核心板为基于Altera,Cyclone器件的嵌入式系统开发提供了一个

很好的硬件平台,它为开发人员提供以下资源:

1主芯片采用AlteraCyclone器件EP1C6Q240C8

2EPCS1I8配置芯片

34个用户自定义按键

44个用户自定义LED

51个七段码LED

6标准AS编程接口和JTAG调试接口

750MHz高精度时钟源

8三个高密度扩展接口

9系统上电复位电路

10支持+5V直接输入,板上电源管理模块

系统主芯片采用240引脚、贴片封装的E1C6FPGA,它拥有6030个LE,

26个M4K片上RAM(共计239616bits),2个高性能PLL以及多达185个用户

自定义IO。

同时,系统还可以根据用户不同的设计需求来更换其它不同系列

的核心板,如:

EP1C12、EP2C20、EP3C25等。

所以,不管从性能上而言,

还是从系统灵活性上而言,无论您是初学者,还是资深硬件工程师,它都会

成为您的好帮手。

EP1C6核心板系统功能框架图:

FPGA开发平台提供了丰富的资源供学生或开发人员学习使用,资源包

括接口通信、控制、存储、数据转换以及人机交互显示等几大模块,接口通

信模块包括SPI接口、IIC接口、VGA接口、RS232接口、USB接口、PS2键

盘/鼠标接口、1-Wire接口等;存储模块包括EEPROM存储器模块等;数据

转换模块包括串行ADC、DAC以及音频CODE等;人机交互显示模块包括8

个按键、16个LED发光二极管显示、1602字符型点阵LCD、8位动态7段码管、

实时时钟、SD卡等。

上述的这些资源模块既可以满足初学者入门的要求,

也可以满足开发人员进行二次开发的要求。

EDA/SOPC实验开发平台提供的资源有:

1、标准配置核心板为EP1C6核心板(核心芯片为EP1C6Q240C8)。

可

更换EP2C20F484C8等其它核心板。

2、1602字符型液晶点阵。

3、RTC,提供系统实时时钟。

4、1个256色VGA接口。

5、1个标准串行接口。

6、1个USB设备接口,利用PDIUSBD12芯片实现USB协议转换。

7、基于SPI或IIC接口的音频CODEC模块。

8、1个蜂鸣器输出模块。

9、2个PS2键盘/鼠标接口。

10、串行ADC和串行DAC模块。

11、IIC接口的EEPROM存储器模块。

12、基于1-Wire接口的数字温度传感器。

13、8位动态七段码管LED显示。

14、16个用户自定义LED显示,8个用户自定义按键输出。

15、一个SD卡接口模块。

16、扩展接口,供用户高速稳定的自由扩展。

该芯片有逻辑单元LEs6030个、M4KMemoryBlocks26个、所有RAMBits239616约3MB、PLLs2个(即锁相环电路)、用户可用I/O口有185个。