第五章 大规模数字集成电路文档格式.docx

《第五章 大规模数字集成电路文档格式.docx》由会员分享,可在线阅读,更多相关《第五章 大规模数字集成电路文档格式.docx(17页珍藏版)》请在冰豆网上搜索。

时序

访问某地址单元的地址码有效,假如你想去访问的具体地址:

如A9~A0=0D3H=0011010011B,片选有效

=0,选中该片RAM为工作状态。

读/写操作有效:

=1,读出信息;

=0,写入信息;

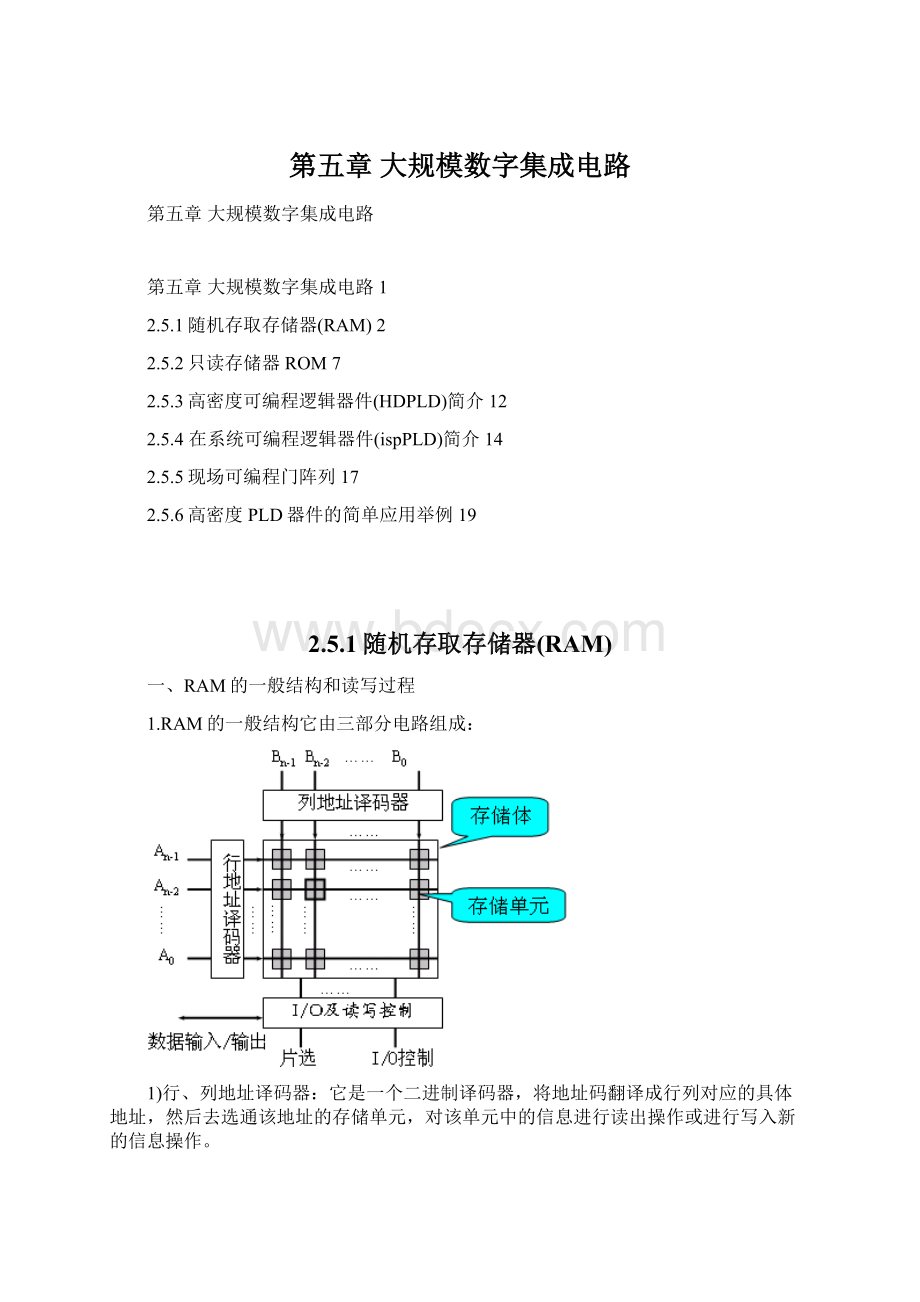

二、RAM中的存储单元

按照数据存取的方式不同,RAM中的存储单元分为两种:

静态存储单元—静态RAM(SRAM);

动态存储单元—动态RAM(DRAM)。

1.静态存储单元(SRAM):

它由电源来维持信息,如触发器,寄存器等。

静态存储单元(SRAM)的典型结构:

T5、T6、T7、T8都是门控管,只要栅极高电平,这些管子就工作在可变电阻区,当作开关。

其中,存储单元通过T5、T6和数据线(位线)相连;

数据线又通过T7、T8和再经输入/输出缓冲电路和输入/输出线相连接,以实现信息的传递和交换。

写入信息的操作过程,在第一次写入信息之前,存储单元中的信息是随机信息。

假定要写入信息“1”:

1)地址码加入,地址有效后,相对应的行选线X和列选线Y都为高电平,T5、T6、T7、T8导电;

2)片选信号

有效(低电平);

3)写入信号有效,这时三态门G2、G3为工作态,G1输出高阻态,信息“1”经G2、T7、T5达到Q端;

经G3反相后信息“0”经T8、T6达到

。

T4导电,T3截止,显然,信息“1”已写入了存储单元。

假定要读出信息“1”:

1)访问该地址单元的地址码有效;

2)片选有效

=0;

3)读操作有效R/

=1;

此时:

三态门G1工作态,G2、G3高阻态,存储单元中的信息“1”经T5、T7、G1三态门读出。

除上述NMOS结构的静态SRAM以外,还有以下几种类型的SRAM。

CMOS结构的SRAM:

功耗更加低,存储容量更加大。

双极型结构SRAM:

功耗较大,存取速度更加快。

2.动态存储单元(DRAM)

静态存储单元存在静态功耗,集成度做不高,所以,存储容量也做不大。

动态存储单元,利用了栅源间的MOS电容存储信息。

其静态功耗很小,因而存储容量可以做得很大。

静态RAM功耗大,密度低,动态RAM功耗小,密度高。

动态RAM需要定时刷新,使用较复杂。

动态存储单元(DRAM)的典型结构:

门控管T3、T4、T5、T6、T7、T8,C1、C2为MOS电容。

DRAM的读/写操作过程:

1)访问该存储单元的地址有效;

2)片选信号有(未画);

3)发出读出信息或写入新信息的控制信号。

读出操作时,令原信息Q=1,C2充有电荷,地址有效后,行、列选取线高电平;

加片选信号后,送读出信号R=1,W=0;

T4、T6、T8导电,经T4、T6、T8读出。

写入操作时,假定原信息为“0”,要写入信息“1”,该存储单元的地址有效后,X、Y为高电平;

在片选信号到达后,加写入命令W=1,R=0,即“1。

信息经T7、T5、T3对C2充电。

充至一定电压后,T2导电,C1放电,T1截止,所以,Q变为高电平,“1”信息写入到了该存储单元中。

如果写入的信息是“0”,则原电容上的电荷不变。

动态RAM的刷新:

由于DRAM靠MOS电容存储信息。

当该信息长时间不处理时,电容上的电荷将会因漏电等原因而逐渐的损失,从而造成存储数据的丢失。

及时补充电荷是动态RAM中一个十分重要的问题。

补充充电的过程称为“刷新”—Refresh,也称“再生”。

补充充电的过程:

加预充电脉冲

、预充电管T9、T10导电,C01,C02很快充电至VDD,

撤消后,C01,C02上的电荷保持。

然而进行读出操作:

地址有效,行、列选线X、Y高电平;

R=1,W=0进行读出操作,如果原信息为Q=“1”,说明MOS电容C2有电荷,C1没有电荷(即T2导电,T1截止);

这时C01上的电荷将对C2补充充电,而C02上的电荷经T2导电管放掉,结果对C2实现了补充充电。

读出的数据仍为,

,则DO=1。

实际上,在每进行一次读出操作之前,必须对DRAM按排一次刷新,即先加一个预充电脉冲,然后进行读出操作。

同时在不进行任何操作时,CPU也应该每隔一定时间对动态RAM进行一次补充充电(一般是2mS时间),以弥补电荷损失。

三、静态RAM的容量扩展(SRAM)

通常微处理器的数据总线为8位、16位或32位,而地址总线为16位或24位不等。

当静态RAM的地址线和数据线不能与微机相匹配时,可用地址线扩展、数据线扩展或地址和数据线同时进行扩展的方法加以解决。

1.RAM容量的扩展---位数扩展数据线扩展

如SRAM2114:

10位地址,4位数据线,其容量=210×

4=1024×

4=4096字位(4K)。

例:

用4K容量的RAM2114,实现一个容量为1024×

8(≈8K字位)字位容量的RAM。

解:

1024×

8字位容量,其地址仍是十位,故只要进行数据位扩展即可,选用RAM2114两片,将两片的地址线,读/写线及片选线并联,两片的位线分别作为高4位数据和低4位数据,组成8位的数据线即可。

扩展后的电路如图所示:

2.SRAM容量的扩展---字位扩展,地址扩展,数据位扩展。

用RAM2114,扩展成容量为4096×

8字位(32K)的RAM。

4096需要12位地址,而RAM2114只有10位地址,所以需要进行地址扩展,同时应该将一字4位,扩展成一字8位。

字的位扩展用前面方法,地址扩展用译码器完成,用8片RAM2114。

2.5.2只读存储器ROM

一、只读存储器的一般结构

容量=

字位=16字位ROM结构图:

地址译码器是一个二进制全译码电路,即是一个不可编程的“与”阵列。

存储体是一个“或”结构的阵列。

读出的信息内容如表所示:

从中可知:

ROM没有记忆电路,且由固定的“与”阵列和固定的“或”阵列组成,所以是一种组合逻辑电路。

如果“与”和“或”阵是可编程时,就是前面介绍的组合型可编程逻辑器件(PLD)了。

为此,ROM也可用简化图表示了。

表明PLD器件是由ROM逐步发展过来的。

二、只读存储器ROM的种类

根据不同的半导体制造工艺,或阵列的编程方式有多种。

存储器ROM种类通常按其编程工艺划分:

1.掩膜型只读存储器:

用掩膜工艺,生产厂在存储体中的字位线交叉处,根据用户要求的存储内容,制作半导体器件。

一旦制成,其内容就固定,无法更改,只供读出。

如家电中的洗衣机程序,电风扇程序都是固定的。

2.一次编程(改写)的只读存储器PROM:

可以编程一次,编程后内容就固定了,再无法更改。

在这种PROM中的存储体内,字位线的每个交叉点上都做上一个半导体器件。

3.可多次编程(改写)的只读存储器EPROM(紫外线擦除式可编程只读存储器UVEPROM:

UltraviolatErasableProgrammableROM):

这种ROM在每个字位线的交叉点都做上一个特殊的MOS器件。

一种是FAMOS(FloatinggateAvalancheInjunctionMOS);

另一种是SIMOS(StackedgateInjunctionMOS)。

它与普通MOS管不同的是有两个栅极,第一栅极与其它电极完全绝缘。

要求能控制管子导电或截止的思路是:

设法让栅极g1获取电子,并能控制电子释放。

当g1带上电子后,管子的开启电压将升高;

电子释放后,开启电压恢复正常。

栅极g1获取电子的方法是:

在漏源极间加上一定的编程电压VPP(该电压由制造时工艺决定),同时在控制栅极g2加上控制脉冲,此时在栅极下面的两个N+区间感应出电子,其中一些能量大的电子就会穿越SiO2层而达到栅极g1,g1积累了一定的电子后,它的开启电压将升高。

g1俘获电子后,该电子可以长期保留。

如果要使开启电压降为正常时,只要用紫外线或X射线照射该SIMOS管,让g1上的电子释放,管子的开启电压就恢复正常。

该半导体存储器在出厂时,栅极g1都不带电子,所以,字选线Wi高电平后,SIMOS导电,位线上信息为“0”,经三态门反相后,读出为“1”信息。

可见,未编程前,其信息为全“1”。

若要将某单元信息改写成“0”时,通常是用硬件编程器产生编程电压和编程高压脉冲,使栅极g1带上电子,开启电压升高,字选线Wi高电平后,SIMOS管截止,读出信息为“0”。

如果要对一片已写好的EPROM进行改写时,应将前面写入的内容擦除。

使EPROM信息重新恢复为全“1”后,进行第二次写入操作。

EPROM存储单元:

可见EPROM:

可多次编程,编程次数达100百次以上;

每次编程前,需先用UV擦除,时间约20分钟;

编程后需防空气中UV,数据可保存20年以上。

4.EEPROM(电擦除式可编程只读存储器EEPROM)

EEPROM的擦除只需电信号(高压编程电压和高压脉冲),且擦除速度快;

可以单字节擦除或改写,而EPROM只能整片擦除;

有些EEPROM可5V编程;

EEPROM既具有ROM器件的非易失性优点,又具备类似RAM器件的可读写功能(只不过写入速度相对较慢)。

隧道MOS管结构和符号:

制作在EEPROM上的器件是隧道MOS管,隧道MOS的导电机理与SIMOS相似,只是在栅漏区之间有一个厚度极薄的隧道区。

当漏极接地,栅极加上编程脉冲电压。

由于隧道区极薄,所以只要不高的电压,在该区将产生一个极强的电场,沟道中感应的电子在电场的作用下穿越SiO2层而达到栅极g1,这样隧道MOS管的开启电压升高。

要使g1电子释放(即擦除信息),只要将栅极接地,漏极加上编程电压,产生与原电场方向相反的电场,从而使g1上的电子释放。

由于器件中的第一栅极容易获得电子,该电子也容易释放,所以,这种ROM的编程比较方便。

现在用的很普遍。

EEPROM存储单元:

5.快闪存储器(FLASHMemory):

每个存储单元只需单个MOS管,因此其结构比EEPROM更加简单,存储容量可以做得更大,不能象EEPROM那样实现单字节擦除或改写,一般只能分页擦除或改写,根据器件容量大小,一页大小为128、256、512、64K字节不等。

快闪存储器中的叠栅MOS管的浮置栅极g1和衬底间的SiO2层更加薄,另外在源极区采用双级扩散工艺。

快闪存储器的编程和擦除机理都与EEPROM相似,即利用了“电子隧道效应”。

当g2接地,在源极加上编程脉冲,即会在浮栅与源极间产生隧道效应,使浮栅电子释放。

三、ROM的应用举例

用ROM产生各种逻辑函数:

依据是ROM由“与”阵列和可编程的“或”阵列组成,“与”阵列产生“与”项,然后由可编程的“或”阵列产生各种“与或”表达式。

试用EPROM2716将四位二进制码转换成格雷码。

EPROM2716有11条地址线,可以访问211=2048个存储单元,一个存储单元存放着8位的二进制信息,所以,其存储容量为2048×

8字位(2K字节)容量。

VPP是编程电压,

、

是片选、读/写或编程控制,见表。

思路是把四位二进制码作为EPROM2716的低四位地址输入,而把四位格雷码作为对应地址中的内容写入到EPROM中去即可。

见表所示。

B0,B1,B2,B3四位二进制码输入,G0,G1,G2,G3读出四位格雷码。

2.5.3高密度可编程逻辑器件(HDPLD)简介

一、基本情况

1.发展基础:

从门阵列的基础上发展起来;

2.内部基本电路:

集成电路内部集成了一系列的逻辑门、触发器和大量的可编程“与”阵列、可编程“或”阵列;

3.所采用的集成工艺CMOS技术、UVEPROM、EEPROM、FlashMemory、SRAM;

4.使用技术用户直接对器件内部结构进行逻辑编程操作;

5.主要特点:

①逻辑功能用编程实现,使数字电子系统电路的大部分硬件设计转化为软件设计(编程);

②具有众多数量的等效编程门数(几百~几百万门级),基本上可以满足各种数字电子系统的芯片化设计;

③速度很快,因为功能是由内部电路的硬件编程决定;

④用户不能直接使用,必须经开发软件编程→下载到具体的芯片上;

二、高密度可编程逻辑器件的分类

按编程工艺分:

熔丝和反熔丝工艺、UVEPROM工艺E2PROM、FlashMemory工艺SRAM编程工艺。

按编程方式分:

ISP方式(在系统可编程)、ICR方式(在电路配置方式)、硬件编程器编程方式。

按器件结构分:

CPLD器件、FPGA器件

常见名称:

EPLD—ErasableProgrammableLogicDevice

HDPLD—HighDensityProgrammableLogicDevice

LDPLD—LowDensityProgrammableLogicDevice

ispPLD—InSystemProgrammableProgrammableLogicDevice

CPLD—ComplexProgrammableLogicDevice

FPGA—FieldProgrammableLogicDevice

三、高密度可编程逻辑器件的结构各公司的产品结构不一定全同,但其基本结构相似。

高密度PLD器件的基本结构框图:

1.I/O单元

输入/输出电路,它包含输入、输出寄存器,三态门、多路选择器,输出摆率控制电路,边界扫描电路,其功能更加丰富。

2.基本逻辑单元块BLB

是实现逻辑功能的最小单位。

注意:

这部分各公司有不同的称呼,Lattice称通用逻辑阵列块(GLB—GenericLogicBlock),Altrra称逻辑元素(LE—LogicElement),Xilinx称为可配置逻辑块(CLB—ConfigrableLogicBlock)。

这些基本逻辑单元块的规模也各不相同,规模大时将对设计方便。

使用时,要根据不同的系统大小要求来选择。

3.可编程互连资源(PI—ProgrammableInterconnect)

它将各单元描述的功能连接起来,构成一个完整的数字系统,并将输入/输出连接到具体的I/O单元。

这部分的设计需要经验和工艺,PI设计的好坏将关系到PLD的使用效率,PLD器件的工作稳定等。

2.5.4在系统可编程逻辑器件(ispPLD)简介

由于在系统PLD器件种类很多,现以Lattice产品加以简介。

Lattice的ispLSI1016的结构框图

共有44条引脚,等效有2000个逻辑门,双列直插式封装。

其内部有:

1个全局布线区GRP(GlobalRoutingPool),1个时钟分配网络二个宏块(Magablock),宏块内部又有8个通用块GLB(GenericLogicBlock),1个输出布线区ORP(OutputRoutingPool),1个输入总线16个I/O口,2条输入引脚;

ispLSI1016内部信号来自I/O引脚的输入信号→输入总线→全局布线区(统一调度后)→分配给具体的GLB,而来自专用输入引脚的信号直接进入各自宏块的GLB,系统的逻辑功能主要决定于GLB。

各GLB的输出可以反馈至全局布线区,也可经过布线区后再分配给具体的I/O引脚;

系统时钟由时钟分配网络产生。

GLB结构分析:

它是ispLSI的标准逻辑块。

内有:

与阵列、乘积项共享阵列、可重构寄存器以及控制电路等四部分。

与阵列:

18个输入项,可编制成20个积项,乘积项共享阵列:

经过共享其它或门的输出,使GLB的每个输出最多拥有20个乘积项,以满足各种逻辑设计的要求;

可重构触发器:

可以有组合形输出或经触发器后输出(重构);

控制电路:

为时钟信号,系统复位信号,以及输出使能;

ispLSI电路的I/O单元电路:

I/O单元的几种配置:

纯输入,纯输出结构,双向I/O结构。

ispLSI1016的编程是在计算机控制下进行的。

计算机根据用户编写的源程序运行开发系统软件,产生相应的编程数据和编程命令,通过5线编程接口与ispLSI1016连接。

2.5.5现场可编程门阵列

一、集成度高达20000门/片以上SRAM工艺实现逻辑函数的原理

1.配置用的SRAM存储单元

2.两个SRAM控制的4/1数据选择器(M1、M0为SRAM的配置输出,A、B、C、D为4路输入,Z为输出)函数发生器电路(由四个SRAM输出控制二个变量的函数发生器)。

二、逻辑单元阵列LCA的总体结构

三、FPGA器件的配置(编程)

因为SRAM编程工艺具有易失性,失电后FPGA不具备某种功能,所以,上电时必须对FPGA进行配置,将编程信息装载进器件中。

2.5.6高密度PLD器件的简单应用举例

应用高密度PLD器件开发软件平台进行逻辑设计时,其软件编程中的逻辑设计输入可以采用HDL语言描述输入,原理图描述输入,状态图描述输入,波形图描述输入,以及混合描述输入法。

试在ISPSynario开发环境下,用ispLSI1016设计一个具有异步清零、同步保持的8421码计数的1000进制加法计数器。

根据要求,画出1000进制计数器的顶层电路原理图,1000进制由底层的三个十进制计数器组成。

十进制计数器用ABEL—HDL语言描述。

设clk→时钟输入,clr→异步清零输入,c_h→计数/保持输入。

q3、q2、q1、q0→计数器的输出信号。

十进制计数器ABEL—HDL语言描述:

为检查输入语句是否正确,编写测试矢量进行语法检查,逻辑化简,逻辑编译等操作。

测试矢量ABEL语言如下:

最后经仿真软件后的波形如图:

正确后经器件管脚锁定,将设地输入下载至ispLSI1016中。