我的第一次modelsim和quartus联调实验Word格式.docx

《我的第一次modelsim和quartus联调实验Word格式.docx》由会员分享,可在线阅读,更多相关《我的第一次modelsim和quartus联调实验Word格式.docx(13页珍藏版)》请在冰豆网上搜索。

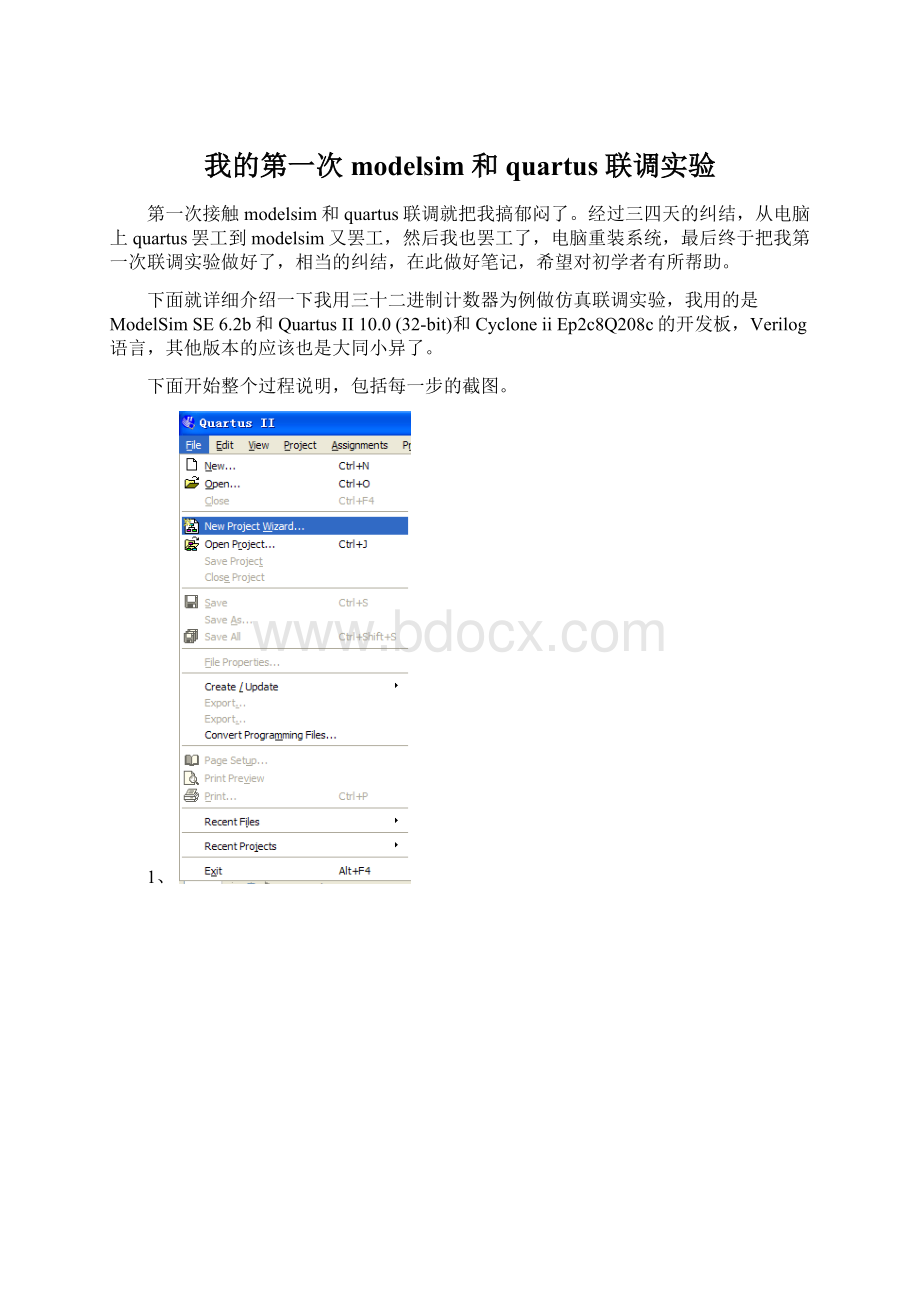

进入NewProjectWizard对话框后直接选择Next就可以了

图2

2、如图三,第一栏填写的是工程所保存的目录(注意不要是中文目录),第二栏是工程名称,填写第二栏是第三栏自动和第二栏相同。

注意这里工程名最好和HDL源文件的module名相同。

填完后直接点击Next进入下一界面。

下一界面是添加你已经编写好的HDL源文件加入这个工程,这里我们不用,我们直接点击Next,进入下一界面。

图3

3、选择器件界面,选择用的对于的器件就可以了。

然后点击Next。

4、EDA工具选择界面,仿真工具中选择ModelSim和VerilogHDL语言,然后点击Next,进入确认界面,如果设置没错的话就直接点击finishi,至此工程建立完成

5、设置仿真文件路径:

Tools——Options进入设置界面

6、在EDAToolOpinion栏中的ModelSim栏中指向ModelSim的安装路径,点击OK即可

7、点击左上角白色图标新建VerilogHDLFile文件

编辑HDL文件,代码如下:

modulecnt(dout,clk,data,rst,load);

output[4:

0]dout;

input[4:

0]data;

inputclk,rst,load;

reg[4:

0]dout=0;

always@(posedgerstorposedgeclk)

if(rst)

dout<

=0;

elseif(load)

dout<

=data;

else

=dout+1;

endmodule

然后保存并编译文件。

至此VerilogHDL文件已建立好,并且可以在建立工程的文件夹下看到simulation文件夹,专门保存仿真相关文件。

下面开始Testbench文件的编写。

6、Processing——Start——StartTestBenchTemplateWriter,之后就可以在simulation文件夹——modelsim文件夹下看到cnt.vt文件,就是Testbench文件,通过文本文件打开可以进行编写,代码如下:

`timescale10ns/1ps

modulecnt_test();

regclk;

reg[4:

0]data;

regload;

regrst;

wire[4:

0]dout;

cntc1(

.dout(dout),

.clk(clk),

.data(data),

.rst(rst),

.load(load)

);

initial

clk<

always

begin

#5clk<

=1'

b1;

b0;

end

initial

begin

data<

=5'

h15;

load<

rst<

=1;

#10rst<

#50data<

h1d;

#50load<

#500

$finish;

7、设置仿真:

Assignments——Settings…

得到如下界面:

选择NativeLikesettings中的Compiletestbench,点击TestBenches…进入TestBenches对话框如下图:

选择New…进入NewTestBenchSettings界面:

第一栏填写Testbenchname我们直接填写cnt,下面Toplevelmoduleintestbench填写和我们编写的testbench文件中的module一样的名字(这里默认第一栏填写后第二栏同第一栏,我们把第二栏修改成cnt_test(和testbench文件中的module一样的名字)方便后面modelsim中区别)。

勾选上Usetestbench……复选框,然后在Designinstancename……中填c1(这里默认是i1,我们改写成c1,和testbench程序中我用红色加黑标注的一致,即调用模块)在下面Testbenchfiles中添加刚刚编写的testbench文件,并点击Add(图示是没有点击Add的状态)。

然后点击各种OK后设置完成了。

推出后编译一下。

8、开始仿真ToolsRunEDASimulationTool——EDAGatelevelSimulation,在弹出对话框中点击Run即可开始联调,自动打开Modelsim

9、弹出finish对话框,选择否,否则自动结束了。

10、得到仿真结果:

可以通过右键cnt_test——Add添加波形,数据流等。

放大仿真波形可以看到我们的仿真结果