S3C6410各引脚的功能引脚号查询Word文档下载推荐.docx

《S3C6410各引脚的功能引脚号查询Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《S3C6410各引脚的功能引脚号查询Word文档下载推荐.docx(50页珍藏版)》请在冰豆网上搜索。

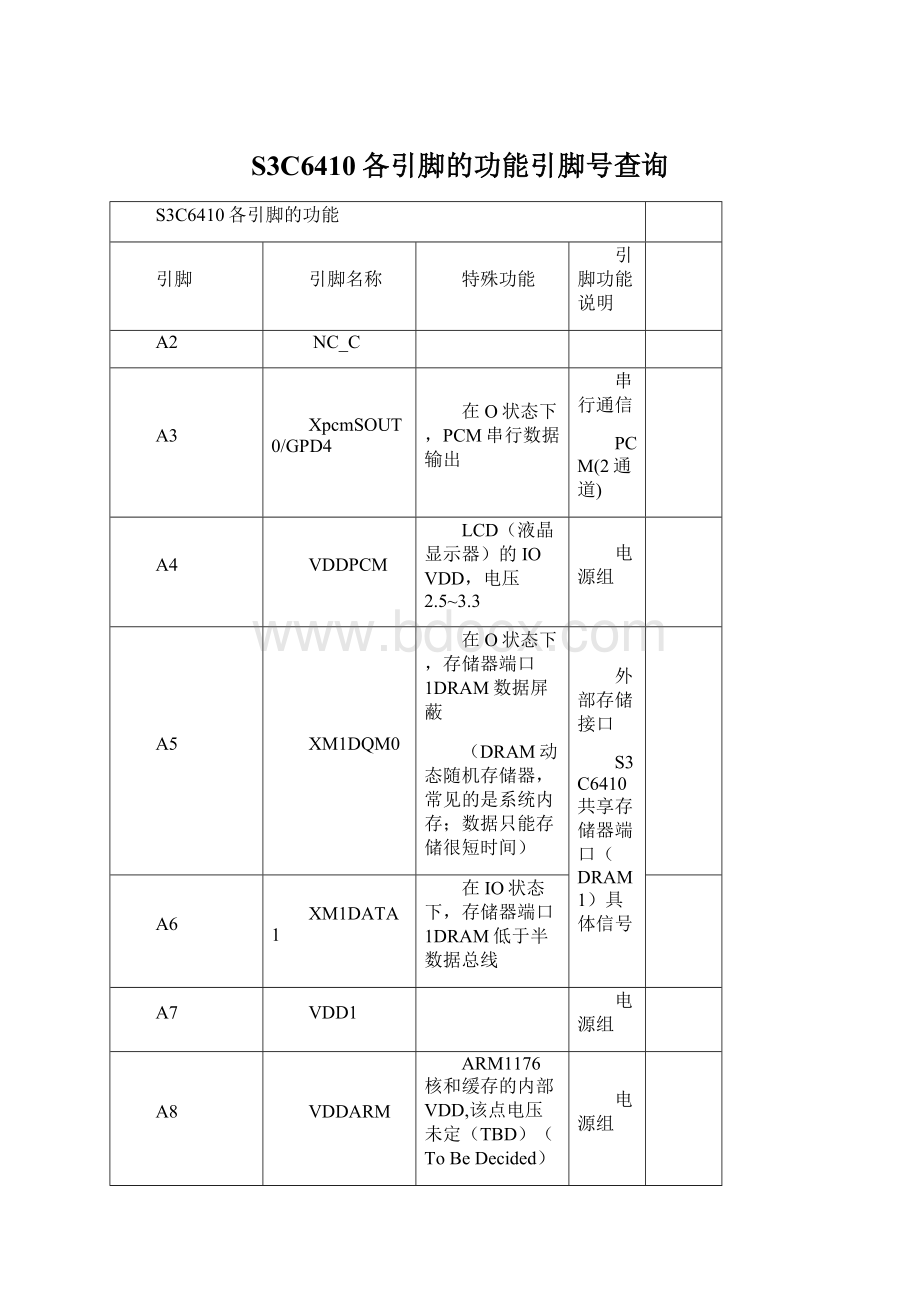

A16

XmmcCMD1/GPG6

在IO状态下,命令/响应(SD/SDIO/MMC卡接口通道1)

A17

CmmcCDN0/GPG0

在I状态下,卡删除(SD/SDIO/MMC卡接口通道0)

A18

CmmcCLK0/GPG0

在O状态下,时钟(SD/SDIO/MMC卡接口通道0)

A19

XspiMOSI0/

GPC2

在IO状态下,SPI主设备输出线路

SPI(2通道)

A20

Xi2cSCL/

GPC8

在IO状态下,IIC总线时钟

(IIC总线具体信号)

A21

XuTXD2/

GPB1

在O状态下,UART2传输数据输出

(UART具体信号)

A22

XuRTSN0/

GPA3

在O状态下,UART0请求发送数据信号

A23

XuTXD0/

GPA1

在O状态下,UART0传输数据输出

A24

NC_D

B1

NC_B

B2

XpcmSIN1/

GPE3

在I状态下,PCB串行数据输入

B3

XpcmEXTCLK1/GPE1

在I状态下,可选参考时钟

B4

XpcmSIN0/

GPD3

B5

XpcmEXTCLK0/GPD1

B6

XM1DATA0

外部存储器接口

(S3C6410共享存储器端口)

B7

XM1DATA3

B8

VDDM1

存储端口1的IOVDD;

电压1.8~2.5

B9

B10

XM1DATA13

B11

ARM1176核和缓存的内部VDD,该点电压未定

B12

XM1DATA16

在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统控制器设置

B13

XM1DATA17

B14

XM1DQS2

在IO状态下,存储器端口1DRAM数据选通

B15

XM1DATA22

B16

XmmcDATA1_2/GHP4

B17

VDDMMC

USB.OTG.PHY的内部VDD;

电压2.5~3.3

B18

XmmcDATA0_0/GHP2

在IO状态下,数据(SD/SDIO/MMC卡接口通道0)

B19

XspiMISO1/GPC4

在IO状态下,SPI主设备输入线路

B20

XspiMISO0/GPC0

B21

XuTXD3/

GPB3

在O状态下,UART3传输数据输出

B22

XuTXD1/

GPA5

在O状态下,UART1传输数据输出

B23

XciYDATA7/

GPF12

在I状态下,在8位模式下,像素数据为YCbCr;

或在16位模式下为Y;

通过相机处理器A驱动

图像/视频处理

(相机接口具体信)

B24

XciYDATA5/

GPF10

B25

NC_F

C1

XM0ADDR0

在O状态下,存储器端口1DRAM地址总线

S3C6410共享存储器端口(DRAM0)具体信号

C2

ARM1176核和缓存的内部VDD,该点电压未定(TBD)

C3

XpcmSOUT1/GPE4

C4

XpcmFSYNC1/GPE2

在O状态下,PCM同步指示字的开始

C5

XpcmEXTCLK1/GPE0

C6

XM1DATA4

S3C6410共享存储器端口(DRAM1)具体信号

C7

XM1DATA2

C8

XM1DATA5

C9

XM1DATA7

C10

C11

XM1DATA14

C12

XM1DATA10

C13

XM1DATA19

C14

C15

XM1DATA20

C16

XmmcDATA1_6/GHP8

存储设备

C17

XmmcDATA1_1/GHP3

C18

XmmcDATA0_2/GHP4

C19

XspiMOSI1/

GPC6

C20

XspiCS0/GPC3

在IO状态下,SPI片选(只对于从模式)

C21

VDDEXT

PCM的IOVDD音频(I/F-I^2S,AC97);

电压3.3

C22

XuRTSN1/

GPA7

在O状态下,UART1请求发送数据信号

C23

XpwmECLK/GPF13

在I状态下,PWM定时器外部时钟

调制解调器接口

(PWM具体信号)

C24

XciYDATA2/

GPF7

C25

XciYDATA0/

GPF5

D1

XM0ADDR2

在O状态下,存储器端口0DRAM地址总线

S3C6410共享存储器端口(DRAM0)具体信号

D2

XM0ADDR3

D3

D6

XpcmFSYNC0/GPD2

D7

D8

D9

XM1DQS0

D10

XM1DATA15

D11

XM1DATA11

D12

XM1DATA8

D13

VDDI

D14

XM1DQM2

D15

XM1DATA21

D16

XM1DATA23

D17

XspiCS1/

GPC7

D18

D19

XuRXD2/

GPB0

在I状态下,UART2接受数据输入

D20

XuRXD0/

GPA0

在I状态下,UART0接受数据输入

D23

XpwmTOUT1/GPF15

在O状态下,PWM定时器输出

D24

XciVSYNC/GPF4

在I状态下,垂直同步,通过相机处理器A驱动

D25

XciHREF/GPF1

在I状态下,水平同步,通过相机处理器A驱动

E1

XM0ADDR5

E2

E3

E23

XciYDATA1/

GPF6

E24

XM1DATA28

E25

XM1DQS3

F1

XM0ADDR8/GPO8

F2

XM0ADDR6/GPO6

F3

F4

VDDM0

存储端口0的IOVDD;

F22

XciPCLK/GPF2

在I状态下,像素时钟,通过相机处理器A驱动

F23

XM1DATA24

F24

XM1DATA25

F25

XM1DATA26

G1

XM0ADDR10/GPO10

G2

XM0ADDR11/GPO11

G3

G4

XM0ADDR7/GPO7

G8

XM1DQM1

G9

XM1DQS1

G10

G11

XmmcDATA1_5/GHP7

G12

XmmcDATA0_3/GHP5

G13

XmmcCMD0/GPG1

G14

Xi2cSDA

在IO状态下,IIC总线数据

G15

XIRSDBW/GPB4

在O状态下,IrDA收发控制信号

(关机和带宽控制)

(IrDA具体信号)

G16

XuCTSN0/

GPA2

在I状态下,UART0清除发送数据信号

G17

XciYDATA6/

GPF11

G18

XciYDATA3/

GPF8

G22

XciCLK/GPF0

在O状态下,主时钟相机处理器A

G23

XM1DATA29

在IO状态下,可作为存储器端口1DRAM高于半数据总线使用,通过系统p控制器设置

G24

XM1DATA27

G25

XM1DATA30

H1

H2

XM0ADDR13/GPO13

H3

XM0ADDR15/GPO15

H4

XM0ADDR12/GPO12

H7

XM0ADDR4

H8

VSSIP

G;

内部逻辑接地&

ARM1176核和缓存

H9

XmmcDATA1_7/GHP9

H10

XmmcDATA1_3/GHP5

H11

XmmcDATA1_0/GHP2

H12

XspiCLK1/

GPC5

在IO状态下,SPI时钟作为通道1

H13

XmmcDATA0_1/GHP3

H14

XspiCLK0/

GPC1

在IO状态下,SPI时钟作为通道0

H15

XuCTSN1/

GPA6

在I状态下,UART1清除发送数据信号

H16

XpwmTOUT0/GPF14

H17

XciYDATA4/

GPF9

H18

VSSPERI

P;

USB主设备,SDMMC,主设备I/F,LCD,PCM,外部I/F和系统控制器

H19

XciRSTN/GPF3

在O状态下,软件复位到相机处理器A驱动

H22

XM1DQM3

H23

XM1DATA31

H24

XM1ADDR0

H25

XM1ADDR3

J1

XM0AP/GPQ8

存储器端口0DRAM自动预充电

J2

XM0WEN

在O状态下,存储器端口1DRAM写入有效

J3

J4

XM0ADDR14/GPO14

J7

VSSMEM

存储器端口0和1的IO接地

J8

XM0ADDR9/GPO9

J11

CmmcCLK1/GPG0

在O状态下,时钟(SD/SDIO/MMC卡接口通道1)

J12

J13

J14

XuRXD3/

GPB2

在I状态下,UART3接受数据输入

J15

XuRXD1/

GPA4

在I状态下,UART1接受数据输入

J18

J19

J22

XM1ADDR9

J23

XM1ADDR2

J24

XM1ADDR1

J25

XM1ADDR6

K1

XM0DATA15

在IO状态下,存储器端口0DRAM低于半数据总线

K2

K3

K4

XM0DATA14

K7

XM0DQM1

K8

K18

XM1ADDR7

K19

XM1ADDR11

K22

XM1ADDR13

K23

XM1ADDR8

K24

XM1ADDR12

K25

XM1ADDR5

L1

XM0DQM0

在O状态下,存储器端口0DRAM数据屏蔽

L2

XM0DATA13

L3

XM0SMCLK/GPp1

在O状态下,存储器端口DRAM0时钟

L4

XM0OEN

存储器端口0CF输出有效选通

S3C6410共享存储器端口(CF)具体信号

L7

XM0DATA10

在IO状态下,存储器端口0共同数据线

L8

XM0DATA12

L9

L17

L18

XM1CSN1

在O状态下,存储器端口1DRAM片选支持高达2个存储页

L19

XM1ADDR4

L22

XM1RASN

在O状态下,存储器端口1DRAM行地址选通

L23

XM1CSN0

L24

XM1CASN

在O状态下,存储器端口1DRAM列地址选通

L25

XM1ADDR15

M1

M2

XM0DATA8

M3

XM0DATA11

M4

XM0DATA9

M7

XM0DATA2

M8

XM0DATA4

M9

M17

XM1ADDR14

S3C6410共享存储器端口(DRAM1)具体