FPGALED点阵汉字显示设计方案.docx

《FPGALED点阵汉字显示设计方案.docx》由会员分享,可在线阅读,更多相关《FPGALED点阵汉字显示设计方案.docx(27页珍藏版)》请在冰豆网上搜索。

FPGALED点阵汉字显示设计方案

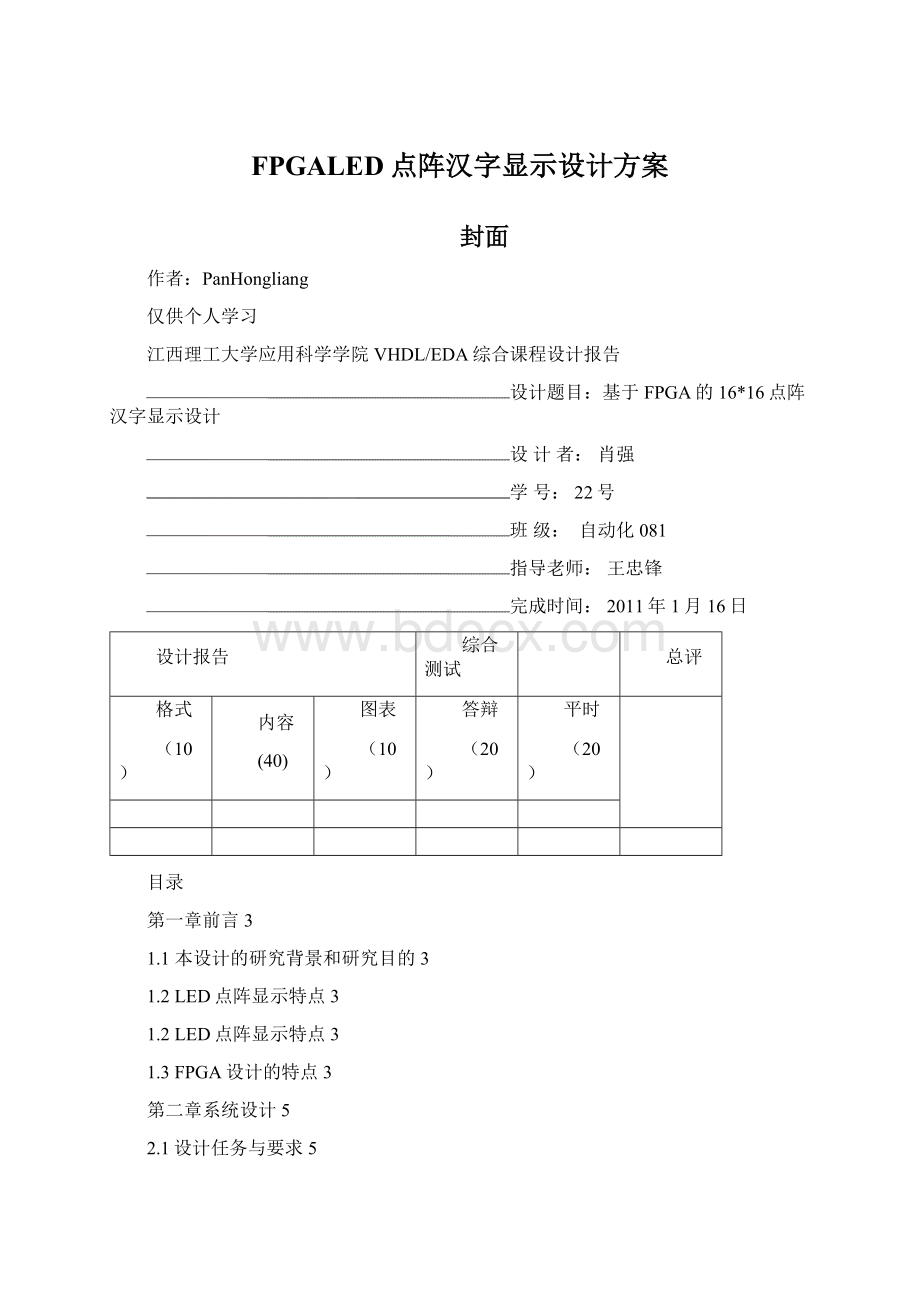

封面

作者:

PanHongliang

仅供个人学习

江西理工大学应用科学学院VHDL/EDA综合课程设计报告

设计题目:

基于FPGA的16*16点阵汉字显示设计

设计者:

肖强

学号:

22号

班级:

自动化081

指导老师:

王忠锋

完成时间:

2011年1月16日

设计报告

综合测试

总评

格式

(10)

内容

(40)

图表

(10)

答辩

(20)

平时

(20)

目录

第一章前言3

1.1本设计的研究背景和研究目的3

1.2LED点阵显示特点3

1.2LED点阵显示特点3

1.3FPGA设计的特点3

第二章系统设计5

2.1设计任务与要求5

2.1.1设计任务5

2.1.2设计要求5

2.2设计原理5

2.2.1总体设计方案5

2.2.2方案的比较5

2.3扫描控制模块5

2.3.1LED的显示原理4

2.3.2汉字的存储5

2.4方案一..6

2.4.116进制计数器设计7

2.4.2列驱动设计8

2.4.3行驱动设计9

2..5汉字的储存…………………………………………………………………………19

2.5.1汉字显示…………………………………………………………………………..20

2.5.2列循环扫描………………………………………………………………………..20

2.5.3字符样式设计……………………………………………………………………..21

第三章系统调试与仿真25

3.1开发环境介绍25

3.2调试与仿真25

3.2.1创建工程…………………………………………………………………………..25

3.2.2编译前设置25

3.2.3全程编译27

3.2.4时序仿真28

第四章结束语29

答谢辞29

参考文献29

第一章前言

1.1本设计的研究背景和研究目的

受到体育场馆用LED显示屏需求快速增长的带动,近年来,中国LED显示屏应用逐步增多。

目前,LED已经广泛应用在银行、火车站、广告、体育场馆之中。

而随着世博会的临近,LED显示屏将广泛的应用在体育场馆以及道路交通指示中,LED显示屏在体育广场中的应用将出现快速增长。

因此研究LED汉字滚动显示屏的设计方法具有重要的理论和现实意义。

随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程FPGA器件进行系统芯片集成的新设计方法,也正在快速地到代基于PCB板的传统设计方式。

因此,本设计的研究是很有必要的,之所以基于FPGA设计是因为现场可编程门阵列(FPGA)设计周期小,灵活度高,适合用于小批量系统,提高系统的可靠性和集成度。

并且采用编写灵活的VHDL语言编写主程序。

1.2LED点阵显示特点

(1)可以显示各种数字、文字、图表、曲线、图形;

(2)采用纯红、高绿作双基色发光器件,发光亮度高,色彩鲜艳、丰富;

(3)显示效果清晰、稳定、功耗低、寿命长;

(4)优质铝合金结构,磨沙、银镜或钛金不锈钢包边。

尺寸和规格可根据需要灵活组合;

(5)支持各种计算机网络,编辑软件丰富、易用;

(6)适用于室内、外所有信息发布及广告宣传场所。

如:

银行、证券交易所、商场、市场、宾馆、洒楼、电信、邮政、医院、车站、机场等。

1.3FPGA设计的特点

FPGA通常被认为是ASIC实现的一种替代手段.一般ASIC包括三种,既全定制、半定制(含标准单元和门阵列)以及可编程器件。

对于前两种,需要支付不可重复使用的工程费用NRE(NonrecurringEngineering),主要用于芯片的流片、中测、分析的工程开销,一次费用一般在1万至数万美元以上。

如果一次不成功、返工、甚至多次返工,NRE费用将要上升。

成本高、风险大,而通常对每个ASIC品种的需求量往往不大,NRE费用分摊到每个产品上价太高,用户无法接受。

而对于可编程器件PLD(ProgrammableLogicDevice)正是可以解决上述问题的新型ASIC,PLD以其操作灵活、使用方便、开发迅速、投资风险小等突出优点,特别适合于产品开发初期、科研样品研制或小批量的产品.FPGA是一种新型的PLD,其除了具有PLD的优点外,其规模比一般的PLD的规模大。

目前,Xilinx推出的XC4025可以达到25000门的规模,Altera公司的FLEX10K100系列芯片可达到十万门的规模,完全可以满足用户的一般设计需要。

FPGA的主要特点是:

寄存器数目多,采用查找表计数,适合时序逻辑设计。

但是互连复杂,由于互连采用开关矩阵,因而使得延时估计往往不十分准确。

FPGA也有其自身的局限性,其一就是器件规模的限制,其二就是单元延迟比较大。

所以,在设计者选定某一FPGA器件后,要求设计者对器件的结构、性能作深入的了解,在体系结构设计时,就必须考虑到器件本身的结构及性能,尽可能使设计的结构满足器件本身的要求.这样就增加了设计的难度。

离开对FPGA结构的详细了解,设计人员就不可能优化设计。

因而设计人员必须了解FPGA器件的特性和限制,熟悉FPGA的结构。

在了解FPGA结构特点的基础上,就可以利用VHDL语言描写出高效的电路描述实现性能优化的电路。

第二章系统设计

2.1设计任务与要求

使用FPGA设计一个16×16的点阵显示的控制器,使点阵显示器以两种花样显示“江西理工大学应用科学学院欢迎您!

”

2.1.2设计要求

(1)输出预定义“江、西、理、工、大、学、应、用、科、学、学、院、欢、迎、您、”十五个汉字;

(2)输出汉字循环显示;

(3)操作方便、可维护性高;

(4)程序简捷,便于修改。

2.2设计原理

2.2.1总体设计方案

方案一:

每次显示一个汉字,一秒钟后刷新显示第二汉字,一秒钟后刷新显示第三汉字,依次刷新显示“江西理工大学……”。

循环显示以上汉字

方案二:

使用滚屏

2.3扫描控制模块

2.3.1LED的显示原理

16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯,所以其扫描译码地址需4位信号线(SEL0-SEL3),其汉字扫描码由16位段地址(0-15)输入。

通过时钟的每列扫描显示完整汉字。

图2-2LED灯红绿信号图2-316×16点阵LED等效电路

点阵LED一般采用扫描式显示,实际运用分为三种方式:

(1)点扫描

(2)行扫描

(3)列扫描

若使用第一种方式,其扫描频率必须大于16×64=1024Hz,周期小于1ms即可。

若使用第二和第三种方式,则频率必须大于16×8=128Hz,周期小于7.8ms即可符合视觉暂留要求。

此外一次驱动一列或一行(8颗LED)时需外加驱动电路提高电流,否则LED亮度会不足。

2.4方案一:

16×16扫描LED点阵只要其对应的X、Y轴顺向偏压,即可使LED发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

应用时限流电阻可以放在X轴或Y轴。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

本实验就是要通过CPLD芯片产生读时序,将字形从寄存器中读出,然后产生写时序,写入16×16的点阵,使其扫描显示输出。

为了显示整个汉字,首先分布好汉字的排列,以列给出汉字信息(从16个Y轴线输入字模信息);然后以128HZ的时序逐个点亮每一行(行扫描),即每行逐一加高电平,根据人眼的视觉残留特性,使之形成整个汉字的显示。

LED点阵每个点都有一个红色的发光二极管。

点阵内的二极管间的连接都是行共阳,列共阴(要点亮的二极管给出低电平字模信息)。

本实验采用共阴,当二极管的共阳极为高电平,共阴极为低电平时,所接点发光;反之处于截止状态,不放光。

本实验采取行扫描方式,用列给文字信息,利用周期为1s的脉冲来控制所显示的字。

本设计由32进制计数器(COUNT32),16进制计数器(COUNT16),行驱动(ROWCON)和列驱动(XIANSHI)组成。

图2-116×16点阵原理图

COUNT32.vhd是32进制的计数器,其每计一次数,输出一个字。

例如当计数为“00000B”时显示“江”,当计数为“00001B”时显示“西”。

给其脉冲周期为1S。

其描述如下:

LIBRARYIEEE。

USEIEEE.STD_LOGIC_1164.ALL。

USEIEEE.STD_LOGIC_UNSIGNED.ALL。

ENTITYCOUNT32IS

PORT(CLK1:

INSTD_LOGIC。

QOUT:

OUTSTD_LOGIC_VECTOR(4DOWNTO0))。

ENDENTITYCOUNT32。

ARCHITECTUREBEHVOFCOUNT32IS

SIGNALCQI:

STD_LOGIC_VECTOR(4DOWNTO0)。

BEGIN

PROCESS(CLK1)

BEGIN

IF(CLK1'EVENTANDCLK1='1')THEN

CQI<=CQI+1。

ENDIF。

QOUT<=CQI。

ENDPROCESS。

ENDARCHITECTUREBEHV。

图3-1CUONT32.VHD仿真波形图

从上图中可以看出,本模块是32进制的计数器,当CLK1给予脉冲时输出为前一个数值加1,例如:

在31.46ms前输出为00110B,在这个时刻CLK1给予触发脉冲,31.46ms后的输出为00111B。

可以看出该模块满足设计要求。

2.4.1.16进制计数器设计

COUNT16.vhd是16进制的计数器,其输出端控制行和列驱动控制器的输出数据;其描述如下:

LIBRARYIEEE。

USEIEEE.STD_LOGIC_1164.ALL。

USEIEEE.STD_LOGIC_UNSIGNED.ALL。

ENTITYCOUNT16IS

PORT(CLK:

INSTD_LOGIC。

QOUT:

OUTSTD_LOGIC_VECTOR(3DOWNTO0))。

ENDENTITYCOUNT16。

ARCHITECTUREBEHVOFCOUNT16IS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0)。

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

CQI<=CQI+1。

ENDIF。

QOUT<=CQI。

ENDPROCESS。

ENDARCHITECTUREBEHV。

图3-2COUNT16.vhd仿真波形图

从上图可以看出,该模块为16进制的计数器,当CLK给予脉冲时输出为前一个数值加1,例如:

在104.86ms前输出为0AH,在这个时刻CLK给予触发脉冲,104.86ms后输出值为0BH。

可以看出该模块满足设计要求

2.4.2:

列驱动设计

ROWCON.vhd为行驱动控制器,该模块控制所亮的行,当输出为0001H时,给点阵的第一行高电平,输出为0010H时,给点阵的第