基于VHDL语言的5B6B编译系统设计Word格式.docx

《基于VHDL语言的5B6B编译系统设计Word格式.docx》由会员分享,可在线阅读,更多相关《基于VHDL语言的5B6B编译系统设计Word格式.docx(18页珍藏版)》请在冰豆网上搜索。

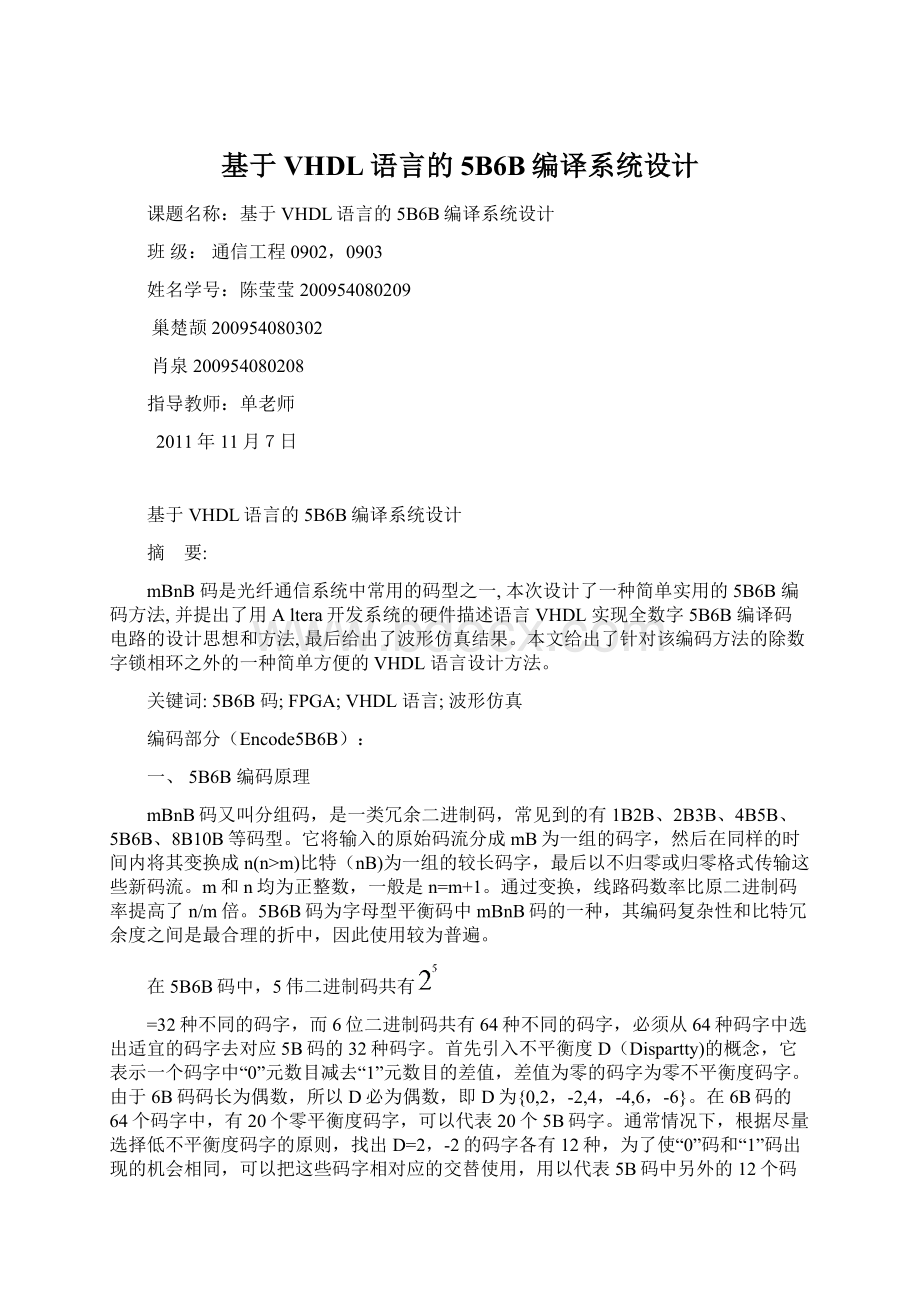

输入码字

(5b)

输出码字(6b)

模式一

模式二

00000

110010

16

10000

110001

1

00001

110011

100001

17

10001

111001

010001

2

00010

110110

100010

18

10010

111010

010010

3

00011

100011

19

10011

010011

4

00100

110101

100100

20

10100

110100

5

00101

100101

21

10101

010101

6

00110

100110

22

10110

010110

7

00111

100111

000111

23

10111

010111

010100

8

01000

101011

101000

24

11000

111000

011000

9

01001

101001

25

11001

011001

10

01010

101010

26

11010

011010

11

01011

001011

27

11011

011011

001010

12

01100

101100

28

11100

011100

13

01101

101101

000101

29

11101

011101

001001

14

01110

101110

000110

30

11110

011110

001100

15

01111

001110

31

11111

001101

二5B6B的编码电路设计

5B6B编码电路的工作原理:

为了实现5B6B编码,本设计是以随机码作为输入的数字信号。

因此,完整的5B6B编码电路包括分频电路、串并转换电路、编码电路和并串转换电路组成。

(1)五分频器:

五分频序列发生器的输入时钟脉冲五分频,从而可以实现每输入5BIT的串行信号就同步转换输出出五位的并行信号,实现时钟信号的同步。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycnt5is

port(clk5:

instd_logic;

newclk1:

outstd_logic);

end;

architectureexamofCNT5is

signalq:

integerrange0to4;

signaltemp:

std_logic;

begin

process(clk5)

begin

ifclk5'

eventandclk5='

1'

then--表示检测clock的上升沿

ifq=4then

q<

=0;

temp<

='

;

elseq<

=q+1;

temp<

0'

endif;

endif;

endprocess;

newclk1<

=temp;

--newclk1是用于五串变五并模块和编码部分的控制时钟

endexam;

五分频分频功能仿真波

(2)串并转换(5位串变5位并)(用循环移位实现)

Clk0来一次有效,Y接收串行的数据就向右移一位,当五分频的信号clk5有效时把Y输出。

编码部分五串变五并程序:

entitySER2PAR5to5is

shift_in:

A:

outstd_logic_vector(4downto0));

end;

architectureoneofSER2PAR5to5is

std_logic_vector(4downto0);

p1:

ifclk5'

then

q<

=shift_in&

q(4downto1);

endif;

endprocessp1;

A<

=q;

endone;

五位串变并波形仿真图:

(3)编码

根据上面的码表,确定5位码对应的6位码,利用类似查表的方法,把输入的五位数据当作rom中的地址,然后输出对应的6位码。

编码部分程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPROM5_6IS

PORT(Y:

INSTD_LOGIC_VECTOR(4DOWNTO0);

CLK6,F:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(5DOWNTO0));

END;

ARCHITECTUREONEOFPROM5_6IS

SIGNALREG:

STD_LOGIC_VECTOR(5DOWNTO0);

BEGIN

P1:

PROCESS(Y,F)

BEGIN

ifF='

then--模式一部分

caseYis

when"

00000"

=>

REG<

="

110010"

00001"

110011"

00010"

110110"

00011"

100011"

00100"

110101"

00101"

100101"

00110"

100110"

00111"

100111"

when"

01000"

101011"

01001"

101001"

01010"

101010"

01011"

001011"

01100"

101100"

01101"

101101"

01110"

101110"

01111"

001110"

10000"

110001"

10001"

111001"

10010"

111010"

10011"

010011"

10100"

110100"

10101"

010101"

10110"

010110"

10111"

010111"

11000"

111000"

11001"

011001"

11010"

011010"

11011"

011011"

11100"

011100"

11101"

011101"

11110"

011110"

11111"

001101"

WHENOTHERS=>

=NULL;

endcase;

endif;

then--模式二部分

100001"

100010"

100100"

000111"

101000"

000101"

000110"

010001"

010010"

010100"

011000"

001010"

001001"

001100"

ENDPROCESSP1;

P2:

PROCESS(CLK6)

BEGIN

IFCLK6'

EVENTANDCLK6='

THEN

Q<

=REG;

ENDIF;

ENDPROCESSP2;

ENDONE;

编码仿真波形如下:

(4)六分频器:

六分频序列发生器的输入时钟脉冲六分频,从而可以实现每输入6BIT的并行信号就将其转换给变量。

具体程序如下:

entityCNT6is

port(clk6:

cnter:

architectureexamofCNT6is

std_logic_vector(2downto0);

process(clk6)

ifclk6'

eventandclk6='

ifq="

101"

000"

cnter<

六分频分频功能仿真波形图:

(5)六位并变串转换

把编码实现的6位码,由并行转换为串行输出。

entityPAR2SER6to6is

port(

clk0,clk6:

instd_logic;

Q:

instd_logic_vector(5downto0);

shift_out:

outstd_logic);

endPAR2SER6to6;

architectureoneofPAR2SER6to6is

signalN:

INTEGERRANGE0TO5;

signalREG:

std_logic_vector(5downto0);

p1:

process(clk6,Q)

begin

ifclk6'

REG<

=Q;

endprocessp1;

PROCESS(CLK0,REG,N)

IFCLK0'

EVENTANDCLK0='

THEN

IFN=5THENN<

ELSEN<

=N+1;

ENDIF;

caseNis

when0=>

shift_out<

=REG(0);

when1=>

=REG

(1);

when2=>

=REG

(2);

when3=>

=REG(3);

when4=>

=REG(4);

when5=>

=REG(5);

whenothers=>

X'

endcase;

endone;

六位并到串仿真波形图:

解码部分(Encode5B6B):

一、解码原理

解码器与编码器基本相同,只是除去组别控制部分。

译码时,把送来的已变换的6B信号码流,每6比特并联为一组,作为PROM的地址,然后读出5B码,再经过并-串变换还原为原来的信号码流。

二5B6B的译码电路设计

解码器包括5分频电路、6分频电路、串并转换电路、解码电路和并串转换电路组成。

(1)译码部分六分频器(用于产生同步时钟信号):

(2)串行转并行(6位串变6位并):

entitySER2PAR6to6is

port(clk6:

shift_in:

A:

outstd_logic_vector(5downto0));

architectureoneofSER2PAR6to6is

std_logic_vector(5downto0);

ifclk6'

q(5downto1);

endprocessp1;

A<

串行转并行功能仿真波形图:

(3)译码

译码程序:

entityPROM6_5is

clk5:

Q:

Y:

outstd_logic_vector(4downto0));

endPROM6_5;

architectureoneofPROM6_5is

signalREG:

begin

process(clk5,Q)

caseQis

when"

when"

When"