VHDL数字时钟设计样本Word文档下载推荐.docx

《VHDL数字时钟设计样本Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《VHDL数字时钟设计样本Word文档下载推荐.docx(10页珍藏版)》请在冰豆网上搜索。

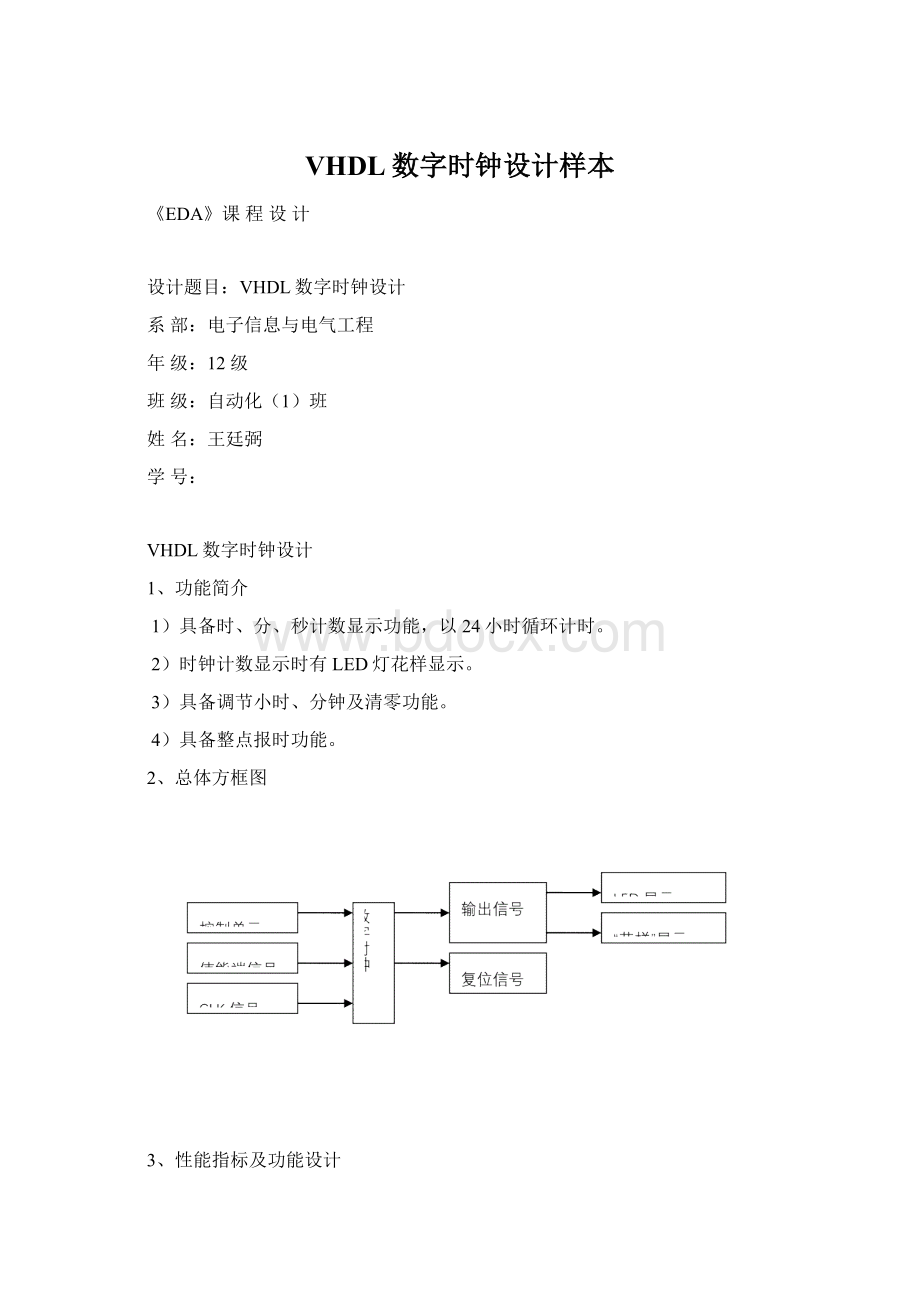

2、总体方框图

3、性能指标及功能设计

1)时钟计数:

完毕时、分、秒对的计时并且显示所计数字;

对秒、分

——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

2)时间设立:

手动调节分钟、小时,可以对所设计时钟任意调时间,这样使数字钟真正具备使用功能。

咱们可以通过实验板上键7和键4进行任意调节,由于咱们用时钟信号均是1HZ,因此每LED灯变化一次就来一种脉冲,即计数一次。

3)清零功能:

reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以依照咱们自己任意时间复位。

4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。

产生“滴答.滴答”报警声音。

5)LED灯在时钟显示时有花样显示信号产生。

即依照进位状况,LED不断闪烁,从而产生“花样”信号。

4、方案选取

依照总体方框图及各某些分派功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分调节以及小时调节和一种顶层文献构成。

采用自顶向下设计办法,子模块运用VHDL语言设计,顶层文献用原理图设计办法。

显示:

小时采用24进制,而分钟和秒均60进制。

5、细化框图

依照自顶向下办法以及各功能模块功能实现上述设计方案应系统细化框图:

6、编写程序、仿真和分析

1、秒计数器

1)VHDL语言描述程序

LIBRARYIEEE;

useIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYhourIS

PORT(clk,reset:

INSTD_LOGIC;

daout:

outSTD_LOGIC_VECTOR(5DOWNTO0));

ENDENTITYhour;

ARCHITECTUREfunOFhourIS

SIGNALcount:

STD_LOGIC_VECTOR(5DOWNTO0);

BEGIN

daout<

=count;

PROCESS(clk,reset)

IF(reset='

0'

)THENcount<

="

000000"

;

——若reset=0,则异步清零

ELSIF(clk'

eventandclk='

1'

)THEN——否则,若clk上升沿到

IF(count(3DOWNTO0)="

1001"

)THEN——若个位计时正好到“1001”即9

IF(count<

16#23#)THEN——23进制

count<

=count+7;

——若到23D则

else

——复0

ENDIF;

ELSIF(count<

16#23#)THEN——若未到23D,则count进1

=count+1;

ELSE——否则清零

;

ENDIF;

——ENDIF(count(3DOWNTO0)=“1001”)

——ENDIF(reset=‘0’)

ENDPROCESS;

ENDfun;

2)秒计数器仿真波形图

3)波形分析

运用60进制计数器完毕00到59循环计数功能,当秒计数至59时,再来一种时钟脉冲则产生进位输出,即enmin=1;

reset作为复位信号低电平有效,即高电平时正常循环计数,低电平清零。

由于这种60进制VHDL语言是较好写,它并不复杂,再说咱们必要要学会这些基本硬件语言描写。

2、分钟计数器

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYminuteIS

PORT(clk,clk1,reset,sethour:

INSTD_LOGIC;

enhour:

OUTSTD_LOGIC;

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDENTITYminute;

ARCHITECTUREfunOFminuteIS

SIGNALcount:

STD_LOGIC_VECTOR(6DOWNTO0);

SIGNALenhour_1,enhour_2:

STD_LOGIC;

——enmin_1为59分时进位信号

BEGIN——enmin_2由clk调制后手动调时脉冲信号串

enhour_2<

=(sethourandclk1);

——sethour为手动调时控制信号,高电平有效

enhour<

=(enhour_1orenhour_2);

PROCESS(clk,reset,sethour)

BEGIN

)THEN——若reset为0,则异步清零

0000000"

IF(count(3DOWNTO0)="

)THEN——若个位计时正好到“1001”即9

IF(count<

16#60#)THEN——又若count不大于16#60#,即60

IF(count="

1011001"

)THEN——又若已到59D

enhour_1<

='

——则置进位为1

——count复0

ELSE

——若count未到59D,则加7,即作“加6校正”

——使前面16#60#个位转变为8421BCD容量

ELSE

——count复0(有此句,则对无效状态电路可自启动)

——ENDIF(count<

16#60#)

ELSIF(count<

16#60#)THEN

=count+1;

——若count<

16#60#则count加1

after100ns;

——没有发生进位

——否则,若count不不大于16#60#count复0

——ENDIF(count(3DOWNTO0)=“1001”)

——ENDIF(reset=‘0’)

ENDprocess;

2)分钟计数器仿真波形图

小时计数模块运用24进制计数器,通过度钟进位信号输入可实现从00到23循环计数。

3、小时计数器

2)小时计数器仿真波形图

4、整点报时报警模块

ENTITYalertIS

PORT(clk:

dain:

INSTD_LOGIC_VECTOR(6DOWNTO0);

speak:

lamp:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));

ENDalert;

ARCHITECTUREfunOFalertIS

SIGNALcount:

STD_LOGIC_VECTOR(1DOWNTO0);

SIGNALcount1:

speaker:

PROCESS(clk)

speak<

=count1

(1);

IF(clk'

)THEN

IF(dain="

IF(count1>

10"

count1<

00"

——count1为三进制加法计数器

=count1+1;

ENDIF;

ENDIF;

ENDPROCESSspeaker;

lamper:

IF(rising_edge(clk))THEN

lamp<

001"

——循环点亮三只灯

ELSIF(count="

01"

010"

100"

ENDPROCESSlamper;

2)整点报时模块仿真波形图

1)波形分析

由图知对于整点报时模块,当分钟计数至59时来一种时钟脉冲则产生一种进位信号,分钟计数到00,此时产生报警信号持续一分钟。

当有时钟脉冲时lamp显示灯就闪烁轮续点亮。

7、全系统联调

1、数字时钟系统原理图

2、数字时钟系统波形图仿真

8、总结

通过这次设计,进一步加深了对EDA理解,让我对它有了更加浓厚兴趣。

特别是当每一种子模块编写调试成功时,心里特别开心。

但是在编写顶层文献程序时,遇到了不少问题,特别是各元件之间连接,以及信号定义,总是有错误,在细心检查下,终于找出了错误和警告,排除困难后,程序编译就通过了,心里终于舒了一口气。

器件选取也很重要,只有选取适当器件,才干对的编译,从而能更好做好本次实验!

通过这次课程设计使我懂得了理论与实际相结合是很重要,只有理论知识是远远不够,只有把所学理论知识与实践相结合起来,从理论中得出结论,才干真正为社会服务,从而提高自己实际动手能力和独立思考能力。

在设计过程中遇到问题,可以说得是困难重重,难免会遇到过各种各样问题,同步在设计过程中发现了自己局限性之处,对此前所学过知识理解得不够深刻,掌握得不够牢固。

最后,对给过我协助所有同窗和各位指引教师再次表达忠心感谢!