计算机组成原理13习题解析第四章01doc.ppt

《计算机组成原理13习题解析第四章01doc.ppt》由会员分享,可在线阅读,更多相关《计算机组成原理13习题解析第四章01doc.ppt(15页珍藏版)》请在冰豆网上搜索。

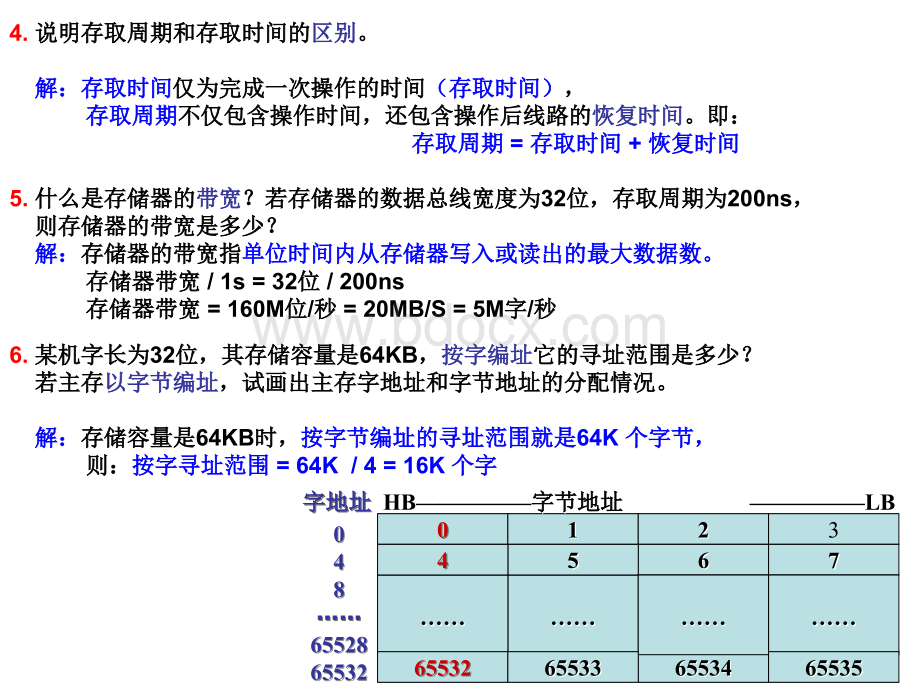

4.说明存取周期和存取时间的说明存取周期和存取时间的区别区别。

解:

存取时间解:

存取时间仅为完成一次操作的时间仅为完成一次操作的时间(存取时间)(存取时间),存取周期存取周期不仅包含操作时间,还包含操作后线路的不仅包含操作时间,还包含操作后线路的恢复时间恢复时间。

即:

。

即:

存取周期存取周期=存取时间存取时间+恢复时间恢复时间5.什么是存储器的什么是存储器的带宽带宽?

若存储器的数据总线宽度为?

若存储器的数据总线宽度为32位,存取周期为位,存取周期为200ns,则存储器的带宽是多少?

则存储器的带宽是多少?

解:

解:

存储器的带宽指存储器的带宽指单位时间内从存储器写入或读出的最大数据数。

单位时间内从存储器写入或读出的最大数据数。

存储器带宽存储器带宽/1s=32位位/200ns存储器带宽存储器带宽=160M位位/秒秒=20MB/S=5M字字/秒秒6.某机字长为某机字长为32位,其存储容量是位,其存储容量是64KB,按字编址按字编址它的寻址范围是多少?

它的寻址范围是多少?

若主存若主存以字节编址以字节编址,试画出主存字地址和字节地址的分配情况。

,试画出主存字地址和字节地址的分配情况。

解:

解:

存储容量是存储容量是64KB时,时,按字节编址的寻址范围就是按字节编址的寻址范围就是64K个字节,个字节,则:

则:

按字寻址范围按字寻址范围=64K/4=16K个字个字0011223665544655346553465532655327765535655356553365533字地址字地址字地址字地址HBHB字节地址字节地址字节地址字节地址LBLB004488655286552865532655327.一个容量为一个容量为16KX32位的存储器,其位的存储器,其地址线和数据线的总和地址线和数据线的总和是多少?

是多少?

当选用下列不同规格的存储芯片时,各需要多少片?

当选用下列不同规格的存储芯片时,各需要多少片?

1KX4位,位,2KX8位,位,4KX4位,位,16KX1位,位,4KX8位,位,8KX8位位解:

解:

地址线和数据线的总和地址线和数据线的总和=14+32=46根;根;各需要的片数为:

各需要的片数为:

1KX4:

16KX32/1KX4=16X8=128片片2KX8:

16KX32/2KX8=8X4=32片片4KX4:

16KX32/4KX4=4X8=32片片16KX1:

16KX32/16KX1=32片片4KX8:

16KX32/4KX8=4X4=16片片8KX8:

16KX32/8KX8=2X4=8片片9.什么叫什么叫刷新刷新?

为什么为什么要刷新?

说明刷新有要刷新?

说明刷新有几种方法几种方法。

解:

刷新解:

刷新对对DRAM定期进行的全部重写过程;定期进行的全部重写过程;刷新原因刷新原因因电容泄漏而引起的因电容泄漏而引起的DRAM所存信息的衰减需要及时补充,所存信息的衰减需要及时补充,因此安排了定期刷新操作;因此安排了定期刷新操作;常用的刷新方法常用的刷新方法有三种有三种集中式、分散式、异步式集中式、分散式、异步式。

集中式:

集中式:

在最大刷新间隔时间内,集中安排一段时间进行刷新;在最大刷新间隔时间内,集中安排一段时间进行刷新;分散式:

分散式:

在每个读在每个读/写周期之后插入一个刷新周期,无写周期之后插入一个刷新周期,无CPU访存死时间;访存死时间;异步式:

异步式:

是集中式和分散式的折衷。

是集中式和分散式的折衷。

10.半导体存储器芯片的半导体存储器芯片的译码驱动方式译码驱动方式有几种?

有几种?

解:

解:

半导体存储器芯片的译码驱动方式有半导体存储器芯片的译码驱动方式有两种两种:

线选法(单译码器)线选法(单译码器)和和重合法(双译码器)重合法(双译码器)。

线选法:

线选法:

地址译码信号只选中同一个字的所有位,结构简单,费器材;地址译码信号只选中同一个字的所有位,结构简单,费器材;重合法:

重合法:

地址分行、列两部分译码,行、列译码线的交叉点即为所选单元。

地址分行、列两部分译码,行、列译码线的交叉点即为所选单元。

这种方法通过行、列译码信号的重合来选址,也称矩阵译码。

这种方法通过行、列译码信号的重合来选址,也称矩阵译码。

可大大节省器材用量,是最常用的译码驱动方式。

可大大节省器材用量,是最常用的译码驱动方式。

12.画出用画出用1024X4位位的存储芯片组成一个容量为的存储芯片组成一个容量为64KX8位位的存储器逻辑框图。

的存储器逻辑框图。

要求将要求将64K分成分成4个页面个页面,每个页面分,每个页面分16组组,指出共需多少片存储芯片。

,指出共需多少片存储芯片。

解:

设采用解:

设采用SRAM芯片,芯片,总片数总片数=64KX8位位/1KX4位位=64X2=128片片题意分析题意分析:

本题设计的存储器结构上分为:

本题设计的存储器结构上分为总体总体、页面、组三级页面、组三级,因此画图时也应分三级画。

首先应确定各级的容量:

因此画图时也应分三级画。

首先应确定各级的容量:

页容量页容量=总容量总容量/页面数页面数=64KX8位位/4=16KX8位位;组容量组容量=页面容量页面容量/组组=16KX8位位/16=1KX8位位;组内片数组内片数=组容量组容量/片容量片容量=1KX8位位/1KX4位位=2片(位扩展)片(位扩展);地址分配:

地址分配:

页面号页面号页面号页面号组号组号组号组号组内地址组内地址组内地址组内地址24102410AA1515AA1414AA1313AA1010AA99AA00页面逻辑框图:

(页面逻辑框图:

(字扩展字扩展)1KX81KX8(组(组(组(组00)1KX81KX8(组(组(组(组11)1KX81KX8(组(组(组(组22)1KX81KX8(组(组(组(组1515)组组组组译译译译码码码码器器器器4:

16-CS0-CS0-CS1-CS1-CS2-CS2-CS15-CS15AA9090-WED-WED7070A10A10A11A11A12A12A13A13-CEi-CEi16KX816KX8存储器逻辑框图:

(存储器逻辑框图:

(字扩展字扩展)16KX816KX8(页面(页面(页面(页面00)16KX816KX8(页面(页面(页面(页面11)16KX816KX8(页面(页面(页面(页面22)16KX816KX8(页面(页面(页面(页面33)A14A14A15A15-CE0-CE0-CE1-CE1-CE2-CE2-CE3-CE3A130-WED70A130-WED70页页页页面面面面译译译译码码码码器器器器2:

42:

413.设有一个设有一个64KX8位位的的RAM芯片,试问该芯片共有多少个芯片,试问该芯片共有多少个基本单元基本单元电路(简称存储电路(简称存储基元)?

欲设计一种具有上述同样多存储基元的芯片,要求对芯片字长的选择应满足基元)?

欲设计一种具有上述同样多存储基元的芯片,要求对芯片字长的选择应满足地址线和数据线的总和为最小地址线和数据线的总和为最小,试确定这种芯片的地址线和数据线,并说明有,试确定这种芯片的地址线和数据线,并说明有几种几种解解答。

答。

解:

解:

存储基元总数存储基元总数=64KX8位位=512K位位=219位位;思路思路:

如要满足地址线和数据线总和最小,应尽量把存储元安排在:

如要满足地址线和数据线总和最小,应尽量把存储元安排在字向字向,因为地址位数和字数成因为地址位数和字数成2的幂的幂的关系,可较好地的关系,可较好地压缩压缩线数。

线数。

设地址线根数为设地址线根数为a,数据线根数为,数据线根数为b,则片容量为:

,则片容量为:

2aXb=219;b=219-a;若若a=19,b=1,总和,总和=19+1=20;a=18,b=2,总和,总和=18+2=20;a=17,b=4,总和,总和=17+4=21;a=16,b=8,总和,总和=16+8=24;由上可看出:

由上可看出:

片字数越少,片字长越长,引脚数越多。

片字数越少,片字长越长,引脚数越多。

片字数、片位数均按片字数、片位数均按2的幂变化的幂变化。

结论:

结论:

如果满足地址线和数据线的总和为最小,这种芯片的引脚分配方案有如果满足地址线和数据线的总和为最小,这种芯片的引脚分配方案有两种两种:

地址线:

地址线=19根根,数据线,数据线=1根根;或地址线或地址线=18根根,数据线,数据线=2根根。

14.某某8位位微型机微型机地址码为地址码为18位位,若使用,若使用4KX4位位的的RAM芯片组成模块板结构的存芯片组成模块板结构的存储器,试问:

储器,试问:

(1)该机所允许的)该机所允许的最大主存空间最大主存空间是多少?

是多少?

(2)若每个模块板为)若每个模块板为32KX8位位,共需,共需几个几个模块板?

模块板?

(3)每个模块板内共有)每个模块板内共有几片几片RAM芯片?

芯片?

(4)共有)共有多少片多少片RAM?

(5)CPU如何如何选择选择各模块板?

各模块板?

解:

解:

(1)218=256K,则该机所允许的最大主存空间是,则该机所允许的最大主存空间是256KX8位位(或(或256KB););

(2)模块板总数)模块板总数=256KX8/32KX8=8块块;(3)板内片数)板内片数=32KX8位位/4KX4位位=8X2=16片片(8组组);(4)总片数)总片数=16片片X8=128片片;(5)CPU通过通过最高最高3位地址译码位地址译码选选板板,次高次高3位地址译码位地址译码选选组组。

地址格式分配如下:

地址格式分配如下:

板地址板地址板地址板地址组地址组地址组地址组地址片内地址片内地址片内地址片内地址331233121715141211015.设设CPU共有共有16根地址线根地址线,8根数据线根数据线,并用并用-MREQ(低电平有效)作访存控制信号,(低电平有效)作访存控制信号,R/-W作读写命令信号(高电平为读,低电评为写)。

现有下列存储芯片:

作读写命令信号(高电平为读,低电评为写)。

现有下列存储芯片:

ROM(2KX8位,位,4KX4位,位,8KX8位),位),RAM(1KX4位,位,2KX8位,位,4KX8位),位),及及74138译码器和其他译码器和其他门电路门电路(门电路自定)。

(门电路自定)。

试从上述规格中选用合适芯片,画出试从上述规格中选用合适芯片,画出CPU和存储芯片的连接图。

要求:

和存储芯片的连接图。

要求:

(1)最小最小4K地址地址为为系统系统程序区,程序区,409616383地址范围为地址范围为用户用户程序区;程序区;

(2)指出)指出选用选用的存储芯片类型及数量;的存储芯片类型及数量;(3)详细)详细画出画出片选逻辑。

片选逻辑。

解解:

因为,地址范围决定了存储器的容量。

所以:

因为,地址范围决定了存储器的容量。

所以:

ROM04K(04095)=4K*8RAM409616383=12K*8选选ROM4K*4两片两片(片选信号最少,电路信号传输效率高片选信号最少,电路信号传输效率高)选选RAM4K*8三片三片(片选信号最少片选信号最少)ABC000001010011100101110111Y0Y1Y2Y3Y4Y5Y6Y70111111110111111110111111110111111110111111110111111110111111110G1CBAG2BG2AY0Y1Y2Y3Y4Y5Y6Y7输入信号输入信号输出信号输出信号控制信号控制信号G1G2AG2B741383-8译码器译码器高电平有效高电平有效低电平有效低电平有效低电平有效低电平有效连连片片选选信信号号连连地地址址信信号号A0A114K*4/CSD7D4CPUA11A0D7D0/WE3