计算机组成原理习题解析Word下载.docx

《计算机组成原理习题解析Word下载.docx》由会员分享,可在线阅读,更多相关《计算机组成原理习题解析Word下载.docx(14页珍藏版)》请在冰豆网上搜索。

(2)1024×

1位RAM构成128KB的存储系统;

(3)2K×

4位RAM构成64KB的存储系统;

(4)64K×

1位RAM构成256KB的存储系统;

1)需要16KB/512×

4=64片

片外地址译码需11位地址线。

2)需要128KB/1K×

1=1024片

片外地址译码需10位地址线。

3)需要64KB/2K×

片外地址译码需9位地址线。

4)需要256KB/64K×

1位=32片

片外地址译码需4位地址线。

4.5现有一种存储芯片容量为512×

4位,若要用它组成4KB的存储容量,需多少这样的存储芯片?

每块芯片需多少寻址线?

而4KB存储系统最少需多少寻址线?

解:

4KB/512×

4b=16,需要16片

每片芯片需9条寻址线

4KB存储系统最少需12条寻址线

4.6.何为位扩展?

何为字扩展?

并举例说明。

若每个存储芯片只有1条数据线D,8个存储芯片的数据线分别同CPU的数据线D0~D7相连,CPU发出16位地址,同时选中8个存储片的同一地址单元,各提供1位数据,形成1个字节的信息供CPU读写(这就是“位扩展”);

同样,若每个存储芯片只有2条数据线D1,D0,4个存储芯片的数据线分别同CPU的数据线D0D1,D2D3,D4D5,和D6D7相连,CPU发出16位地址,同时选中4个存储片的同一地址单元,各提供2位数据,形成1个字节的信息供CPU读写;

若每个存储芯片各有4条数据线D3,D2,D1,D0,2个存储芯片的数据线分别同CPU的数据线D3D2D1D0,和D6D7D4D5,相连,CPU发出16位地址,同时选中1个存储片的同一地址单元,各提供4位数据,形成1个字节的信息供CPU读写。

这都是“位扩展”。

每个存储芯片提供字信息,设字信息为8位,每个芯片可提供64K×

8位——64K字,8个存储芯片构成8×

64K字,把存储字从64K字扩展为512K字。

这就是“字扩展”。

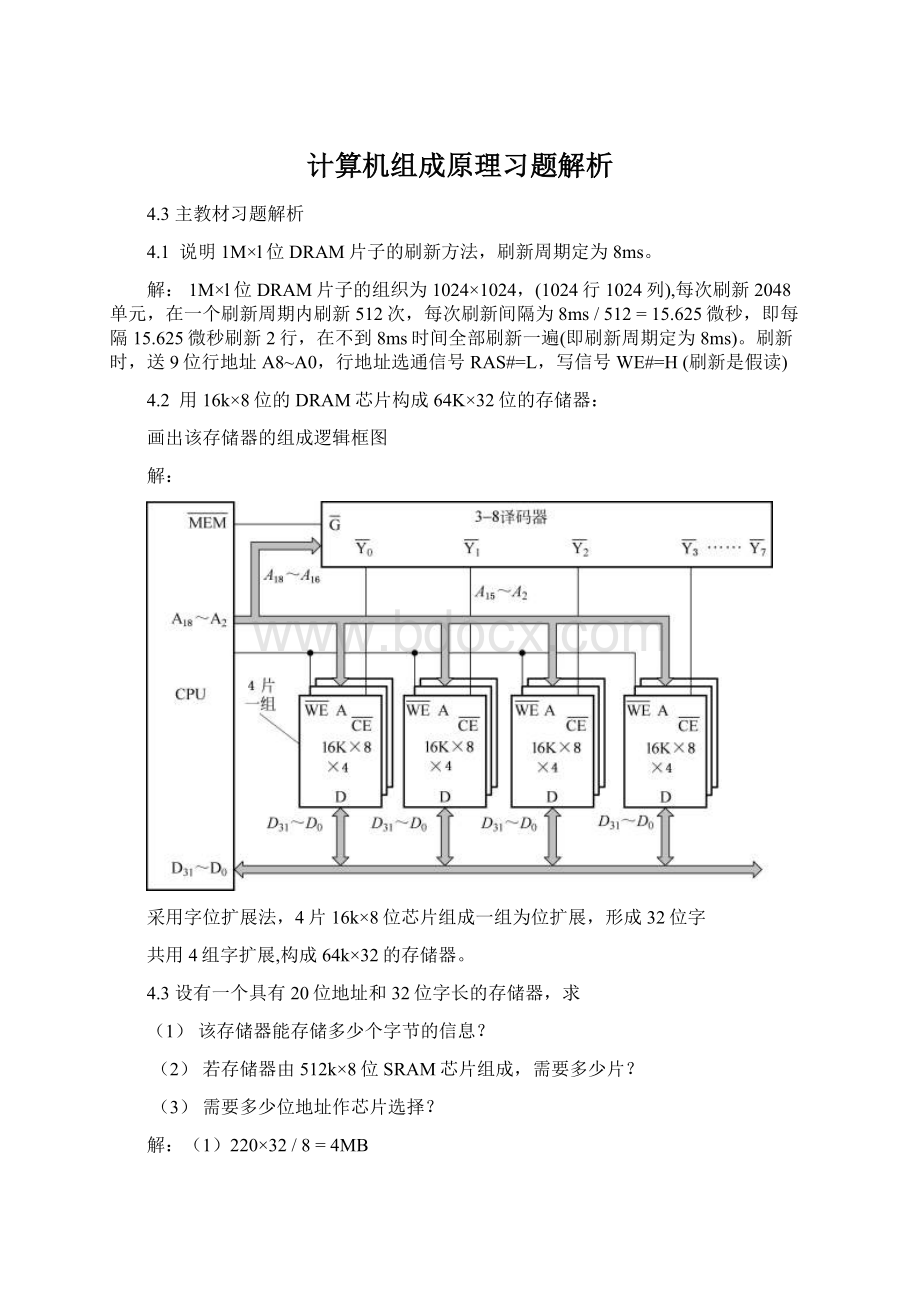

4.7用16k×

8位的SRAM芯片构成64K×

16位的存储器,要求画出该存储器的组成逻辑框图。

采用字位扩展法,2片16k×

8位芯片组成一组为位扩展,形成16位字

16位的存储器。

4.8已知某8位机的主存采用半导体存储器,地址码为18位,采用4K×

4位的SRAM芯片组成该机所允许的最大主存空间,并选用模块条形式,问:

(1)若每个模块条为32K×

8位,共需几个模块条?

(2)每个模块条内有多少片RAM芯片?

(3)主存共需多少RAM芯片?

CPU需使用几根地址线来选择各模块?

使用何种译码器?

(1)地址码为18位,所允许的最大主存空间为218B=512KB

512KB/32K×

8位=16,

共需16个模块条

(2)32K×

8位/4K×

4位=16,

每个模块条内有16片RAM芯片

(3)16×

16=256

主存共需256个RAM芯片

16=2n,n=4

CPU需使用4地址线来选择各模块,使用2-4译码器。

4.9用32K×

8位的静态存储芯片实现128K×

16位的存储体,按字编址(16位为一个字)。

①该存储体需要多少块32K×

8位存储芯片;

②该存储体的地址总线和数据总线各是多少位。

(1)128K×

16/32K×

8位=4×

2

(2)该存储体的地址总线为17位;

该存储体的数据总线为16位

4.10试述三级存储系统的组成(按CPU向外的次序写)及功能。

三级存储系统的组成是Cache(高速缓冲存储器)、主存储器和辅助存储器构成三级存储系统,分为两个存储层次:

Cache-主存存储层次(Cache存储系统)和主存-辅存存储层次(虚拟存储系统)。

Cache-主存存储层次用来解决主存速度低的问题,弥补CPU与主存在速度上的差异。

主存-辅存存储层次用来解决主存容量小的问题,在主存和辅存之间增加辅助硬件和辅助软件,使主存和辅存构成一个整体,扩大程序可访问的存储空间,通过把磁盘空间当作主存空间供程序使用,建立起一个虚拟存储器。

4.11一个具有8KB直接映象Cache的32位计算机系统,主存容量为32MB,假定该Cache中块的大小为4个32位字。

(1)求该主存地址中区号、块号和块内地址的位数。

(2)求主存地址为ABCDEF16的单元在Cache中的位置

(1)区号=32MB/8KB=4K,12位

块号=8KB/4×

4B=512,9位

块内地址=4×

32/8=16,4位(字节地址)

(2)主存地址为ABCDEF16的单元其二进制地址为:

0101010111100110111101111(注意主存字节地址为25位)

区号为010101011110

块号为011011110

数据在Cache中的位置是0110111101111即DEF16

4.12直接映象Cache的块长为4个32位字,容量为4096字,主存容量为64K字:

(1)画出该Cache的地址映象方式

(2)求主存中有多少块,Cache中有多少块

(1)Cache的地址映象方式

这里的块号同Cache块号。

(2)主存中块数为64K字/4字=16K个

Cache中块数为4096字/4字=1024个

4.13一个计算机系统的主存容量为2MB,字长32位,采用直接映象的Cache的容量为512字,计算主存地址格式中,区号、块号和块内地址字段的位数。

(1)Cache块长为1字

(2)Cache块长为8字

(1)Cache块长为1字

主存为2MB,21位,字长32位,字内字节地址2位,主存字地址19位

区号=2MB/512×

4B=1024,10位

块号=512字/1字=512,9位

块内地址,字地址0位(1个字),字内字节地址2位(4B)

(2)Cache块长为8字

主存为2MB,21位,字长32位,字内字节地址2位,主存字地址19位

块号=512字/8字=64,6位

块内地址,字地址3位(8个字),字内字节地址2位(4B)

4.14一个具有16KB直接映象Cache的32位微处理器,主存容量为256MB,假定该Cache中块的大小为4个32位字。

(1)画出该Cache的地址映象方式,并指出主存地址不同字段的作用;

(2)主存地址为ABCDE8F16的单元在cache中的位置(写出区号、块号和块内地址值)

(1)主存256MB,地址为28位

区号=256MB/16K=16K个,14位

块号=16KB/4×

4B=1024,10位

块内地址,字地址2位,字节地址4位

“区号”作为标记(表示为Tag)存放在“地址映像表”中,用于判断是否命中;

“块号”是区内块号,同Cache块号,用于直接查“地址映像表”(用作查表索引,表示为Index),以及在Cache中进行“块寻址”;

“块内地址”用于在块内选择字或字节(表示为BS)

(2)主存地址为ABCDE8F16的单元其二进制地址为:

101010111100111111(主存字节地址为28位)

区号为10101011110011

块号为0111101000

数据在Cache中的位置是01111010001111

即1E8F16

4.15有一个Cache-主存存储层次,主存容量为8个块,Cache容量为4个块。

采用直接地址映象:

(1)对于如下主存块地址流:

0,1,2,5,4,6,4,7,1,2,4,1,3,7,2,如果主存中内容一开始未装入Cache中,请列出每次访问后Cache中各块的分配情况

(2)指出块命中的时刻

(3)求出此期间Cache的命中率

(1)

时间

1

3

4

5

6

7

8

9

10

11

12

13

14

15

地址流

0块

1块

2块

3块

(1)从表可见命中时刻为:

7,11,12和15

(2)h=4/15=0.267

4.16一个组相联映象Cache由64个存储块构成,每组包含4个存储块。

主存包含4096个存储块,每块由128字组成,访存地址为字地址。

(1)求一个主存地址有多少位?

一个Cache地址有多少位?

(2)计算主存地址格式中,区号、组号、块号和块内地址字段的位数。

(1)主存4096块------12位,每块128字------7位,共19位

Cache64块------6位,每块128字------7位,共13位

(2)区号=主存块数/Cache块数=4096/64=64(6位)

组号=Cache块数/组内块数=64/4=16(4位)

组内块号为4(2位)

块内地址为7位(字地址,每块128字)

主存地址格式如下

6位6位2位7位

区号

组号

组内块号

块内地址

4.17有一个16KB4路组相联Cache的32位微处理器,假定该Cache的块为4个32位的字。

(1)画出该Cache的结构逻辑图,指出主存地址的不同字段的作用。

(2)主存地址为ABCDE8F816的单元在Cache中的什么位置。

(1)Cache容量为16kb,地址14位;

采用4路组相联结构,块地址2位;

块长为4个字,块内地址2位;

每个字32位(4个字节),字内字节地址2位。

由

(2)知主存地址为32位,则区号为32-14=18位。

则逻辑结构图如下:

(2)主存地址单元ABCDE8F8的二进制表示为:

101010111100110111101000111101000

Cache地址为:

101000111101000

4.18有一个”Cache-主存”存储层次。

主存共分为8个块(0~7),Cache为4个块(0~3),采用组相联映象,组内块数为2块,采用LRU(近期最少使用法)的替换算法。

(1)画出主存、Cache地址的各字段对应关系;

(2)画出主存、Cache空间块的映象对应关系的示意图;

(3)对于如下主存块地址流:

1、2、4、1、3、7、0、1、2、5、4、6、4、7、2,请列出每次访问后Cache中各块的分配情况。

(1)主存、Cache地址的各字段对应关系如下:

(2)主存的第0和第1块映射到Cache的第0和第1块;

主存的第2和第3块映射到Cache的第2和第3块;

主存的第4和第5块映射到Cache的第0和第1块;

主存的第6和第7块映射到Cache的第2和第3块;

如下图所示:

(3)Cache中各块的使用状况如下图所示:

块失效又发生块争用的时刻为:

6.7.9.10.11.12.14.15。

Cache命中3次,在此期间Cache的命中率为:

H=3/15=0.2。

4.19设Cache的工作速度为主存的8倍,Cache被访问命中的概率为0.90,问采用Cache后,存储器性能提高多少?

Ta=0.1Tm+0.9×

Tm/8=0.2125

性能为原来的1/0.2125=4.706倍,即提高了3.706倍

4.20某计算机的页式虚存管理中采用长度为32字的页面。

页表内容如表习5-1所示,求当CPU程序按下列2进制虚拟字地址访存时产生的实际字地址。

(1)00001101

(2)10000000

(3)00101000

表习5-1

虚页号

实页号

装入位

000

01

001

010

011

00

100

101

110

111

页面长度为32字,则页内地址5位,8位地址码巾的髙3位为虚页号,从表中查出2位实页号,与页内地址合并构成7位实际物理内存的地址。

(1)虚页号为000,查得实页号01,与页内地址01101合并,得0101101;

(2)虚页号为100,查得实页号10,与页内地址00000合并,得1000000;

(3)虚页号为001,查得该页未装入内存,故无相应的内存地址。

4.21一个虚拟存储器有8个页面,页面大小为1024字,内存有4个页面框架,页表的内容如表习5-2所示。

问对应于虚拟地址4096的主存地址是什么。

表习5-2

方法1:

利用除法和取模法

页面大小为1024,虚拟地址为4096,4096/1024=4-------0,

虚页号为4页内地址为0,查表得实页号为2,

实际地址为2×

1024+0=2048

方法2:

页面大小为1024,用二进制表示地址中页内地址部分为10位,髙位部分为虚页号,4096=10000000000002

虚页号为4=100,页内地址为0000000000,查得实页号为2,即102,与页内号合并得实际地址为1000000000002

4.22一个虚拟存储器有8个页面,页面大小为1024字,内存有4个页面框架,页表的内容如表习5-2所示(同上题)。

(1)问哪些虚拟地址将引起页面失效?

(2)对应于以下虚拟地址的主存地址是什么?

0

3728

1023

1024

7800

4096

(1)虚页号为2、3、5、7的页面失效。

(2)0------0110000000000

3728------虚页号为3,页面失效。

1023------0111111111111

1024------0010000000000

7800------虚页号为7,页面失效

-010*********

4.23主存容量为4MB,虚存容量为1GB,则虚拟地址和物理地址各为多少位?

如页面大小为4KB,页表长度是多少?

1GB=230虚拟地址=30位

4MB=222物理地址=22位

主存4MB,页面大小为4KB,主存中有4MB/4KB=1024页

虚存容量为1GB,可有256*1024页

页表长度=218=256K

4.24一台计算机的主存容量为1MB,字长为32位,Cache的容量为512字,确定下列情况下主存和Cache的地址格式:

(1)直接映像的Cache,块长1字

(2)直接映像的Cache,块长8字

(3)组相联映像的Cache,块长1字,组内4块

(1)Cache块长为1字

主存为1MB,20位,字长32位,字内字节地址2位,主存字地址18位

区号=1MB/512×

4B=512,9位

主存的地址格式

块号

块内字节地址

9位9位2位

Cache的地址格式

9位2位

主存为1MB,20位,字长32位,字内字节地址2位,主存字地址18位

区号=1MB/512×

9位6位5位

6位5位

组内4块,块号2位,块长1字,块内地址,字地址0位(1个字),字内字节地址2位(4B),

Cache的容量为512字,块长1字,Cache中有512块,每组4块,Cache中有128组.

区号9位,组号7位,组内块号2位,块内地址---字地址0位(1个字),字内字节地址2位(4B)

主存的地址格式

9位7位2位2位

7位2位2位

4.25一个直接映像的Cache,块长为4个16位的字,容量为4096字,主存容量为64K字

(1)设计该Cache的地址映像方式

(2)主存有多少个块?

Cache有多少个块?

(1)Cache地址:

Cache地址容量为4096字,16位字长,字节地址13位,Cache块长为4个16位的字,1024块,块号10位,块内字节地址3位(块内字地址2位(4个字),字内字节地址1位)

主存容量为64K字,字长16位,主存字节地址17位(字地址16位,字内字节地址1位),

区号=64K字/4096字=16,4位

4位10位3位

Cache的地址格式

10位3位

(2)主存有16个块,Cache有10个块。