Concept HDL原理图设计Word文档格式.docx

《Concept HDL原理图设计Word文档格式.docx》由会员分享,可在线阅读,更多相关《Concept HDL原理图设计Word文档格式.docx(38页珍藏版)》请在冰豆网上搜索。

总体方案的设计、元件的选型、库的设计及将其添加到项目中。

设计阶段

在准备工作都完成之后,就进入设计阶段开始设计工作。

这阶段主要包括:

新建一个项目、ConceptHDL的初始化的设置和原理图的绘制。

设计后输出阶段

完成了设计之后,要对原理图进行仔细的检查、打包原理图、导出物料表以及完成原理图的打印、输出工作,开始PCB设计工作。

方案设计

元件选型

原理图库设计

初始化设置

创建一个项目

库的设置添加

原理图设计

原理图检查

原理图输出

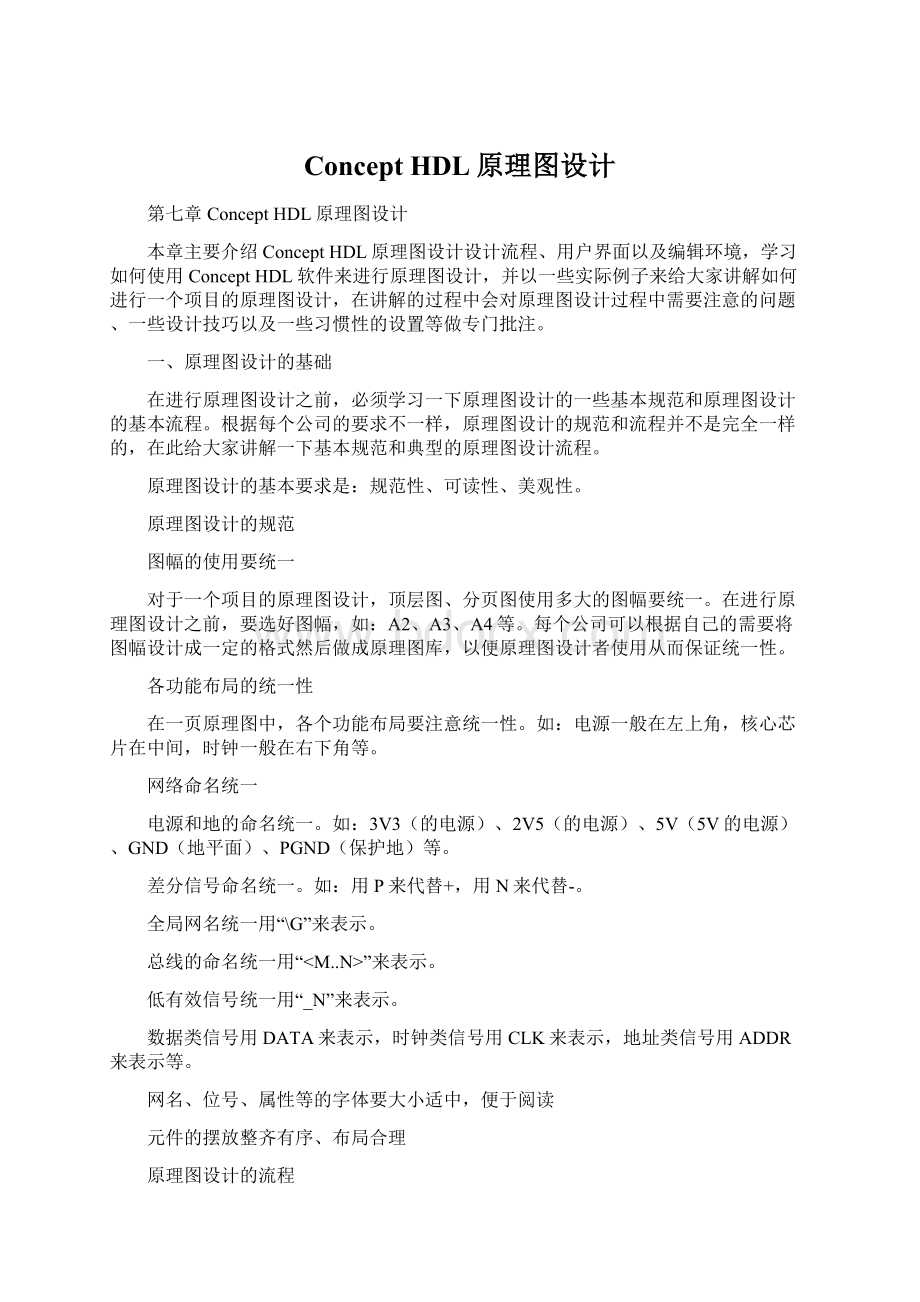

7_1

图7_1是一个项目原理图设计的基本流程。

二、ConceptHDL的用户界面

ConceptHDL是Cadence公司的原理图输入工具,提供原理图输入与分析的一个真正的协同设计的环境。

其用户界面由标题栏、菜单栏、工具栏、设计窗口、状态栏以及命令控制窗口组成,如图7_2所示。

对于ConceptHDL界面的6个部分,标题栏显示当前所得页面及页面状态,设计窗口就是整个设计所在的窗口,也就是图7_2中所示中间区域,命令栏是供用户写入命令的窗口(可以通过点击View/ConsoleWindow来控制是否打开),状态栏是显示当前状态的一栏,包括样式、选中、使用库、栅格和鼠标位置坐标等。

下面分解详细讲解一下菜单栏和工具栏。

菜单栏

ConceptHDL的菜单栏是由13个下拉菜单组成,他们分别是:

File(文件类)、Edit(编辑类)、View(查看类)、Component(元件类)、Wire(线类)、Text(字符类)、Block(模块类)、Group(群组类)、Display(显示类)、AMSSimulator(仿真类)、Tools(工具类)、Window(窗口类)、Help(帮助)。

File(文件类)

文件类的下拉菜单中的命令主要包括:

新建、打开、关闭及保存一个文件及转换(Revert)、回复(Recover)、移动(Remove)、编辑页面,编辑层次图、更改序列号、输入\输出原理图信息、原理图打印相关的设置、推出等。

Edit(编辑类)

编辑类的下拉菜单主要是对元件和线进行编辑的一些命令,如:

后退\前进命令(Undo\Redo)、移动、复制、排列、删除、镜像、旋转、层次图显示、创建圆\圆弧等。

7_2

View(查看类)

查看类的下拉菜单的命令主要是控制整个界面的,如:

缩放界面、界面的上下左右移动、以及界面中的控制栏、错误表示栏、命令栏是否打开灯。

Component(元件类)

元件类的下拉菜单都是对元件进行操作的一些命令,如:

添加元件、替换元件、替换元件的part(Version)、元件封装信息更改(Modify)、显示元件的引脚(Section)、交换\转换引脚(SwapPins\BubblePins)、删除元件所有属性(Smash)等。

Wire(线类)

线类的下拉菜单中主要包括:

连线命令(Draw和Route)、添加网名(SignalName)、总线网名(BusName)、总线符号设置(BusTap)、加连接点(Dot/ConnectionPoint)、线加粗\细(Thick\Thin)、线样式选择(Pattern)等。

Text(字符类)

字符类的下拉菜单主要包括:

添加一个带属性字符(Property)、增加一个自定义的字符(CustomText)、查看字符属性(Attributes)、分配电源\信号引脚模型(AssignPower\Signal)、更新当前页面的字符(UpdateSheetVariables)、更改字符(Change)、增加接口名字(PortName)、设置字符大小(SetSize)、交换字符(Swap)、更改字符属性(Reattach)、属性显示格式选择(PropertyDisplay)等。

Block(模块类)

模块类的下拉菜单的命令主要是针对模块的操作,在没有选中模块的时候,大多数命令都是不可选中的。

此下拉菜单命令包括:

增加一个模块(Add)、模块名的更改(Rename)、模块大小的更改(Stretch)、模块上划线(DrawWire和RouteWire,模块上会自动增加引脚)、模块引脚的添加(AddPin会有3种接口供选择:

输入、输出、双向)及引脚的删除、更名、移动等命令。

Group(群组类)

群组类的下拉菜单中的命令主要包括:

创建一个组,设置当前组的组名、查看组的内容以及对当前组的移动、删除、复制、设置字符大小、选择颜色表示、高亮显示及元件更新等命令。

Display(显示类)

显示类俄下拉菜单中的命令都是与项目中元件、网名等显示有关的,包括:

高亮显示(Highlight)、去除高亮显示(Dehighlight)、属性的显示(Attachments)、颜色标示(Color)、显示元件信息(Component)、星号显示一个网名连接多处引脚(Connections)、显示任一点的坐标(Coordinate)、显示当前项目目录(Directory)、显示任意两点的距离(Distance)、显示历史操作(History)、显示定义的热键(Keys)、显示未保存定义(Modified)、显示网名(Net)、星号显示每个元件的原点(Origins)、星号显示每个引脚的位置(Pins)、显示选中元件的引脚名(PinNames)、显示所有属性(Properties)、显示返回的信息(Return)、显示选中字符的大小(TextSize)等。

AMSSimulator(仿真类)

仿真类的命令栏,其下拉菜单中的命令主要包括和仿真相关的命令,如:

新建、编辑、删除一个仿真项、运行仿真、创建网表、查看网表、编辑模型、高级分析、反标仿真结果、编辑仿真结果等。

Tools(工具类)

工具类的下拉菜单中包括命令:

扩展设计(EspandDesign)、取消扩展(UnexpandDesign)、编辑模式(OccurrenceEdit)、全局查找(GlobalFind)、全局导航(GlobalNavigate)、全局更新(GlobalUpdate)、打开约束管理器(Constraints)、检查原理图(Check)、查看错误(Error)、标识信息(Markers)、运行脚本文件(RunScript)、反标识原理图(BackAnnotate)、仿真(Simulate)、层次编辑(HierarchyEditor)、生成模块(GenerateView)、元件管理(PartManager)、模型分配(ModelAssignment)、打包后运行项(PackagerUtilities)、自动对比项(DesignSifferences)、设计统一(DesignAssociation)、工具选项(Options)、工具栏定制(Customize)等。

Window(窗口类)

窗口类的下拉菜单中主要都是与窗口相关的一些命令,如:

新窗口、刷行窗口、层叠防止窗口、上下防止窗口、重排图标及当前显示项的选择。

Help(帮助类)

帮助类的下拉菜单命令都是与帮助相关的一些命令,如:

在线帮助、新版本更新项、此工具的学习机学习文档。

工具栏

对于在该课程中使用的ConceptHDL版本,其常用的工具栏如:

标准工具栏(Standard)、模块工具栏(Block)、添加工具栏(Add)、编辑工具栏(Edit)、颜色工具栏(Color)、标记工具栏(Markers)、群组工具栏(Group)及仿真类的模拟工具栏(Analog)、无源工具栏(Passive)、有源工具栏(Source)、线性工具栏(Linear)、分立工具栏(Discrete)、混合工具栏(Misc)及快捷工具栏共14个工具栏组成。

ConceptHDL的14个工具栏可以通过单击菜单栏中的View/Toolbars自己选择打开哪些工具栏,如图7_3所示。

7_3

1)标准工具栏(见图7_4)

7_4

2)模块工具栏(见图7_5)

7_5

3)添加工具栏(见图7_6)

7_6

4)编辑工具栏(见图7_7)

7_7

5)颜色工具栏(见图7_8)

7_8

6)符号工具栏(见图7_9)

7_9

7)群组工具栏(见图7_10)

7_10

8)模拟工具栏(见图7_11)

7_11

9)无源工具栏(见图7_12)

7_12

10)有源工具栏(见图7_13)

7_13

11)线性工具栏(见图7_14)

7_14

12)分立工具栏(见图7_15)

7_15

13)混合工具栏(见图7_16)

7_16

14)快速工具栏(见图7_17)

7_17

三、ConceptHDL的使用

本节主要讲解ConceptHDL的使用,包括ConceptHDL的启动、ConceptHDL的设置以及ConceptHDL的基本操作等。

ConceptHDL的启动

打开或新建一个原理图设计项目有两种方式:

1、通过项目管理器界面进入,此内容在前面章节已介绍过,此处不再赘述;

2、通过点击“开始菜单/程序/AllegroSPB15.5.1/DesignEntryHDL”,出现如图7_18所示提示选择相应的License的界面。

7_18

根据Cadence公司许可选择相应的产品许可之后,就可以进入原理图设计界面中,进行原理图设计。

如果以第二种方式进入到ConceptHDL界面,会弹出一个如图7_19所示的界面,提示是打开最后一次打开的原理图设计项目,还是打开一个已有的项目,又或者是新创建一个原理图设计项目。

7_19

进行选择之后,进入到ConceptHDL工作界面中,用户就可以开始设计自己的原理图了。

ConceptHDL的设置

在进入原理图设计界面开始一个新的设计前,首先要做的就是对ConceptHDL的基本设置,比如:

栅格的设置、字符的设置、节点的设置、输入\输出项的设置等,合理的设置可以提高设计的效率和质量。

ConceptHDL的设置项都在工具类的下拉菜单中的Option下,单击“Tools/Options”,即可以打开设置对话框,如图7_20所示。

7_20

General选项卡中各功能描述

SaveLayoutatExit:

当退出时,保持DesignEntryHDL原有的窗口和工具栏设置

ClicktoActivateView:

选择此项,单击激活窗口;

不选中时,当光标移动到窗口时,自动激活

CursorShapes:

在命令模式下,允许使用不同的光标形状

WindowsAutopan:

整体移动窗口功能

Ctrl+RMBContextMenu:

选择此项:

Ctrl按键+单击鼠标右键才能弹出右键菜单;

不选择此项:

单击鼠标右键直接弹出右键菜单,一般情况下不选中此项

Multi-formatVectors:

多种格式的信号命名方式:

<

>

、()、[]、冒号、逗号与&

都是特殊符号,不能再用作信号名;

上述符号除<

可以指示矢量信号和冒号(:

)代表连接关系,其余符号都无特殊含义,可以用作信号名,一般默认选择此项

Ctrl+LMBSelectandDrag:

改变选择,拖动及Stroke的命令所执行的行为:

1选中时:

直接按住鼠标左键画出相应的符号,即可以使用Stroke功能;

按住Ctrl键,鼠标左键单击一个对象,移动鼠标就可以移动对象;

按下Ctrl或Shift键,按住并拖动鼠标左键,可以选择多个选项。

按下鼠标右键,在弹出菜单中选择Exclude及可以去掉选中的元件、属性或连线;

2、不选择此项时:

按下Ctrl键和1中不按Ctrl键的功能一样,不按下Ctrl和1中按下Ctrl键的功能一样

ComponentBrowser(Add):

选择此项,在命令栏中输入add,即可以打开添加元件对话框

ShowCategoryView(Add):

选择此项,打开添加元件对话框,默认显示的是CategoryView项;

不选择此项,打开添加元件对话框,默认显示的是LibraryView项

DrawingBrowser(Edit):

选择此项,在命令栏中输入edit,回车即可打开ViewOpen窗口

LibrariesBrowser(Lib):

选择此项,在命令栏中输入lib,回车即可以打开SearchStack窗口;

不选择此项,则打开库路径的提示框

ShowPPTBrowser:

选择此项,在添加元件的时候会自动打开PhysicalPartFilter项

EnablePre-SelectMode:

打开DesignEntryHDL菜单的预选模式

SetPATHPropertyInvisible:

选择此项,在放置元件的时候,元件的属性全为不可见,不选择此项,则默认全部显示元件属性

HierarchyViewer:

HideSheetNumber:

表示隐藏层次试图窗口中的模块的页码;

HideInstanceName:

表示隐藏层次试图窗口中的实例名

Messages:

设置在何处显示哪种类型(Fatal、Error、Warning、Information)的信息,例如,当设置了一个很小的逻辑网格尺寸,DesignEntryHDL会给出警告信息“网格太小,无法显示”,此消息如何显示就根据此处的设置;

CommandLine表示在命令输入栏中显示信息;

Dialog表示以对话框的形式显示信息;

Suppress表示不显示信息(对于致命的错误,这项是不能选择的)

CanonicalNames:

在使用全局查找、全局导航和查看属性的时候,控制显示的名命名方式,根据选择和不选择Library、Cell和View来实现显示与不显示这三项内容;

Depth便是在显示格式中的:

View的显示层级

PageBorder:

给新建的原理图页设定一个默认的图幅:

单击“Browse”按钮在相应的库中选择一个图幅即可,设定之后,新建原理图页就是有图幅的页面,不用再手动调入图幅了

Drawings:

设定DesignEntryHDL可以同时打开的原理图页面窗口,默认值是50

Output项

图7_21所示为Output项的各选项内容。

7_21

BinaryFile:

保存逻辑的二进制格式的文件

ASCIIFile:

保存逻辑的ASCII格式的文件

ConfirmWrite:

保存前需确认

DependencyFile:

按照相关信息保存ASCII文件

CreateNetlist:

当保存设计时创建一个VHDL或Verilog文本描述

Verilog:

当保存设计时创建一个Verilog文本描述

Verilog栏的Options:

显示Verilog的网表设置对话框

VHDL:

当保存设计时创建一个VHDL文本描述

VHDL栏的Options:

显示VHDL的网表设置对话框

AnnotateSynthesisConstraintsinNetlist:

选择此项,DesignEntryHDL会报告设计中的约束信息

AllowedGlobalShorts:

添加全局网名列表,这些信号网名可以在设计中短路,当在Signal1栏中填写了第一个全局网名,在Signal2中填写了第二个全局网名,再当它们短路时,不会报错(此项设置一般情况下可以不进行设置,如要设置须慎重)

Paths项

如图7_22所示为Paths项的各项内容

7_22

CategoryFilePath:

指定类别文件(.cat)的目录

InputScript:

指定DesignEntryHDL控制命令的文件路径,在启动DesignEntryHDL的时候运行此文件

PPTOptionSet:

指定PPT选项设置文件的路径,可以作为默认设置

AttributeDirectory:

指定属性显示对话框中显示选项加载的属性文件(.att)默认路径为(安装路径)/tools/fet/concept/attributes

CustomVariables项

如图7_23所示为CustomVariables项的各选项内容

7_23

CustomVariables项是用户定义变量的窗口,可以在DesignEntryHDL定义变量,放置在原理图中。

Name表示在此处输入定义的变量名。

Value表示在此处输入定义变量的值。

注意:

变量值不能为空,否则会删除掉此变量。

Graphics项

如图7_24所示为Graphics项的各选项内容。

7_24

Add:

划线时,以垂直直线方式(Orthogonal)或直线拉斜线方式(Direct)

Move:

移动时,以垂直直线方式(Orthogonal)或直线拉斜线方式(Direct)

AutoRouteOnMove:

移动元件的时候,线随元件移动自动延伸

AutoHeavyIfBusName:

添加总线信号名时,线自动加粗

AutoNameonTap:

在命令总线高低位时,自动插入确定的总线位的总线位符号、数据及网络名

TapSymbol:

指定在原理图中使用的总线位符号

Open:

添加空心的连接点

Filled:

添加实心的连接

AutoDotAtIntersection:

网络连接时,自动显示节点

LogicDotRadius:

调整原理图中的网络连接节点的直径

SymbolDotRadius:

调整Symbol(符号)中的网络连接节点的直径

Text项

如图7_25所示为Text各选项的内容

7_25

Size:

指定文本(属性名、属性值、信号名以及注释)在原理图中的大小,默认为0.082in,最小为0.008in,最大为1.467in;

如果在设计的过程中更改了文本的大小,则只对以后添加的文本有效,对先前添加的无效

Justification:

调整文本的位置居左、居中或居右

Upper-caseInput:

显示所有的文本

TextChangeEditor:

指定默认的文本编辑器

Visibility:

控制属性的显示,都不显示(Invisible)、只显示名字(Name)、只显示值(Value)、显示名字和值(Both)

PinPropertyVisibility:

控制当放置Symbol或元件的时候,引脚属性是否显示,Invisilible表示不显示,DedinedbyComponent表示显示

PinNumberSize:

调整引脚号的大小,默认为0.066in(注意:

引脚号的大小与文本的大小无关)

RorateVerticalPinNumbersDuringBackannotation:

选中此项:

自动选装垂直引脚的引脚号,如果已经反标则不处理

AutoPathPropertiesOnComponents:

对添加的部分自动添加Path属性

RetainDeleteSymbolPropertiesFromLogicInstances(“stickyoff”):

当元件属性被删去时,自动删掉原理图中相应的默认属性

PowerPropertyVisilibity:

控制电源引脚属性的可见性显示,可以选择Invisible、Name、Value及Both,默认为Value

Plotting项

如图7_26所示为Plotting项的各选项内容。

7_26

Plotting选项主要是对打印的一些设置,因为原理图的打印及归档工作是一项非常重要的工作,但不属于设计前的设置项,将会在以后章节中介绍。

Color项

Color项是对DesignEntryHDL中颜色进行设置的项,包括:

图形颜色(线、连接点、符号、圆弧、属性、注释、高亮)和背景的颜色选取,如图7_27所示。

7_27

Grid项

如图7_28所示为Grid项的各选项内容。

7_28

Type:

定义网格类型:

Decimal表示选择10进制绘制(每in对应500单位);

Fractional表示每in对应400单位绘制;

Metric表示选择公制绘制(每mm20单位)

LogicGrid:

定义原理图绘制的栅格

SymbolGrid:

定义Symbol绘制的栅格

DocumentGrid:

定义文本绘制的栅格

Show:

显示隐藏的网格

Style:

以点(Dots)或线(Lines)方式显示栅格

调整栅格的大小

Multiple:

显示每个栅格线,定义可以放置对象的地方,可以保证线和元件引脚的正确连接(注意:

整个设计阶段包括原理图库设计、原理图绘制栅格应该尽可能的一致)

SignalIntegrity项

如图7_29所示为SignalIntegrity项的各选项内容。

SignalIntegrity项是信号完整性的设置项,主要是对不同的引脚类型来赋予一定的模型。

这些引脚类型包括:

IN、OUT、BI、TRI、OCL、OCA。

当然也可以通过选择RetainExistingXnetsandDiffpairs项来改变差分以及Xnets的设置。

7_29

Check项

如图7_30所示为Check项的各选项内容。

7_30

CheckonWrite:

存盘时自动检查,错误信息保存在和

ElectricalChecks:

电气检查的项

MissingPins:

检查引脚属性是否不再附加在引脚

UnconnectedWirs:

检查是否没有网名的线及有网名但是没有任何连接的线

ShortedPins:

检查一个引脚连接两个以上网名的情况

Power-LoadSignalShort:

Checksforlocalsig