出租车自动计价器设计Word格式.docx

《出租车自动计价器设计Word格式.docx》由会员分享,可在线阅读,更多相关《出租车自动计价器设计Word格式.docx(10页珍藏版)》请在冰豆网上搜索。

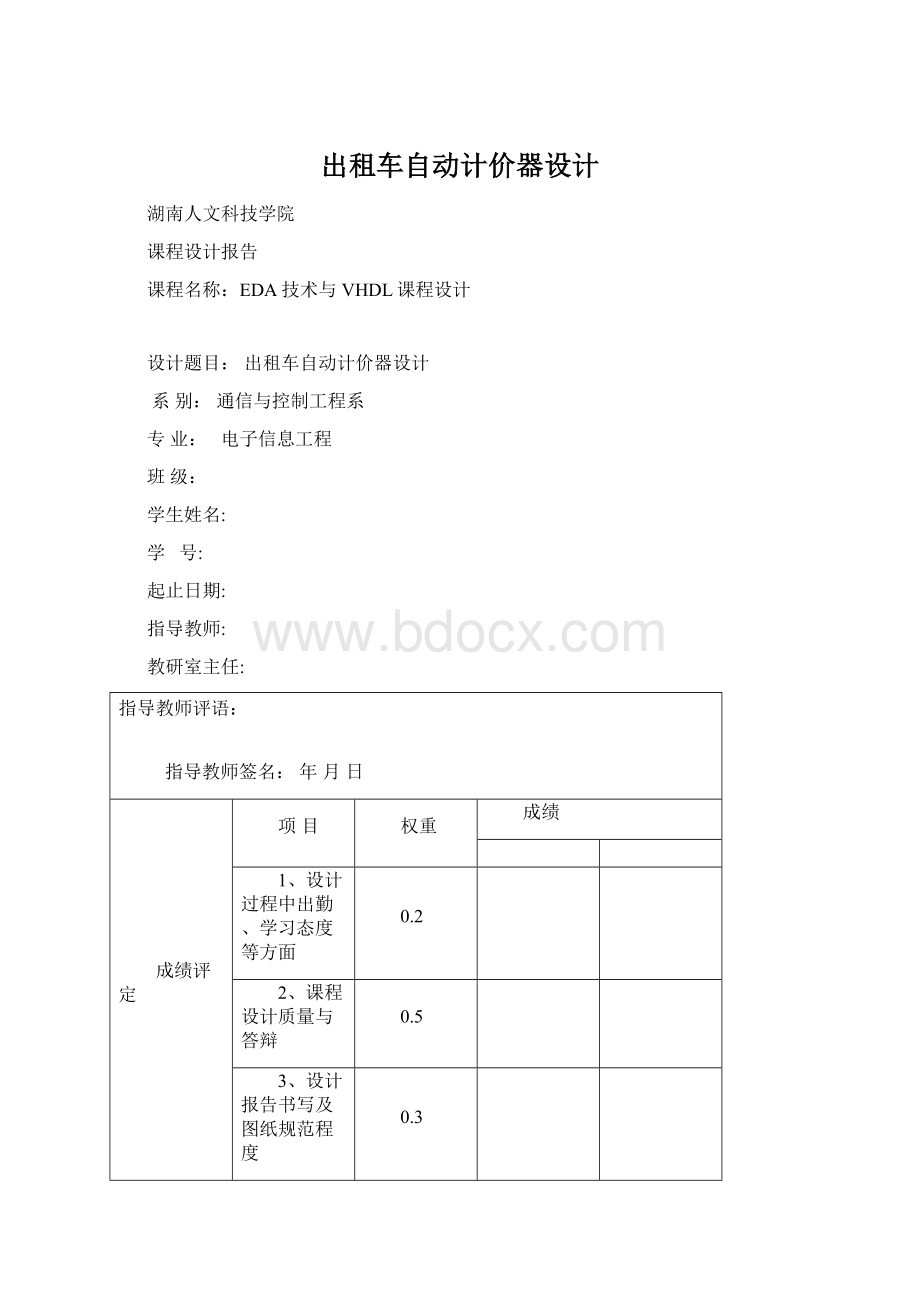

教学系审核意见:

主任签字:

年月日

摘要

随着我国社会经济的全面发展,各大中小城市的出租车营运事业发展迅速,出租车已经成为人们日常出行选择较为普遍的交通工具。

出租车计价器是出租车营运收费的专用智能化仪表,是出租车市场规范化、标准化以及减少司机与乘客之间发生纠纷的重要设备。

一种功能完备、简单易用、计量准确的出租车计价器是加强出租车行业管理、提高服务质量的必备品。

根据预定的设计要求和设计思路,我们使用VHDL硬件描述语言设计了一个实际的基于AlteraFPGA芯片的出租车自动计价器系统,介绍了该系统的电路结构和程序设计。

通过在QuartusII6.0软件中编译和下载测试,得到了仿真波形和关键的设计结果。

经过在实验箱上进行硬件测试,证明该出租车计价系统具有实用出租车计价器的基本功能,如能进一步完善,将可以实用化和市场化。

关键词:

出租车自动计价器;

VHDL;

FPGA;

QuartusII6.0

设计要求

设计一个出租车计价器,该计价器的计费系统:

行程3公里内,且等待累计时间2分钟内,起步费为10元;

3公里外以每公里1.6元计费,等待累计时间2分钟以每分钟1.5元计费。

并能显示行驶公里数、等待累计时间、总费用。

设计的主要技术指标如下:

1)计价范围:

0~999.9元计价分辨率:

0.1元

2)计程范围:

0~99公里计程分辨率:

1公里

3)计时范围:

0~59分计时分辨率:

1分

1、方案论证与对比

根据本课程设计要求,需要对出租车当行驶公里数和等待时间两种情况对应进行计数计费,同时要求显示出对应行驶公里数、等待时间和出租车费用,我们想到了以下两种方案。

1.1方案一

用分频器将外部时钟分为三路频率的信号,用来计时和计程,同时也供整个系统工作,通过设置使能信号,使系统自动对等待时间计时和对行驶公里数的计数,最后将所得结果分别在数码管上显示出来。

图1方案一出租车计价系统的设计结构图

1.2方案二

各部分主要功能包括:

信号输入模块对车轮传感器传送的脉冲信号进行计数,并以高低脉冲模拟出租汽车启动、停止按钮,具有输入信号作用;

数据转换模块将计费模块输出的车费和路程转换成十进制数据;

译码/动态扫描模块将路程与费用的数值译码后用动态扫描的方式驱动数码管[5];

数码管显示模块将公里数和计费金额显示出来。

图2方案二出租车计价系统的设计结构图

1.3两种方案的对比

经分析,两种方案都要通过模块组合来实现出租车计价器的功能。

方案一模块数量比方案二多一些,但思路简单,各模块程序也相对简单,因此较容易实现,适合我们初学EDA的编程设计。

方案二模块较少,但单个模块功能要求较高,程序复杂。

所以,我们选择方案一。

2、实验步骤和设计过程

2.1分频器模块

分频器模块:

分频模块对频率为256Hz的输入脉冲进行分频,得到两个16Hz频率的信号和1个1Hz的频率。

该模块产生的频率信号用于计费,每个1Hz脉冲为0.1元计费控制,16Hz信号一个为1.6元的公里脉冲计费控制,另一个16Hz信号为1.6元等待时间计费控制。

2.2计程模块

计程模块:

根据提供的里程脉冲信号fin,计算乘客上车后出租车所行驶的里程数。

fin每来一个上升沿,计程模块实现一次计数,里程数就加1。

当行驶里程大于3Km时,本模块中en0信号变为1;

进行行驶公里都计费。

2.3等待计时模块

等待计时模块:

根据分频得到的时钟信号f_1,计算乘客的等待累计时间。

计时器的量程为59min,满量程归零。

等待时间大于3min时,本模块中en1信号变为1;

f_1每来一个上升沿,计量模块实现一次计数,等待时间加1。

2.4计费模块

计费模块:

实现计价、计时和计程的数据计费。

计量模块实现对于出租车在行驶和等待过程中的里程数和计时功能:

计费时钟每来一个上升沿,计量模块实现一次计数,里程数或者等待时间加1。

进行的是行驶公里数大于3公里以每公里1.6元计费的操作;

当等待时间大于2min时,本模块中en1信号变为1,进行的是等待时间大于2分钟以每分钟1.6元计费的操作;

最后用cha3,cha2,cha1,cha0来组成的4位数显示总费用,最大显示为999.9元。

3、调试与操作说明

3.1QuartusII中的VHDL程序

根据设计要求我们写出了VHDL程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitytaxiis

--定义实体[3]

port(clk_256

:

instd_logic;

--频率为256Hz的时钟

start:

--计价使能信号

stop:

--等待信号

fin:

--公里脉冲信号

cha3,cha2,cha1,cha0:

outstd_logic_vector(3downto0);

--费用数据

km1,km0:

--公里数据

min1,min0:

outstd_logic_vector(3downto0));

--等待时间

endtaxi;

architecturebehavoftaxiis

signalf_16,f16,f_1:

std_logic;

signalq_16:

integerrange0to15;

--分频器

signalq16:

--分频器

signalq_1:

integerrange0to255;

signalw:

integerrange0to59;

--秒计数器

signalc3,c2,c1,c0:

std_logic_vector(3downto0);

--制费用计数器

signalk1,k0:

--公里计数器

signalm1:

std_logic_vector(2downto0);

--分的十位计数器

signalm0:

--分的个位计数器

signalen1,en0,f:

--使能信号

begin

fenpin:

process(clk_256,start)--分频器模块

ifclk_256'

eventandclk_256='

1'

then

ifstart='

0'

thenq_16<

=0;

q16<

f_16<

='

;

f16<

f_1<

f<

else

ifq_16=15thenq_16<

--此if语句得到频率为16Hz的信号

elseq_16<

=q_16+1;

endif;

ifq16=15thenq16<

--此if语句得到另一个频率为16Hz的信号

elseq16<

=q16+1;

ifq_1=255thenq_1<

--此if语句得到频率为1Hz的信号

elseq_1<

=q_1+1;

ifen1='

thenf<

=f_16;

--此if语句得到计费脉冲f

elsifen0='

=f16;

elsef<

endprocess;

process(f_1)--等待计时模块

iff_1'

eventandf_1='

then

w<

en1<

en0<

m1<

="

000"

m0<

0000"

k1<

k0<

elsifstop='

then--等待计时模块

ifw=59thenw<

--此if语句完成等待计时

ifm0="

1001"

thenm0<

--此if语句完成分计数

ifm1<

101"

thenm1<

elsem1<

=m1+1;

elsem0<

=m0+1;

ifm1&

m0>

"

0000001"

thenen1<

--此if语句得到en1使能信号

elseen1<

elsew<

=w+1;

elsiffin='

then--计程模块

ifk0="

thenk0<

--此if语句完成公里脉冲计数

ifk1="

thenk1<

elsek1<

=k1+1;

elsek0<

=k0+1;

ifk1&

k0>

00000010"

thenen0<

--此if语句得到en0使能信号

elseen0<

cha3<

=c3;

cha2<

=c2;

cha1<

=c1;

cha0<

=c0;

--费用数据输出

km1<

=k1;

km0<

=k0;

min1<

&

m1;

min0<

=m0;

--公里数据、分钟数据输出

process(f,start)--计费模块[2]

thenc3<

c2<

0001"

c1<

c0<

elsiff'

eventandf='

ifc0="

thenc0<

--此if语句完成对费用的计数

ifc1="

thenc1<

ifc2="

thenc2<

ifc3<

elsec3<

=c3+1;

elsec2<

=c2+1;

elsec1<

=c1+1;

elsec0<

=c0+1;

endbehav;

3.2程序的编译与及仿真波形

在QuartusII新建项目,将设计的程序输入并以实体名为文件名保存[4],然后以保存后的文件taxi.vhd为顶层文件建立工程,编译通过后新建波形文件,设置好输入参数后进行仿真,我们得到的仿真波形如图4:

图4出租车计价器程序的仿真波形

从仿真波形中我们看出,当出租车行驶公里数(Km1,Km0组成的两位数)为12即出租车行驶了12公里,等待时间(min1,min0组成的两位数)为03,即等待3分钟时,对应的出租车计费显示是0260即26.0元。

而理论计算如下:

出租车总计费=起步费+(行驶公里数-3)×

1.6+(等待时间-2)×

1.6=10+(12-3)×

1.6+(3-2)×

1.6=26.0,可以看出仿真的结果与理论值一致。

3.3程序下载与功能测试

编译通过后,进行引脚锁定,锁定方法如图5:

图5引脚锁定图

锁定好引脚后,将编译产生的SOF格式配置文件配置进FPGA[1],具体操作如下:

先将实验箱下载线连接好,接好电源打开实验箱电源开关,再选择实验箱工作模式0,将实验箱下载允许开关打开,最后在QuartusII菜单依次点击Tools——programer,配置好硬件后点击startprogramer。

这时就可以进行功能测试了。

根据引脚锁定可知实验箱上键6为等待计时控制键,键7为计费/复位控制键,键8为公里脉冲输入控制键。

下载后,按下键7,就开始模拟出租车自动计费过程。

数码管计费显示为“0100”,即10元起步费,其他数码管显示数据都为零。

然后模拟出租车处于等待时的计费情况,按下键6进入等待计时,发现显示计时的数码管每等待1分钟就累加“01”,当等待计时对应数码管显示大于02时我们发现显示计费的数码管显示数据每分钟增加“0016”,符合设计要求。

最后模拟出租车行驶公里的计费,按下键8,发现显示公里数的数码管数值按规律增加,每增加1公里的同时,显示计费的数码管也对应增加“0016”,符合实验要求。

因此,经过硬件电路个参数测试可知,本次设计的出租车自动计价器完全符合设计要求,达到了预期的目的。

4.课程设计心得体会

通过课程设计,我们深有体会:

一、我们温故而知新。

课程设计发端之始,思绪全无,举步维艰,对于理论知识学习不够扎实的我们深感“书到用时方恨少”有时间就会拿教材与实验手册,对知识系统而全面进行了梳理,遇到难处先是苦思冥想再向同学请教,终于熟练掌握了基本理论知识,而且领悟诸多平时学习难以理解掌握的较难知识,学会了如何思考的思维方式,找到了设计的灵感。

二、我们意识到实践出真知,从开始设计到课程设计基本告成,才切身领悟“实践是检验真理的唯一标准”,才明晓实践出真知。

因为在教材上,计数器什么应用的少,而且例子浅显,与实际仿真和测试要求有所不同。

三、我们要创新求发展.我们要从小处着手,顺应时代发展潮流,在课程设计中不忘在小处创新,未必是创新技术,但凡创新思维亦可,未必成功,只要实现创新思维培育和锻炼即可。

四、我们觉得过而能改,善莫大焉。

至善至美,是人类永恒的追求。

但是,我们不曾忘却“金无足赤,人无完人”,换种思维方式,去恶亦是至善,改错亦为至美。

在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获取。

最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。

五、我们领悟到学海无涯,学无止境。

尽管课程设计是在期末才开始,我们的教材学习完毕,掌握许多知识,但是还有很多地方理解领悟不到位,由于对EDA技术与VHDL以及以前学过的模拟电子技术、数字电子技术的相关章节未能掌握以致用到清零复位模块程序无法自行设计,导致程序及实际功能不够完美我们觉得学海无涯只有苦来作舟,学无止境只有书来作伴。

综上所述,课程设计诚然是一门专业课,给我们很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我们许多道,给了我们很多思,给了我们莫大的空间。

5.元器件及仪器设备明细

表1元器件及仪器设备详单

器件名称

型号/版本

数量

备注

微型计算机

联想

一台

EDA/SOPC开发系统

GW48-PK2

一套

QuartusII开发软件

6.0

6.参考文献

[1]潘松,黄继业,EDA技术与VHDL(第2版).北京:

清华大学出版社,2007

[2]高书莉,罗朝霞.可编程逻辑设计技术及应用.北京:

人民邮电出版社,2004

[3]李宗伯,王蓉晖译.VHDL设计表示和综合.北京:

机械工业出版社,2002

[4]边计年,薛宏熙译.用VHDL设计电子线路.北京:

清华大学出版社,2000

[5]王锁萍,电子设计自动化(EDA)教程.成都:

电子科技大学出版社,2000

7.致谢

在这次课程设计的撰写过程中,我们得到了许多人的帮助。

首先我们要感谢我们的指导老师在课程设计上给予我们的指导、提供给我们的支持和帮助,这是我们能顺利完成这次报告的主要原因,更重要的是老师帮我们解决了许多技术上的难题,让我们能把系统做得更加完善。

在此期间,我们不仅学到了许多新的知识,而且也开阔了视野,提高了自己的设计能力。

其次,我们要感谢帮助过我们的同学们,他们也为我们解决了不少我们不太明白的难题。

同时也感谢学院为我们提供良好的做毕业设计的环境。

最后再一次感谢所有在设计中曾经帮助过我们的良师益友和同学。