传导骚扰整改经验案例Word文档格式.docx

《传导骚扰整改经验案例Word文档格式.docx》由会员分享,可在线阅读,更多相关《传导骚扰整改经验案例Word文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

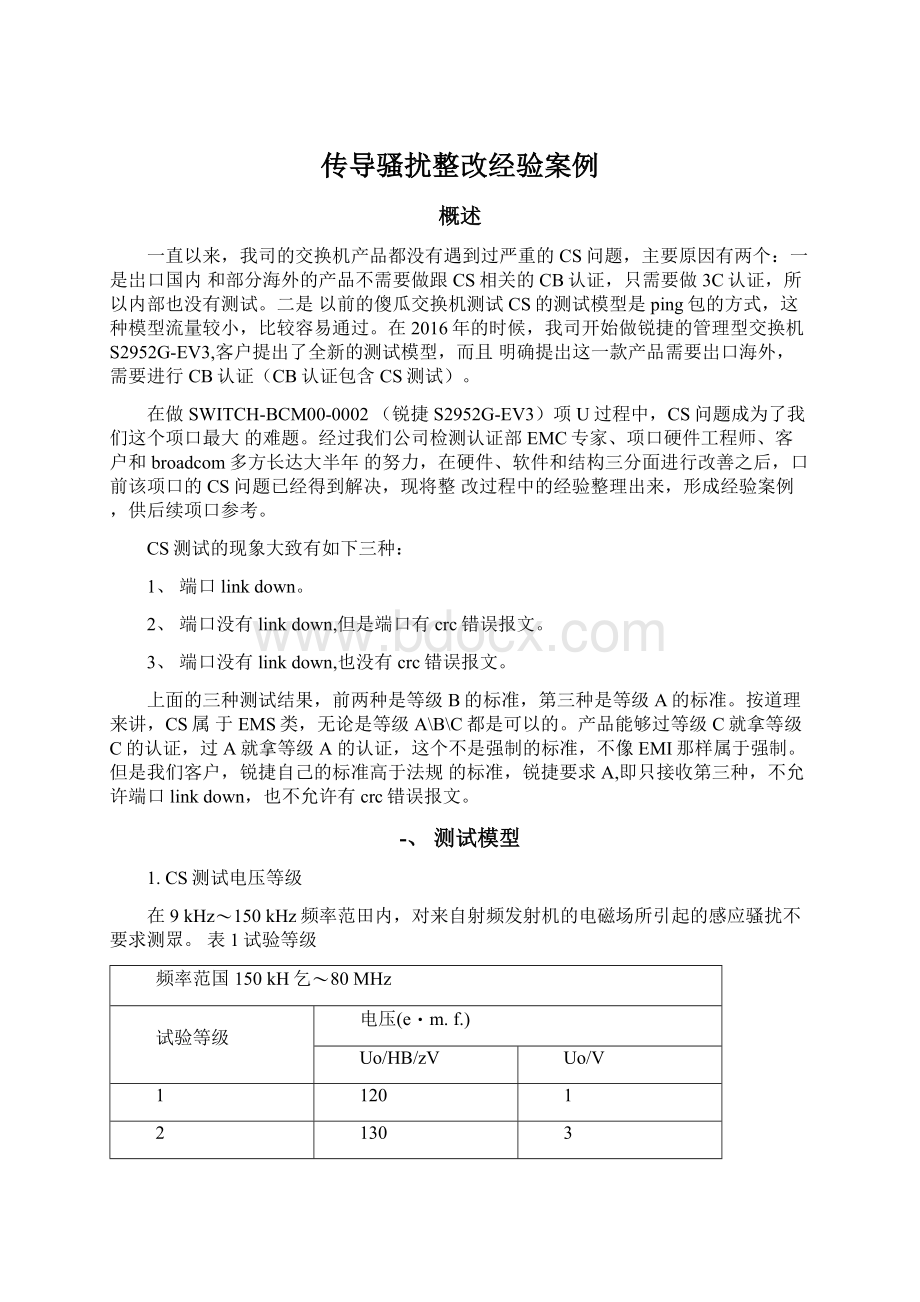

试验等级

电压(e・m.f.)

Uo/HB/zV

Uo/V

1

120

2

130

3

140

10

X

特定

注:

X是一个开故等级。

如表1所示,以有效值(匕m・s.)表示未调制骚扰信号的开路试验电平(e.在耦合和去朝装

置的受试设备端口上设亘试验电平(见6.4.1),测量设备时,该信号是用1kHz正弦波调幅(80%调制度)来模拟实际骚扰影响。

实际的幅度调制如图4所示。

附录C中给出选择试验等级的指南。

说明:

以3V的测试电压为例,3V为有效值,未调制信号的绦峰值为(3V/0.707)*2=4.2438V*2=8.486V,所

以80%调制的信号的稣il床值为&

486V*1.8=15.27Va

二、锐捷在我司的交换机,测试等级都是3V。

2.CS测试仪器

CS的测试仪器分为如下三部分:

射频信号源。

功率衰减器T2:

6db衰减°

注入钳:

分为电流注入钳和电磁注入钳。

(我司为电磁注入钳,信宝那边为电流钳,法规规左如果两种的测试结果不一致,以电流注入钳为准)

3.锐捷网口CS测试模型

锐捷对于测试环境的具体的要求如下:

网线长度:

JDM项目网线长度为0.8米。

端口速率:

端口的最高速率,千兆产品需要测试端口为千兆的情况,不允许降低速率为100松或者10M去测试。

(对于千兆的产品,千兆一般是最难通过的,100M和10M因为采用的编码原理不一样,速率更低导致容错率很高,CS—般不会有什么问题)

端口数量:

需要满载测试,全部端口都要接上,不允许只接部分端口。

(只接部分端口,特别是只接测试端口和辅助端口,其他端口不接的情况,跟满载测试的测试结果有很大的不同,这一点已经得到了验证。

)

测试电压:

3Vo

驻留时间:

1S,认证和客户那边都是测试IS。

测试频率:

0.15MHZ-80MHZ。

查看测试结果:

在测试之前需要clearlog和clearcounter,测试过程中,拔掉串口线。

测试完成之后,接上吊口线,查看showlog和showinterfacecountererr.不允许有端口down的情况,不允许有CRC。

即要求为CLASSAo

如下是测试过程中的LOG。

■log

二、Layout影响分析

1.LED灯线

在进行CS测试时,高压侧的MDIX线上面的干扰能量会很大,假如它旁边有走线,那么干扰的能量将会串扰到旁边的走线上,进而跑到系统端去,影响整个系统的稳定。

下图中高亮的线是S2952第一版的灯线,从中可以看出,灯线跟网口的走线交义在一起了,有些地方棋至有部分重叠。

这就导致在进行CS测试时,干扰能量从灯线串到系统端去。

抑制这个吊扰上的能量的最好的方法是断开这个通路,LED灯做单独的灯板显示,但是在52口的设备中,是没有空间去做灯板的,所以这个通路不能去掉。

只能想办法增大这个灯线上对干扰频率的抑制能力。

最后我们的解决的办法是把600欧姆磁珠改为1000欧姆或者更高阻抗的磁珠。

将这一条通路上面的能量抑制到最低。

最终,我们选择了如下这个物料:

2060210010041197电子料—电感一磁珠Chip.FB」000Q,±

25%,0.49

Q,350mA,0402,BLM15AX102SN1D(Murata)

在进行CS测试的过程中,发现一个现象。

在测试某个端口时,不仅测试端口和辅助的端口会

linkdown,连相邻的端口也会linkdown。

例如,测试端口gel2时,不仅gell>

gel2会linkdown,连ge9、gelO也会linkdown。

后面我们做了这样的实验,将某个端口飞线出来测试。

这个时候,许多端口的相邻端口发生linkdown的问题得到了解决。

结合PCB分析,发现网口高压侧的MDIX线,有部分端口有重叠的现象。

高圧侧的MDIX差分线的重叠,会造成他们之间的串扰会加大。

不仅会造成白米网线测试容易丢包,还会造成CS测试时,相邻端口容易down的问题。

如下是两种LAYOUT的对比。

我司原版的LAYOUTo

锐捷改板改进的LAYOUTo

3.MDIX走线不能过长

PHY到网络变压器的MDIX走线过长,也会影响端口的CS。

MDIX走线过长,首先会影响网口的信号质量,特别是千兆眼图的信号的幅值会降低。

在我司原来的PCB上,左边的24个口MDIX走线过长,导致眼图儿乎都不达标。

即使把MAC和PHY芯片的

Rdac电阻调低到最小,(芯片规格书要求必须在5%范围内,选用1%精度的电阻,我们选用115K的),其千兆眼图的幅值还是会偏低,达不到IEEE802.3标准的要求。

我们专门对比测试S2952老板子的左边24个端口和右边24个端口,发现左边24个端口比右边24个端口CS测试更加容易出问题。

他们的区别就在于左边24个端口的MDIX的走线较长,眼图不达标。

右边24个端口的MDIX走线较短,眼图质量满足要求。

如下是我司第一版的PCB。

如下是最终改板的PCB走线图,从图中可以看岀,我们调整了主芯片的位置,保证了每个芯片的MDIX走线不会过长,最终这个方案下所有的端口的CS都能达标。

三、主板上关键器件影响分析

1.阻容方案

在整改CS的过程中,我们验证过如下儿种方案:

1、在MDIX差分线上面串接1・3欧姆电阻。

2、在MDIX差分线上面并联4.7PF电容,10PF电容,及去掉该电容。

3、在变压器的中心抽头(PHY侧),调整抽头的电容为102,103,104。

4、在变压器的中心抽头(RJ45侧),调整抽头的电阻为0欧姆,75欧姆,150欧姆。

5、任变压器的中心抽头(RJ45侧),调整抽头的电容为68PF,100PF,1000PF,10000PF“

6、更换网络变压器。

实际验证发现,前面5种方案并没有对CS有明显的改善,只有第六种方案,更换网络变压器对CS测试的效果明显,所以我们重点验证不同的网络变压器。

2.网络变压器方案

在验证网络变压器的过程中,方案细分如下:

1、验证不同品牌的共模线圈朝PHY侧的网络变压器。

2、验证不同品牌的共模线圈朝RJ45侧的网络变压器。

3、验证不同品牌的双共模线圈的网络变压器。

4、让供应商针对性的对CMRR这个参数进行改善,验证对CS的改善效果。

在验证过程中,方案一、二、三都对CS的改善效果不是很明显。

所以,我们从理论进行分析,给网络变压器的厂家提出方案,让他们给我们做出CMRR性能更佳的网络变压器。

最终,攸特给我们做了儿款网络变压器,最后发现型号为UTG72T22的效果最好。

一般的网络变压器的CMRR参数,在1-100MHZ内,至少达到-30db°

UTG72T22这一款变压器,在这一个参数上进行优化,可以达到-35dbo从供应商那边了解到,他们改善CMRR的方法是通过调整共模线圈的磁环的配方,增加共模线圈上绕线的圈数。

ElectricalSpecifications@25°

C

OCL:

350uHMin.@100KHz/0.1Vwith8mADCBias

Hi-POT:

1500Vrms

TumRatio:

1:

1±

3%

LK:

0.5uHMax@100KHz/02V

Cw/w

120PFMax@100KHz/0.2V

D.C.R:

1.4ohmMax

InsertionLoss:

1-100MHz-1.0dBMax

CrossTalk:

1-100MHZ:

-30dBMin

CMRR

1-100MHz:

-30dBMin

ReturnLoss:

1-30MHz

40MHz

50MHz

60-80MHZ

80-100MHZ

-18dBMin

-144dBMin

-13.1dBMin

-12dBMin

-10dBMin

四、结构方而影响分析

在CS整改过程中,我们发现结果对于CS的影响也是非常大。

主要在两个方面,一是SGCC和SECC两种不同的板材对我们CS影响很大,二是接地孔。

1.SGCC和SECC

一般机壳的五金材料包括两种,SECC和SGCC。

SECC:

电镀锌钢板,具有优越的耐腐蚀性,耐腐蚀性跟镀锌层的厚度有关,也保持了冷轧板的加工型。

但是其导电性能较差,特别表现在搭接处的电气连接较差。

SGCC:

热浸锌钢板,目前大陆这边暂时无厂家可以生产,主要从台湾和国外进口。

其导电的性能比SECC要好。

SGCC分为大锌花和小锌花两种,小锌花的生产工艺要求更加高,但是小锌花的耐腐蚀性更加好。

所以我们尽量要求厂家给我们小锌花的。

从价格上,以前SECC比较有优势,但是H前大陆这边成本上涨比较厉害,导致SGCC反而更加有价格优势,所以出现这种情况,以前为了节省成本,很多厂家从SGCC切换到SECC,现在乂从SECC切换到SGCCo

后续建议都釆用SGCC的机壳,因为SGCC的导电性能更加好。

这在EMC的测试中,有显著的好处。

专门对比S2952同一个批次的PCB,分别放在SGCC和SECC的机壳中去测试其CS性能,对于特定的儿个端口,SGCC材质CS能够过4V,而SECC只能够过3V。

SECC的颜色比SGCC较暗一些,较好区分,参考如下的图。

SECC(±

盖、下盖和后而):

2.

接地孔

从本次CS的测试中,接地点对CS的影响也非常的大。

SECC材质的老机壳的接地点接地性能不是很好,因为SECC机壳上而有一层电镀的锌,这一种工艺导致接触点阻抗加大。

在验证CS的过程中,老机壳经常需要把接地孔上面的锌层刮开,CS才能过。

SGCC材质的新机壳的接地点接地性能要明显更好。

刮开和不刮开接地孔上而的那一个锌层对测试结果的影响不大,说明这种方式的接触是非常良好的。

3.结构上其他的方面

一、机壳的折边对于RJ45同下盖之间的连接性能的好坏起到重要的作用,机壳增加折边,对于EMC最明显的改善效果是雷击,ESD等,我们这一次没有不折边的机壳,无法对比一个数据输出来,证明折边的效果,但是从理论分析来看,折边对于更好的将干扰接到大地有好处,建议后续所有机壳都加上折边。

二、在机壳生产过程中,需要尽量控制好喷漆工艺。

特別注意上下壳之间的接触点不要有喷漆,这样会非常影响机壳的接触。

可以让五金厂在生产的过程中,把重要的不能喷漆的地方用胶布粘好。

如下是没有控制好喷漆步骤的机壳。

五、软件影响分析

1.软件的寄存器配置对CS的影响

本次项目CS的解决还需要修改PHY相关的部分寄存器,这些寄存器的目的是增加MAC和PHY芯片的接收阈值的容错能力,但是这些寄存器并没有对客户开放,我们和锐捷都问过broadcom几次,但是broadcom觉得这些寄存器的说明涉及机密,并没有提供给我们。

值得一提的是,broadcom第一次提供的寄存器配置(“解决CS相关配程l.txt”),还导致新的问题-…电口不支持jumbo帧。

需要导入“解决CS配巻2-解决jumbo帧.txt”这个脚本,才能解决jumbo帧问题。

所以,后续我们如果因为CS问题,要对PHY寄存器进行修改,需要重点验证jumbo帧是否支持。

具体的脚本和原厂的邮件回复如下。

阿沛跑«

1・txt

□

REli^nt-56152

CSliWfl动msg

六、总结

从这个项目中,我们发现CS的影响因素主要分为layout,结构,软件和变压器这四个方而,后续大家可以从这四个方面进行CS的优化。