《数字电路设计》课堂笔记整理段成华老师Word文档格式.docx

《《数字电路设计》课堂笔记整理段成华老师Word文档格式.docx》由会员分享,可在线阅读,更多相关《《数字电路设计》课堂笔记整理段成华老师Word文档格式.docx(55页珍藏版)》请在冰豆网上搜索。

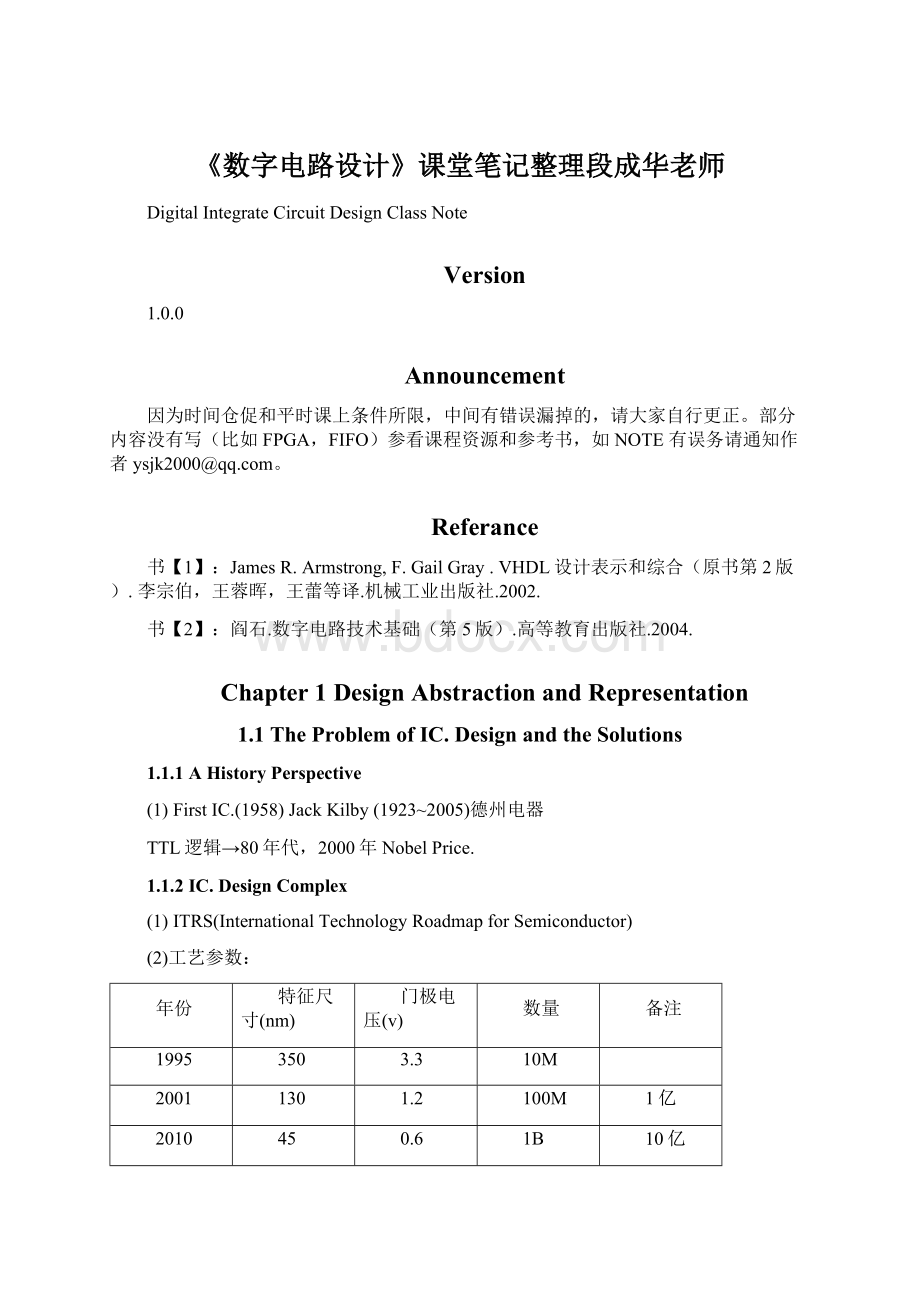

4.2

100B

(3)Complex

FeatureSize(特征尺寸):

Gate-equivalentCorrespondstoa2inputNANDgate

做一个与非门的面积

λ法则

λroughlyhalfthelengthofthesmalltransistor.

Reliably(可信性)variability(变化性)

(4)Solution

解决复杂性的方案

A.DesignAbstraction设计抽象

B.FormalRepresentation正式表达

1.2DesignRepresentation

1.2.1Y-chart1983DanielD.Gajski

(1)Abstractlevel见书【1】Page2表1-1

1

Systemlevel

系统级

2

Chiplevel

芯片级

3

Register-Transferlevel

寄存器级

4

Logicgatelevel

逻辑门级

*

Switchlevel

交换级

5

Circuitlevel

电路级

6

Layoutlevel

版图级

*为老师所讲可忽略一级

(2)MainComponentsofY-chartrep.

a)Behavioralrep.(BR,BD)

Def.:

adesignasablackboxanddescribesitsoutputintermofitsinputandtime,indicatingnoinformationabouttheimplementationorstructure.

Example:

noanygeometricinformationtosomeextent,nostructureinformation.

b)StructureRep.(SD,SR):

Ablackboxisrepresentedasasetofcomponentsandconnects(interconnection).

ActingabridgebetweenBRandGR,nophysicalinformationiscontained.

(3)GeometricRep.(GR,GD)

a)Def.:

Specifyingsize(heightandwidth)ofeachcomponents;

thepositionandinterconnectedonsilicondie.

1.2.2HardwareDesignlanguage(HDL)

AnexampleofmodelHDL:

1970s

Specification

Portinv(in)→out

(1)Nfetoutinvss

(2)Pfetoutinvdd/end

高级语言

↓

低级语言

创建时Delay问题

并发性

AVHDLexample

;

ENTITYOR2IS

Port(i1,i2:

inbit;

ooutbit);

ENDOR2

ARCHITECTUREDOFOR2IS

BEGAIN

o<

=i1ori2

END

OneHDL

●Forsynthesis生成硬件

●Forsimulation仿真

●Fastvector测试矢量

功能描述有延时,行为描述无延时

BehaviorDescription

Algorithmicdescription算法描述

Dataflowdescription数据描述(functiondescription,功能描述)

Implystructureinformation数据表示

1.3StructureDesign

1.3.1BasicDefinition

(1)Abstractionhierarchy抽象层次:

Asetofinterrelationrepresentationlevelsthatallowasystemtoberepresentedinvaryingamountsofdetail

(2)Computationalstep:

Dataprocesstime时钟周期

1.3.2DesignandimplementationProcess

RelationshipBetweenDesign(Logic)andImplementation(physical)

PCB有芯片直接焊制在板子上.

FPGA(FieldProgramGateArray)现场可编程门阵列.

DesignCycles

Synthesis:

TheprocessoftransformingonrepresentationIntoanotherrepresentation.

Synthesis=translation+optimistic

Designcycles:

aseriesofsynthesissteps.

Systemlevelsynthesis:

mappingatask-levelspecification(系统级的规范)onaheterogonoushardware/softwarearchitecture.

physicalsynthesis物理综合

RTL→layout从行为域到几何域

1.3.3IPsandY-chartrep

IP:

IntellectualProperty知识产权,表示预定义组件(predefinemodule)

●Eachabstractionlevelneedsadatabaseofcomponents

●Eachcomponenthasthreemodel(B,G,S)

a)Behaviormodel(modelofcomputer)

b)Structuremodel(hardIPcore)

c)Physicallayoutmodel(fixedIPcore)

Structuredesigndecomposition

KeyQuestion

ModelSize50k~500k(门数)

Howmanyclocks?

Oneofeachmodule

DesignTree

DigitalDesignSpace

1.4DesignFlow

1.4.1FPGA/CPLDDesignflow

1.4.2ASICdesignflow

1.4.3SoCDesignflow

1.5DesignTools

Highlevelsystem-level,chip-level.

Classification:

1designentry

2logicdesign

3physicaldesign

4verification

5highlevelsynthesis

Chapter2DigitalLogicDevices

2.1BasicConcept

2.1.1CategoriesofDigitalLogic

(1)Standardproducts(Detailedgeneralpurposedevise.TTLseries74)

(2)ProgrammableLogic

PAL:

可编程阵列逻辑

GAL:

GenericArrayLogic

PROMPLD

CPLDFPGA

(3)CustomLogic(standard-cell)

2.1.2ElectricalParametersofDigitalIC

States:

high

low

off

3-state

short-circuit

elay:

Tpd:

Propagationdelay

2.2CommonUseGeneralPerposeLogic

2.2.1BasicLogicgates

Inverter:

NAND,NOR,XOR,NXOR

2.2.2D-flip-flops

tsu:

Setuptime

thd:

Holdtime

tco:

C时钟,O输出

2.2.3Bi-stablelatch

不对称电路会带来竞争,产生毛刺如右图

2.2.4BinaryCounter

2.2.5SynchroniesCounter

2.2.6Multiplexer(MUX)多路开关

C0→Y1

00

C1→Y1

01

C2→Y1

10

C3→Y1

11

多布尔述如下:

2.2.7Bustransistor

2.3ProgrammableLogicDevice

2.3.1PAL可编程逻辑阵列

书【2】page392

(1)BasicPLAArchitecture

(2)PALNotaton

a)ANDarray

b)PALArchitecture书【2】P392

c)PALOutputstructure

ActiveLOWBi-diroutput书【2】p394图8.3.4

ActiveHigh书上没有

Registeredoutput书【2】p395图8.3.6

XORregisteroutput书【2】p396图8.3.7

2.3.2GAL通用阵列逻辑

书【2】P402

OutputlogicMacroCell(OLMC)书【2】P405图8.4.4注意该图有错误,对照老师作业2中所留图片

2.4CompleteProgrammableLogic

Chapter3BasicVHDLModelingTechnique

3.1Introduction

3.1.1Significance

1)ProcessControl,Standardization,RiskControl.

2)Automation—EDA:

Synthesis/Simulation

3)VLSITesting

3.1.2Standards

●1979s:

initialdefinition

●Late1970s:

VHDLprojection

●1987:

ieeestdVHDL1164released

●1993:

ieeestdVHDL1076released

●2001:

ieeestdVHDL1076rareleased

3.2DesignEntity

3.2.14-bitEqualityComponents

Designcase

1)RTLschematicdesign(rightfigure)

2)VHDLDesign(DataflowModel)

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

--引入库

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYeqcompfIS--定义实体

PORT(a:

INBIT_VECTOR(3DOWNTO0);

b:

Equals:

OUTBIT);

ENDeqcompf;

ARCHITECTUREdataflowOFeqcompf–-结构体内为并发语句,写入进程内为顺序

BEGAIN--语句。

Equals<

=’1’when(a=b)

Else‘0’;

ENDdataflow;

3.2.2DesignEntityConcept

ThedesignentityistheprimaryhardwareabstractioninVHDL.Itisdefinedbyanentitydeclarationtogetherwithacorrespondingarchitecturebody.

Entity:

●Definesthestaticcharacteristicofhardwareincludingitsrangeandinterface.

Interface:

consistence,variable,signal,file

●Representsanentitysystem,acircuitsboardchipandalogicgate

●Declareallinandoutports

Architecturebody:

●Definethedynamicdeclarationsofhardware(behavior)

●Multiarchitecturecanbedefinedofthesameentity

●Definestyles(types)

3.2.3Entitydeclaration

1)BNF(Backs-newformat)ofentitydef.

ENTITY[entityname]IS

Port([signalidentifier]:

[mode(in/out/buffer)][signaltype];

……);

END[entity][entityname];

a)ports

●EachI/Osignalinentitydeclarationiscalledaport

●Aportisadataobjectanditcanbeassignedvalueorusedinstalement

b)Mode:

declarethedirectionofdatatransfer(in/out/inout/buffer).buffer设定信号的输入输出

c)Type(signalport)

Boolean/bit/integer:

supportbyieee.1076,1993

Std_logic:

ieee.1164,1987

U:

unsolved(resolution)

3.2.4ArchitectureDefinition

1)BNF:

ARCHITACTURE[arch.name]OF[entityname]IS

[typedeclaration(signaldef./constantdef./componentsdef./alicedef./attri.spec./subprobody)]

[processstatement]

END[arch.name]

2)example

a)typedef.

TYPEBITIS(‘0’,’1’);

TYPESTATE_TYPEIS(st0,st1,st2);

b)signaldef.

SIGNAL[static]:

[statictype]

SIGNALx:

BIT;

d)constantdef.

CONSTANTzi:

STD_LOGIC_VECTOR(7DOWNTO0):

=”00000000”;

e)componentsdef.

COMPONETSAND2PORT(ij:

INSTD_LOGIC;

k:

BUFFERSTD_LOGIC);

f)alicesdeal

SINGNALaddr:

STD_LOGIC_VECTOR(31DOWNTO0);

ALIESTOaddr:

STD_LOGIC_VECTOR(3DOWNTO0)ISaddr(31DOWNTO28);

g)attributespec

TYPECONSTISINTEGRATERANGE(0TO27);

CONST‘LEFT(=0);

h)Subprogrambody

FUNCTIONmajority(a,b,c:

BIT)RETURNBITIS

RETURN(aANDb)OR(aANDc)OR(bANDc);

ENDmajority;

3.3DesignDescriptionStyle

3.3.1BehaviorDescription(BD)

comp:

PROCESS(a,b)–敏感表

IFa=bTHEN

equal<

=’1’;

ELSIF

=’0’;

ENDIF;

Endcomp

FeatureofBD

(1)BDisconductaccordingtoalgorithmpart;

(2)BDishighleveldescription

(3)BDindicatesonormoreprocesswitharch.Body

(4)Sequentialstatement

ARCHITECTURE

P1–进程内顺序执行--┐

P2--│--进程间并发执行

P3--┘

3.3.2DataflowDescription(DD).

ARCHITECTUREbulOFeqcompIS

Equal<

=NOT(a(0)XORb(0))

ANDNOT(a(0)XORb(0))

ANDNOT(a(0)XORb(0));

ENDbul;

FeatureofDataflowDescription:

●DDuseconcurrentstatementinsteadofsequentialstatement;

●Thesignalassignmentstatementsrunconcurrently;

●DDimpliessomestructureinformation.

3.3.3StructureDescription

ARCHITECTUREstructOFeqcomp4IS

SIGNALx:

STD_LOGIC_VECTOR(0TO3);

U0:

XOR2portmap(x(0),a(0),b(0));

U1:

XOR2portmap(x

(1),a

(1),b

(1));

U2:

XOR2portmap(x

(2),a

(2),b

(2));

U3:

XOR2portmap(x(3),a(3),b(3));

U4:

XOR2portmap(x(4),a(4),b(4));

ENDstruct;

ENTITYeqcomp4IS

……

END;

ENTITYXOR2IS

PORT(d0,d1:

INBIT;

q0:

OUTBIT);

ENDXOR2

ARCHITECTUREXOR2IS

ENDXOR2;

ARCHITECTUREstructOFeqcomp4ISCOMPONENTXOR2;

--实体之前写入lib说明,否则放于最后容易出错。

FeatureofSD

(1)SDcallscomponentsinLibusingUSEdeaseandgetstheinstructuralcomponents.

(2)Concurrentstatementsareused.

(3)Ifconsistentofnetlist……(这里没有记录完整)

3.3.4Comparation

Differentdescriptionsstyleleadtodifferentimplementswithdifferentsources.

(1)redundantlogic多余逻辑

(2)Generalandrenderspecificcomponents

General(BD):

portability;

Renderspecific(SD):

nonportability.

3.3.5SequentialStatement

Statementthatexecuteinthesequencearecalledsequential