电压控制LC振荡器毕业设计文档格式.docx

《电压控制LC振荡器毕业设计文档格式.docx》由会员分享,可在线阅读,更多相关《电压控制LC振荡器毕业设计文档格式.docx(25页珍藏版)》请在冰豆网上搜索。

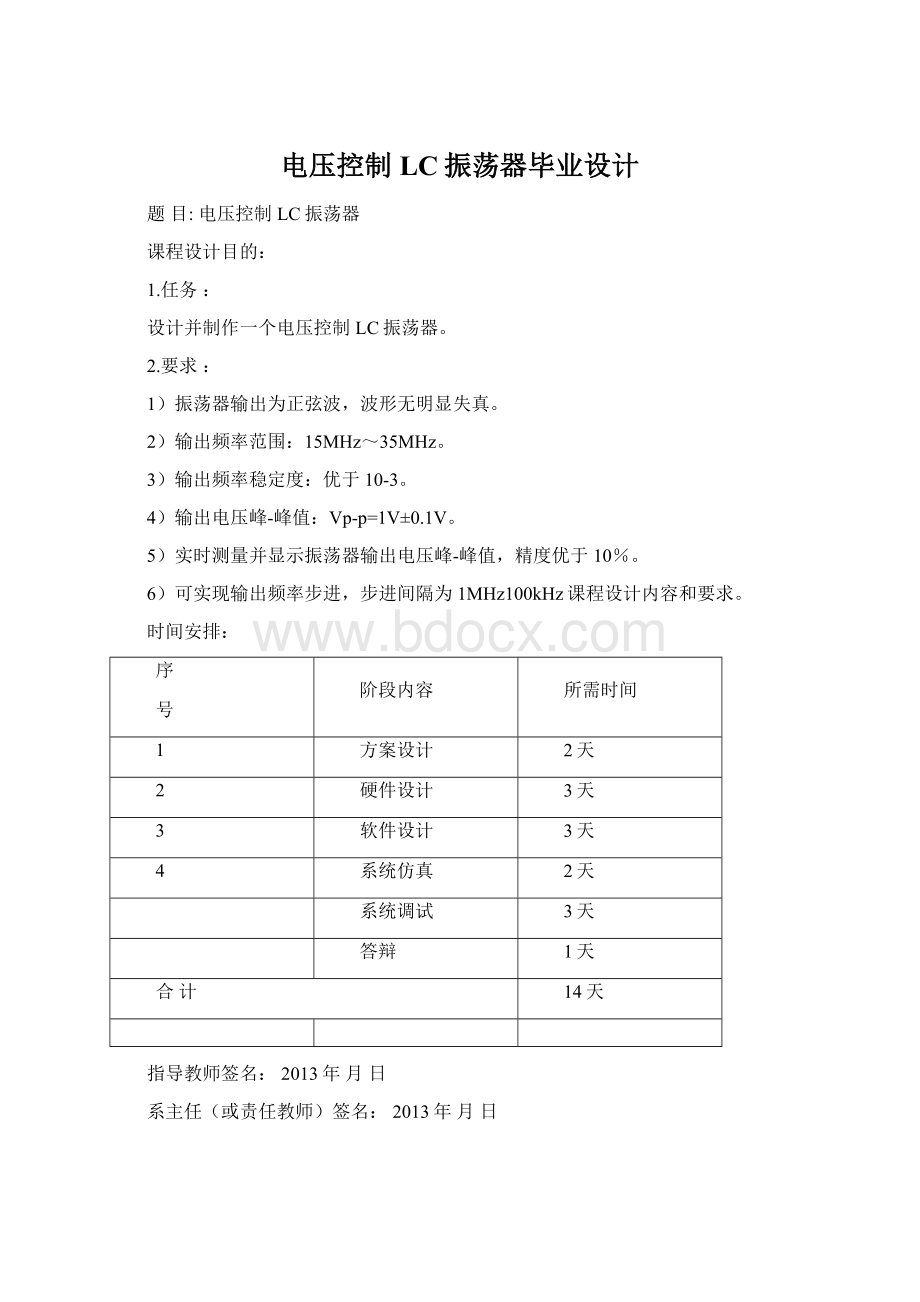

系统调试

答辩

1天

合计

14天

指导教师签名:

2013年月日

系主任(或责任教师)签名:

摘要

本设计描述了电压控制LC振荡器的设计思路,实现的方法及测试方法和测试结果。

本设计采用西勒振荡器作为振荡器的主体部分,解决了基本三点式振荡设计改变振荡频率必改变反馈系数的矛盾,通过改变变容二极管两端的电压来调节振荡器输出频率实现输出在15MHz-35MHz范围内可变,通过VCO改变频率实现频率合成并稳定频率,通过功率放大器使电路输出电压控制在1V。

设计以单片机为控制核心,实现频率和电压值的实时测量及显示并控制频率步进。

本电路在调频部分为提高输出频率精度,采用单片机控制主振器参数,根据产生不同的频率范围控制不同的主振器参数而达到提高精度和稳定度的目的。

关键词:

VCO单片机变容二极管

Abstract

ThisdesigndescribesthevoltagecontroloscillatordesignideaofLC,therealizationmethodandthetestmethodandtestresults.ThisdesignusestheSeileroscillatorasthemainpartoftheoscillator,thebasicthreepointtypeoscillatingdesignchangestheoscillationfrequencywillchangethecontradictionoffeedbackcoefficient,voltagebychangingthevariablecapacitancediodeendstoadjusttheoutputfrequencyoscillatoroutputintherangeof15MHz-35MHzvariable,throughVCOrealizethefrequencysynthesisandfrequencystability,controlin1Vthroughthepoweramplifiercircuittomaketheoutputvoltage.Thedesignofsingle-chipmicrocomputerasthecontrolcore,real-timemeasurementanddisplaytorealizethefrequencyandvoltagevalueandfrequencystep.ThecircuitintheFMpartinordertoimprovetheprecisionofoutputfrequency,usingsingle-chipcontrolofthemainisolatorparameters,accordingtothedifferentfrequencycontrolmasteroscillatorwithdifferentparametersandtoimprovetheaccuracyandthestabilityof.

Keywords:

VCOMCUDIODE

电压控制LC振荡器

1.系统设计

1.1设计要求

(1)任务

(2)要求

6)可实现输出频率步进,步进间隔为1MHz100kHz。

1.2设计思路

根据系统的设计要求,拟采用基于单片机控制的系统结构。

本系统可分为三大部分:

电压控制LC振荡源电路、锁相环稳频步进电路和单片机控制的测控和显示电路。

首先VCO振荡器采用分立元件构成的电容三点式西勒振荡电路,采用数字锁相环式频率合成器技术,由时钟发生电路、鉴频/鉴相器(FD/PD)、可变分频器(÷

N)和压控振荡器(VCO)组成。

利用锁相环,将VCO的输出频率锁定在所需频率上。

可以很好的选择所需频率信号,抑制杂散分量,并且避免了大量的滤波器。

控制部分采用单片机来完成,结合AD测量出电压的峰峰值,并利用液晶显示模块显示输出设定的输出频率及电压峰-峰值,另利用键盘模块来完成对频率的步增步减功能。

1.3方案比较与论证

1.3.1振荡电路方案选择

LC振荡器的输出频率由电感L与电容C的值决定,通过改变L或C可以改变振荡频率,利用变容二极管可以构成压控振荡电路,改变加在其PN结上的反向电压可以调节其容量,从而实现电压控制LC振荡。

方案一:

采用分离元件构成压控振荡器电路,主要由变容二极管MV209构成西勒振荡电路。

其结构简单,但由于使用分立元件组成,电感量及其它阻容元件的参数计算复杂,调试较困难。

方案二:

采用集成的压控振荡器电路,如图1.2所示,选用压控振荡器芯片MC1648,其工作电压5V,工作频率可从1.0MHz~150MHz,需要外接一个并行的LC槽路,另外,MC1648内部有放大电路和自动增益控制,可以实现输出频率稳幅,射极跟随器有隔离作用,可减小负载对振荡器工作状态的影响。

图1.2方案二压控振电路

综上所述,虽然采用压控振荡器芯片调试简单,但芯片相比分离元件较贵,同时,采用分离元件构成压控振荡器电路可以锻炼同学们的动手能力,因此选择方案一。

1.3.2锁相环频率合成方案

为了实现输出频率步进以及输出频率有高度的稳定性,可以采用锁相环频率合成技术,其频率步进可以为任意值,频率稳定度与参考晶振的稳定度相当,达到10-5。

模拟锁相环路法,通过环式的减法降频,将VCO的频率降低,与参考频率进行鉴相。

优点是:

可以得到任意小的频率间隔;

鉴相器的工作频率不高,频率变化范围不大,比较好做,带内带外噪声和锁定时间易于处理。

不需要昂贵的晶体滤波器,频率稳定度与参考晶振的频率稳定度相同。

缺点是分辨率的提高要通过增加循环次数来实现,电路超小型化和集成化比较复杂。

数字锁相环路法,如图1.3所示,应用数字逻辑电路把VCO的频率降低到鉴相器的参考频率上,采用的是除法降频。

综上所述,方案二具有方案一的优点外,克服了方案一的缺点,利用灵活方便的数字电路,做成数控可变分频,得到任意的频率,且便于集成化,大大简化电路连线,缩短电路制作时间,降低整机体积。

因此采用方案二。

图1.3数字锁相环频率合成原理

1.3.3控制电路设计方案

系统的控制电路完成输出频率控制,显示控制,键盘控制等。

采用单片机控制,灵活方便,能较大限度的开发其资源,价格低廉,软件编程简单。

采用FPGA(现场可编程逻辑门阵列)作为系统的控制核心。

由于FPGA具有强大的资源,使用方便灵活,易于进行功能扩展,特别是结合EDA(电子设计自动化),可以达到很高的效率。

综上所述,虽然FPGA控制灵活方便,但我们对单片机知识掌握的更充分,因此选择方案一。

1.4系统整体设计

综合以上选定的方案,得到系统总体框图如图1.4所示。

图1.4系统方框图

2单元电路设计

2.1压控振荡器的设计

2.1.1振荡电路原理

本设计选用西勒振荡器作为振荡电路,对于一个振荡器,首先要判断它是否能产生振荡,其振荡频率可根据选频网络的参数进行计算。

要满足振荡电路自激振荡,则必须满足电路产生振荡的基本条件,即使电路中的反馈信号与输入信号大小相等,相位相同。

正弦振荡电路由A放大电路和F反馈网络组成。

满足下列条件电路起振。

1、振幅平衡条件

振荡电路产生自激振荡满足振幅平衡条件

式(2—1)

即放大倍数与反馈系数乘积的模为1,反馈信号与原输入信号的幅度相等。

2、相位平衡条件

振荡电路产生自激振荡时满足相位平衡条件

式(2—2)

即放大电路的相移与反馈网络的相移之和为2nπ,引入的反馈为正反馈,反馈端信号与输入端信号同相。

经分析西勒振荡电路的振荡原理得出高静态工作点Q的谐振回路是电路起振的关键。

Q的值不高就无法从丰富的频率中选出可以构成自激振荡的频率分量构成正反馈,振荡电路据无法正常起振。

谐振回路的Q值是反映回路在谐振时的能量损耗。

损耗越小,Q值越高。

解决这个问题的方法是尽可能选择高Q值的L和C。

一般情况下,电容的值较高,不会对电路的Q值构成影响。

电感成为影响谐振回路的主要因素。

理论上讲空心的电感线圈损耗较小,Q值较高,满足电感值较小无法回路的需要。

经过反复实践,选频网络最好选用高频材料镍芯材料绕制的电感。

2.1.2西勒振荡器电路

图2.1西勒振荡电路

如上图2—2所示是西勒振荡器的原理图电路图。

C4电容调整振荡器的频率,而C3用固定电容,在一般情况下,C1和C2电容都远大于C3,其振荡频率近似为

式(2—3)

式(2—3)是振荡频率计算式。

调节C4电容改变振荡器频率,由于C3电容不变,所以谐振回路反映到晶体管输出端的等效负载变换很缓慢,故调节C4对放大器增益的影响不大,从而保证振荡幅度的稳定,其频率覆盖系数较大,可达1.6~1.8。

2.1.3电压控制LC振荡电路

在本设计中LC振荡器电路采用了改进型电容三点式振荡器中的经典的西勒振荡电路,减弱了晶体管与振荡电路中谐振回路的耦合,使其频率稳定度可达到10-5~10-4数量级。

该电路频率稳定性高,输出幅度均匀,调谐范围也比较宽。

电路原理电路图如图2.2所示。

压控振荡器的作用是产生频率控制电压变化的振荡电压。

其特性可用调频特性即瞬时振荡角频率相对于输入控制电压的关系来表示,在一定范围内瞬时振荡角频率和输入控制电压是成线性关系的。

因此可得出瞬时振荡角频率是压控振荡器的中心频率和压控电压为零时的振荡频率和压控灵敏度积的总和。

图2.2压控LC振荡器电路原理图

电路原理说明:

该压控振荡器由西勒振荡器组成,其中由R1、R2、R3及晶体三极管Q1等组成振荡电路,由C3、C4、C5、Rp1、L2及变容二极管等元器件组成振荡器的选频网络,完成频率选择。

通过调节可变电阻Rp1来改变电压的大小,从而改变变容二极管两端的电压,使输出频率发生改变,达到设计目标中电压控制LC振荡器的指标。

耦合电容C6隔离前后极电路,使晶体三极管的静态工作点不受后极电路的影响,工作在放大状态。

VCO产生的振荡频率范围和变容二极管的压容特性有关。

图2.3为变容二极管MV209的测试图。

可利用图中(a)所示的测量电路来测变容二极管的压容特性。

(b)为其压容特性和压控振荡器的压控特性示意图。

从图中可见变容二极管的反偏电压从Vdmin~Vdmax变化,对应的输出频率范围是fmin~fmax。

在预先给定L的情况下,给变容二极管加不同的电压,测得对应的谐振频率,从而可以计算出Cd的值。

减小谐振回路的电感感抗,改变电容容量,不需要并联二极管即可很容易地实现频率扩展。

在本设计中通过该方法使输出频率的范围扩展到15~35MHz。

(a)电容特性测量电路(b)变容二极管压容特性及压控振荡器的压控性

图2.3变容二极管特性测试图

2.2锁相环式频率合成器的设计

锁相环的基本原理框图如图2.4所示。

采用锁相环频率合成,可以得到任意频率步进,同时频率稳定度与参考晶振相当,可以达到10-5。

锁相环路主要由晶振、参考分频器、压控振荡器(VCO)、鉴频/鉴相器(FD/PD)、可编程分频器组成。

它是应用数字逻辑电路将VCO频率一次或多次降低至鉴相器频率上,再与参考频率在鉴相电路中进行比较,通过低通滤波器取出误差信号来控制VCO的频率,使之锁定在参考频率的稳定度上。

fc

ft

图2.4锁相环基本原理框图

2.2.1PLL频率合成电路设计

频率稳定度是指在一定时间间隔内,频率源的频率准确度的变化,所以实际上是频率不稳定度,它表征频率源维持其工作于恒定频率上的工作能力。

各种频率源的频率值由于受内外因素的影响,总是在不断地变化着。

为了提高频率的稳定度我们设计了PLL以提高电路性能。

本设计的PLL与系统构架框图如图2.5所示:

图2.5PLL系统框架

图示虚线框为锁相环路。

它与主振荡器的接口有两个。

一是FVCO,该信号的频率就是压控振荡器(VCO)的频率,另一是误差纠正电压PDO。

FVCO信号经过74HCT74四分频后,再经过CD4059N分频,输出10KHz的信号作为鉴相器CD4046的一路输入信号。

CD4046对两路输入信号进行比较,当两者频率不相同时,CD4046会输出一个误差电压纠正VCO的频率,直到它的两路输入信号频率相等时,PDO呈高阻态。

此时环路称为锁定状态,锁相环路实际上是频率反馈电路。

(f/4N=ft/10,f=N*ft/2.5ft为给4046提供基准比较频率)。

输出频率经倍频fo=2*N*ft/2.5后给功率放大器。

由此可见,输出频率的稳定度与ft相当,当ft为100KHz时,由于N为自然数,所以输出的步进频率为0.1MHz,当N的范围在250到1000变化时,则输出频率可在10MHz到40MHz之间变化。

在10MHz—24MHz之间谐振点为17MHz,在24MHz—40MHz之间谐振点为32MHz。

此模块主要是控制CD4059的分频系数N。

通过锁相环CD4046处理输出电压来达到控制输出频率FVCO目的。

此模块实现方便,电路简洁。

本部分还可实现输出频率步进的粗调上升、粗调下降和细调上升、细调下降的步进方式,为频率值的准确调节带来方便。

CD4060时钟发生器,CD4046鉴相器,CD4059N分频器,构成整个锁相环路系统,CD4059为N分频器,它有多种工作模式可供选择。

在电路中他工作在模式10,BCD计数的模式。

下面举个例子:

要在锁定时发射频率是15MHz。

根据上面所讲,CD4059的分频器系数N应该为375。

在*1000位置0,即D4、C4、B4、A4都断开;

在*100位,C3、D3断开,B3、A3接+5V;

在*10位,D2断开,C2、B2、A2接+5V;

在*1位,D1、B1断开,C1、A1接+5V。

此频率设置过程均由单片机控制。

图2.6是锁相环电路与频率控制仿真电路。

2.3单片机控制模块设计

本系统采用单片机AT89C51,包括键盘模块、显示模块、AD模块等。

负责键盘处理、控制锁相环的可编程分频器,以达到实现频率步进的目的,以及对峰峰值检测电路的A/D输入的数据进行处理。

键盘模块是用于控制系统工作的,设计三个按键,一个检测键,接单片机的P3.2口,一个频率上调键,接单片机的P3.6口,一个频率下调键,接单片机的P3.7口。

显示模块用1602LCD液晶显示屏显示,显示当前输出的频率以及所测的电压峰峰值。

单片机IO口资源分配如图2.7所示:

图2.7单片机资源分配

单片机模块仿真电路图如图2.8所示:

图2.8单片机模块仿真电路

2.4功率放大器设计

本设计采用高频功率放大器,在其设计中首先要考虑的是晶体三极管的选择。

通常在选择过程中晶体管的极限参数将是选择的主要依据。

这些参数包括:

集电极最大允许电流,反向击穿电压,二次击穿,集电极最大允许损耗功率,晶体管的安全工作区等等。

根据本设计的工作频率和输出电压的要求,本设计选用共发射极电路作为放大电路,设计中晶体三极管工作在放大状态。

电路图如图2.9所示。

图2.9功率放大电路的设计

设计中电路采用两级放大实现,利用三极管9018将压控振荡器输出的电压进行放大,前一级电路工作在甲类状态,在频率改变的情况下,电压负反馈使输出电压稳定在1V±

后一级电路可以进一步提高放大器的工作效率。

后级的三极管3DA5109工作在丙类状态,可以提高功率放大器的功率。

T1为中介耦合变压器,能把Q2的功率完全的传输到工作在丙类的Q3上。

为了防止失真过大,输出端采用并联谐振电路。

当负载为容性时,采用串联谐振回路。

这样可以使输出功率和效率都到达最大值。

在该电路中,可以保持输出电压稳定在1V±

为了稳定静态工作点,设计中射极放大电路采用分压式偏置电路,如图3—5所示。

图2.10分压式射极偏置电路

分压式射极偏置电路是常用的一偏置稳压电路,图中Rb1为上偏置电阻,Rb2为下偏置电阻,Rc为集电极电阻,Re为发射极电阻,Ce为电路的射极旁路电容,在电路中起到了使电路的交流信号放大能力不因Re的存在而降低,使电路的放大倍数不受影响的作用。

电路中Rb1、Rb2为基极偏置电阻为三极管建立了合适的基极电压;

Rc电阻起到了使放大电路的电流信号转换为以电压形式输出信号的作用。

放大电路中放大的本质是实现能量的控制和转换,即能量的转换:

把输入的微弱信号放大到所需要的幅度值且与原输入信号变化规律一致的信号,对信号进行不失真放大。

信号由三极管的基极输入,由三极管的集电极输出,基极与发射极之间形成了回路,构成了反馈。

2.5峰-峰值检测显示电路的设计

该电路由二极管和电容构成。

其原理图如2.11所示。

输入电压加到该电路中,正半周时二极管导通,对电容充电,对应一个电压值;

负半周时二极管截止,

电容放电。

因充电时间小,而放电时间常数很大,故运放输入端加进的是一个脉动直流源。

经直流放大器后,输出一个大约几伏的直流电压U0。

U0与给出峰-峰值电压的关系曲线通过实验得到,如图2.11(b)所示。

然后将输出电压经AD转换后送入单片机后就可以直接测得电压峰-峰值。

(a)峰-峰值测量电路(b)Uo-Vp-p曲线

图2.11峰-峰值测量原理

峰值检测电路图如图2.12所示:

图2.12峰值检测电路

3.软件设计

本设计软件分为电压测量显示,频率及电压显示,步进控制三部分。

其中,主程序流程图如图3.1所示:

图3.1主程序流程图

幅值测量程序流程图如图3.2所示:

图3.2子程序流程图

频率步进程序流程图如图3.3所示:

N

Y

4.仿真结果

4.1VCO振荡电路仿真结果

所产生的仿真波形如图4.1所示:

图4.1VCO振荡波形

由图可见,刚接通电源时电路发生自激振荡,电压幅值波动很大,随后趋于稳定。

且波形为标准的正弦波,稳定后的振荡输出波形如图4.2所示:

图4.2稳定后的振荡输出波形

4.2峰峰值检测电路仿真结果

正弦波信号经过设计的峰值转换电路,输入输出信号波形如图4.3所示:

图4.3峰峰值检测电路仿真波形

可见,经转换后,电压不断变化的正弦波变成了与其幅值相等的稳定的直流信号,这样通过AD采样后,即可求得信号的峰峰值。

4.3频率步进波形仿真

通过按键,对频率进行递增或递减,观察递进频率值。

初始时,输出波形如图4.4所示:

图4.4初始时输出波形

可发现,波形周期约为67ns,即14.92MHz,按递增键,得输出波形如图4.5所示:

图4.5按下递增键后的输出波形

观察得,输出波形的周期变为63.43ns,即15.8MHz,步进0.8MHz,与设计要求有一定的误差。

4.4峰峰值及输出频率显示

初始时,输出频率为15MHz,电压测量为990mV,如图4.6所示:

图4.6峰峰值及输出频率LCD显示

按下频率步增S2键,频率输出变为16MHz,如图4.7所示,可见步长为1MHz。

图4.7按下S2键后的显示

5.心得体会

本次课程设计至此已经接近尾声,设计的时间虽然不是很长,但在整个设计过程中收获颇丰。

通过这次课设让我明白了理论和实际操作之间差距,而且也让我很明确得意识到自己在知识上上有很多的漏洞,以后应该多钻研一下。

通过这次课设,我也深刻体会到了自己知识的匮乏。

意识到自己所学的知识的肤浅,只是一个表面性的,理论性的,根本不能够解决在现实中还存在的很多问题。

因此,学习中应多与实际应用相联系。

此外,此次课设所涉及的知识面相当广泛,对我是一个重要的考验和历练。

设计电压控制LC振荡器,包含了基本的模电知识、数电知识、高频原理,同样也需要掌握单片机知识、EDA知识。

无论是对于软件的设计还是硬件的设计,都有着相当高的要求。

总之,通过这次设计,不仅使我对所学过的知识有了一个新的认识。

而且提高了我分析问题及动手操作的能力。

使我的综合能力有了一个很大的提高。

6.参考文献

1高吉祥,黄智伟,陈和.高频电子线路[M].北京:

电子工业出版社,2003年第一版

2.黄智伟.无线数字收发电路设计[M].北京:

电子工业出版社,2003年,第1版

3.邹其洪黄智伟高嵩.电工电子实验与计算机仿真[M].北京:

4.吴运昌.模拟集成电路原理与应用[M].广州:

华南理工大学出版社,2001年第一版

5.全国大学生电子设计竞赛组委会.第五届全国大学生电子设计竞赛获奖作品选编[M].北京:

北京理工大学出版社.2003年1月第一版

6.甘历.VHDL应用与开发实践[M]北京:

科技出版社.2003年第一版

7.赵俊超.集成电路设计VHDL教程[M].北京:

北京希望电子出版社,2002年第一版

8.童诗白.华成英.模拟电子技术基础[M].北京:

高等教育出版社,2001年第三版

7.附录

单片机控制程序如下所示:

#include<

reg52.h>

#include<

intrins.h>

#defineucharunsignedchar

#defineuintunsignedint

uintN=375;

uintvalue;

sbitadwr=P3^6;

//定义AD0804的转化信号端口

sbitadrd=P3^7;

//定义AD0804的读信号端口

sbitjia_key=P3^6;

//进行自增计数按键端口

sbitjian_key=P3^7;

//进行自减计数按键端口

sbitcontrol_key=P3^2;

//控制AD采样的端口

sbitDIOLA=P2^5;

//定义LCD锁存器的端口

sbitlcden=P3^4;

//LCD控制端口

sbitlcdrs=P3^5;

sbitdula=P2^6;

sbitwela=P2^7;

voiddelay(uintxms)

{uinti,j,x;

for(x=xms;

i>

0;

i--)

for(j=110;

j>

j