modelsim仿真Word下载.docx

《modelsim仿真Word下载.docx》由会员分享,可在线阅读,更多相关《modelsim仿真Word下载.docx(11页珍藏版)》请在冰豆网上搜索。

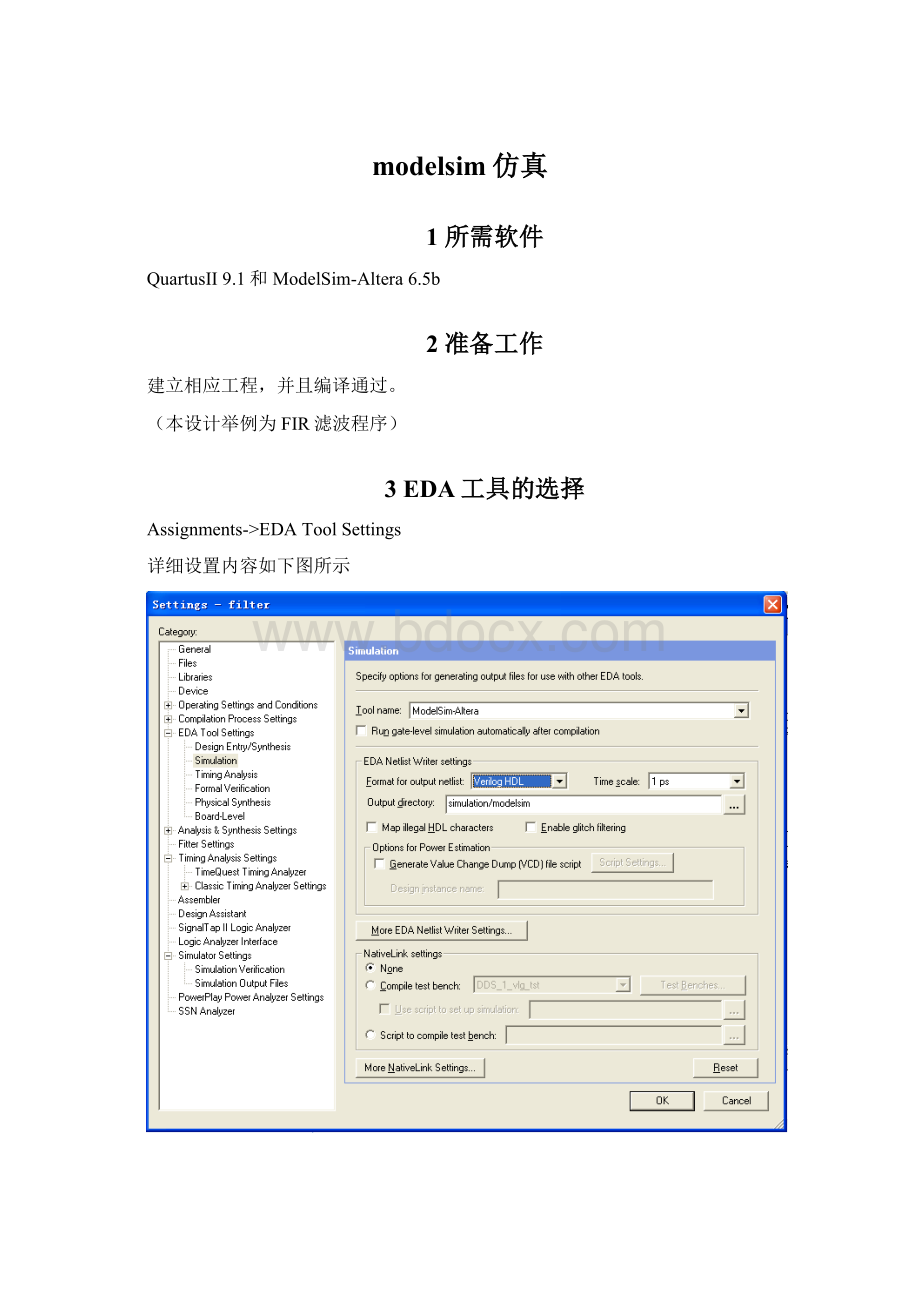

Assignments->

EDAToolSettings

详细设置内容如下图所示

4创建testbench文件

Processing->

Start->

StartTestBenchTemplateWrite

成功后如下图所示,恭喜你,离胜利有近了一步。

打开刚才上面提到的simulation\modelsim文件夹下的DDS_1.vt文件并编辑,内容如下图所示。

`timescale1ns/1ps

moduleDDS_1_vlg_tst();

//constants

//generalpurposeregisters

regeachvec;

//testvectorinputregisters

regCLK_TOP;

//wires

wire[9:

0]Carry_Wave;

wireclken_100k;

wire[31:

0]data;

0]fir_out;

//assignstatements(ifany)

DDS_1i1(

//portmap-connectionbetweenmasterportsandsignals/registers

.Carry_Wave(Carry_Wave),

.CLK_TOP(CLK_TOP),

.clken_100k(clken_100k),

.data(data),

.fir_out(fir_out)

);

initial

begin

//codethatexecutesonlyonce

//insertcodehere-->

begin

CLK_TOP=0;

//-->

end

$display("

Runningtestbench"

end

always

//optionalsensitivitylist

//@(event1orevent2or....eventn)

//codeexecutesforeveryeventonsensitivitylist

#10CLK_TOP=!

CLK_TOP;

//@eachvec;

endmodule

PS:

红色为修改部分。

将该语句//@eachvec;

注释掉,在Modelsim中可以产生连续的波形,否则只有单个波形。

5加入测试文件

在NativeLinksettings中选择Compiletestbench并点击后面的TestBenches

在TestBenches中点击New

在Testbenchname栏一定要填写刚刚我们创建的testbench文件的实体名即moduleDDS_1_vlg_tst()中的DDS_1_vlg_tst;

在Toplevelmodeleintestbench中也填写DDS_1_vlg_tst;

在Designinstancenameintestbench中i1

然后在Testbenchfiles中浏览添加testbench文件,详见下图

设置完成如下图:

Modelsim仿真

点击Run

仿真结果