booth乘法器Word下载.docx

《booth乘法器Word下载.docx》由会员分享,可在线阅读,更多相关《booth乘法器Word下载.docx(20页珍藏版)》请在冰豆网上搜索。

.multiplicand(multiplicand),

.multiplier(multiplier),

.product(product),

.clk(clock),

.reset(reset)

);

endmodule

booth乘法器主程序文件(不压缩)

modulebooth_mul(multiplicand,multiplier,product,clk,reset);

inputclk,reset;

input[BITWIDTH-1:

output[2*BITWIDTH-1:

reg[2*BITWIDTH-1:

reg[15:

0]multiplicand1,multiplier1;

wire[8:

0]ss;

wirea,e0,e1;

wires0,s1,s2,s3,s4,s5,s6,s7,s8;

wire[2*BITWIDTH-1:

0]tmp_prod;

wire[BITWIDTH+3:

0]tp8;

wire[BITWIDTH+5:

0]tp1,tp2,tp3,tp4,tp5,tp6,tp7;

0]j0;

wire[BITWIDTH+2:

0]j1,j2,j3,j4,j5,j6;

wire[BITWIDTH+1:

0]j7;

wire[BITWIDTH:

0]j8;

assigne0=multiplicand[15];

assigne1=multiplier[15];

assigna=e0|e1;

always@(posedgeclkorposedgeresetornegedgeclk)

if(reset)

product<

else

if(a)

if(multiplicand[15])multiplicand1<

=~multiplicand+1'

b1;

elsemultiplicand1<

=multiplicand;

if(multiplier[15])multiplier1<

=~multiplier+1'

elsemultiplier1<

=multiplier;

{multiplicand1,multiplier1}<

={multiplicand,multiplier};

//partialproduct

bfj_9j_9(

.multiplicand1(multiplicand1),

.multiplier1(multiplier1),

.s0(s0),.s1(s1),.s2(s2),.s3(s3),.s4(s4),

.s5(s5),.s6(s6),.s7(s7),.s8(s8),

.j0(j0),.j1(j1),

.j2(j2),.j3(j3),

.j4(j4),.j5(j5),

.j6(j6),.j7(j7),

.j8(j8)

assigntmp_prod=j0000+{j1000[25:

0],6'

b000000}+{s7,1'

b0,s6,1'

b0,s5,1'

b0,s4,1'

b0,s3,1'

b0,s2,1'

b0,s1,1'

b0,s0};

//partialproductaccumulator

assigntp1=j0+{j1,1'

assigntmp_prod[1:

0]=tp1[1:

0];

assigntp2=tp1[BITWIDTH+5:

2]+{j2,1'

b0,s1};

assigntmp_prod[3:

2]=tp2[1:

assigntp3=tp2[BITWIDTH+5:

2]+{j3,1'

b0,s2};

assigntmp_prod[5:

4]=tp3[1:

assigntp4=tp3[BITWIDTH+5:

2]+{j4,1'

b0,s3};

assigntmp_prod[7:

6]=tp4[1:

assigntp5=tp4[BITWIDTH+5:

2]+{j5,1'

b0,s4};

assigntmp_prod[9:

8]=tp5[1:

assigntp6=tp5[BITWIDTH+5:

2]+{j6,1'

b0,s5};

assigntmp_prod[11:

10]=tp6[1:

assigntp7=tp6[BITWIDTH+5:

2]+{j7,1'

b0,s6};

assigntmp_prod[13:

12]=tp7[1:

assigntp8=tp7[BITWIDTH+5:

2]+{j8[BITWIDTH-1],1'

b0,s7};

assigntmp_prod[2*BITWIDTH-1:

14]=tp8[BITWIDTH+1:

always@(posedgeclkorposedgeresetorposedgeclk)

if(reset)product<

elseif(e0^e1)product<

={1'

b1,~tmp_prod[2*BITWIDTH-2:

0]+1'

b1};

elseproduct<

=tmp_prod;

booth乘法器3:

2压缩文件

//3:

2yasuo1:

9->

6

wire[21:

0]j0_s,j1_s;

wire[19:

0]j0_c,j1_c,j2_s;

wire[17:

0]j2_c;

yasuo1y9_6(

.j8(j8),

.j0_s(j0_s),.j0_c(j0_c),

.j1_s(j1_s),.j1_c(j1_c),

.j2_s(j2_s),.j2_c(j2_c)

2yasuo2:

6->

4

wire[23:

0]j00_s,j00_c;

wire[22:

0]j10_s;

0]j10_c;

yasuo2y6_4(

.j00(j0_s),.j01(j0_c),

.j10(j1_s),.j11(j1_c),

.j20(j2_s),.j21(j2_c),

.j00_s(j00_s),.j00_c(j00_c),

.j10_s(j10_s),.j10_c(j10_c)

2yasuo3:

4->

3

wire[28:

0]j20_s;

wire[26:

0]j20_c;

yasuo3y4_3(

.j000(j00_s),.j100(j00_c),

.j200(j10_s),

.j20_s(j20_s),.j20_c(j20_c)

2yasuo4:

3->

2

0]j0000;

0]j1000;

yasuo4y3_2(

.j10(j20_s),

.j20(j20_c),.j30(j10_c),

.j0000(j0000),.j1000(j1000)

加法器

moduleadd3(a,b,c,si,ci);

inputa,b,c;

outputsi,ci;

wiresi,ci;

assignsi=a^b^c;

assignci=a&

b|(a^b)&

c;

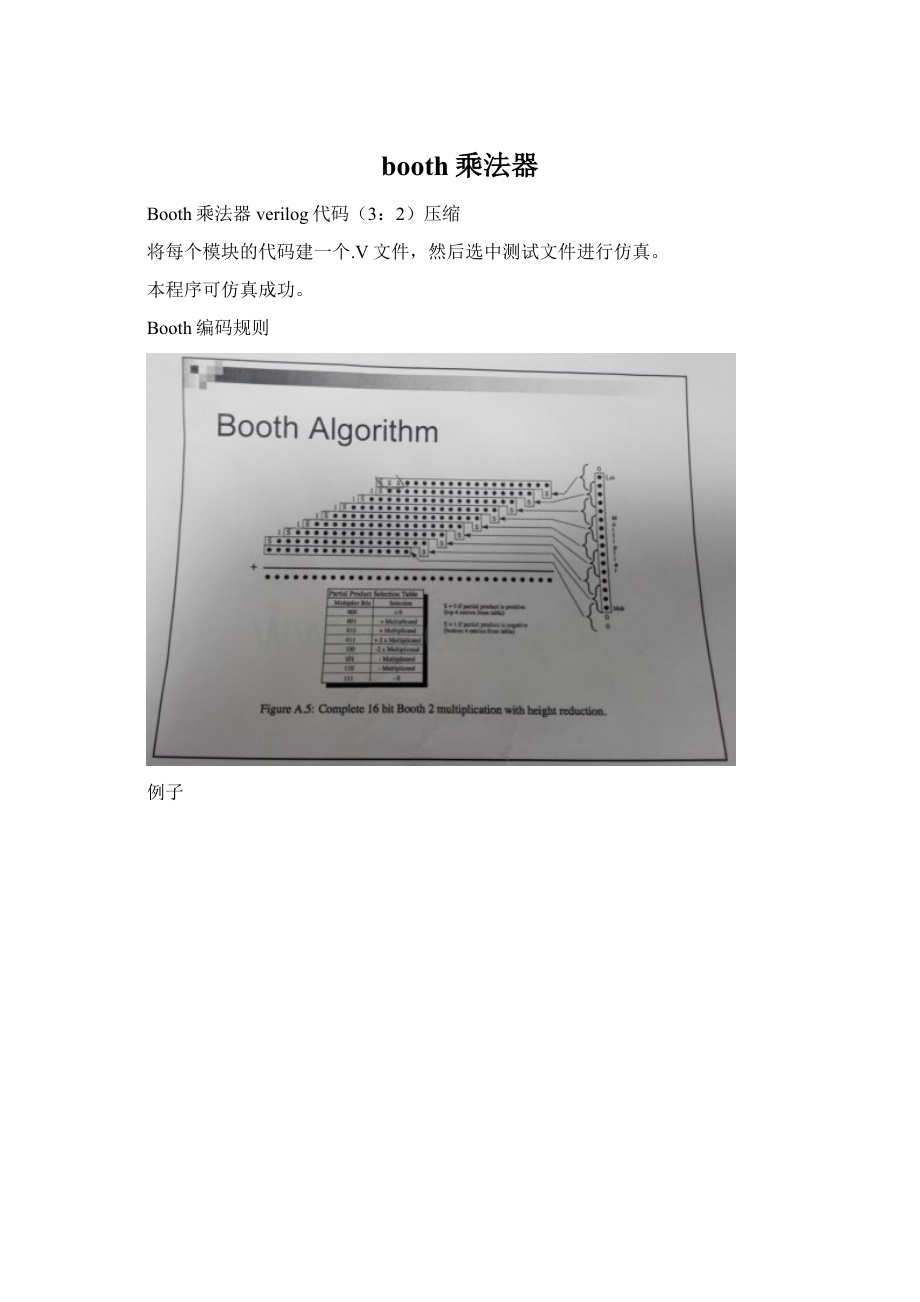

booth编码

modulebooth_recoder(

multiplicand,

code,

pp,

s

input[2:

0]code;

output[BITWIDTH:

0]pp;

outputs;

reg[BITWIDTH:

regs;

always@(multiplicandorcode)

case(code)

3'

b000:

pp={(BITWIDTH+1){1'

b0}};

//+0

b001:

pp={multiplicand[15],multiplicand};

//+M

b010:

b011:

pp={multiplicand,1'

b0};

//+2M

b100:

pp={~multiplicand,1'

//-2M

b101:

pp={~multiplicand[15],(~multiplicand)};

//-M

b110:

b111:

b1}};

//-0

endcase

case(code[2])

1'

b0:

s=1'

b0;

//+0,+M,+2M

b1:

//-2M,-M,-0

booth部分集产生

modulebfj_9(multiplicand1,multiplier1,s0,s1,s2,s3,s4,s5,s6,s7,s8,j0,j1,j2,j3,j4,j5,j6,j7,j8);

0]multiplicand1,multiplier1;

outputs0,s1,s2,s3,s4,s5,s6,s7,s8;

output[BITWIDTH+3:

output[BITWIDTH+2:

output[BITWIDTH+1:

0]pp0,pp1,pp2,pp3,pp4,pp5,pp6,pp7,pp8;

booth_recoder#(BITWIDTH)br0(

.multiplicand(multiplicand1),

.code({multiplier1[1:

0],1'

b0}),

.pp(pp0),

.s(s0)

booth_recoder#(BITWIDTH)br1(

.code(multiplier1[3:

1]),

.pp(pp1),

.s(s1)

booth_recoder#(BITWIDTH)br2(

.code(multiplier1[5:

3]),

.pp(pp2),

.s(s2)

booth_recoder#(BITWIDTH)br3(

.code(multiplier1[7:

5]),

.pp(pp3),

.s(s3)

booth_recoder#(BITWIDTH)br4(

.code(multiplier1[9:

7]),

.pp(pp4),

.s(s4)

booth_recoder#(BITWIDTH)br5(

.code(multiplier1[11:

9]),

.pp(pp5),

.s(s5)

booth_recoder#(BITWIDTH)br6(

.code(multiplier1[13:

11]),

.pp(pp6),

.s(s6)

booth_recoder#(BITWIDTH)br7(

.code(multiplier1[15:

13]),

.pp(pp7),

.s(s7)

booth_recoder#(BITWIDTH)br8(

.code({2'

b00,multiplier1[15]}),

.pp(pp8),

.s(s8)

assignj0={~s0,s0,s0,pp0};

assignj1={1'

b1,~s1,pp1};

assignj2={1'

b1,~s2,pp2};

assignj3={1'

b1,~s3,pp3};

assignj4={1'

b1,~s4,pp4};

assignj5={1'

b1,~s5,pp5};

assignj6={1'

b1,~s6,pp6};

assignj7={~s7,pp7};

assignj8=pp8[15:

子压缩文件

moduleyasuo1(j0,j1,j2,j3,j4,j5,j6,j7,j8,j0_s,j0_c,j1_s,j1_c,j2_s,j2_c);

input[19:

input[18:

input[17:

input[16:

output[21:

output[19:

output[17:

//j0_s,j0_c

assignj0_s[21]=j2[17];

assignj0_s[1]=j0[1];

assignj0_s[0]=j0[0];

assignj0_c[19]=j2[18];

add3a1(.a(1'

b0),.b(j1[18]),.c(j2[16]),.si(j0_s[20]),.ci(j0_c[18]));

add3a2(.a(j0[19]),.b(j1[17]),.c(j2[15]),.si(j0_s[19]),.ci(j0_c[17]));

add3a3(.a(j0[18]),.b(j1[16]),.c(j2[14]),.si(j0_s[18]),.ci(j0_c[16]));

add3a4(.a(j0[17]),.b(j1[15]),.c(j2[13]),.si(j0_s[17]),.ci(j0_c[15]));

add3a5(.a(j0[16]),.b(j1[14]),.c(j2[12]),.si(j0_s[16]),.ci(j0_c[14]));

add3a6(.a(j0[15]),.b(j1[13]),.c(j2[11]),.si(j0_s[15]),.ci(j0_c[13]));

add3a7(.a(j0[14]),.b(j1[12]),.c(j2[10]),.si(j0_s[14]),.ci(j0_c[12]));

add3a8(.a(j0[13]),.b(j1[11]),.c(j2[9]),.si(j0_s[13]),.ci(j0_c[11]));

add3a9(.a(j0[12]),.b(j1[10]),.c(j2[8]),.si(j0_s[12]),.ci(j0_c[10]));

add3a10(.a(j0[11]),.b(j1[9]),.c(j2[7]),.si(j0_s[11]),.ci(j0_c[9]));

add3a11(.a(j0[10]),.b(j1[8]),.c(j2[6]),.si(j0_s[10]),.ci(j0_c[8]));

add3a12(.a(j0[9]),.b(j1[7]),.c(j2[5]),.si(j0_s[9]),.ci(j0_c[7]));

add3a13(.a(j0[8]),.b(j1[6]),.c(j2[4]),.si(j0_s[8]),.ci(j0_c[6]));

add3a14(.a(j0[7]),.b(j1[5]),.c(j2[3]),.si(j0_s[7]),.ci(j0_c[5]));

add3a15(.a(j0[6]),.b(j1[4]),.c(j2[2]),.si(j0_s[6]),.ci(j0_c[4]));

add3a16(.a(j0[5]),.b(j1[3]),.c(j2[1]),.si(j0_s[5]),.ci(j0_c[3]));

add3a17(.a(j0[4]),.b(j1[2]),.c(j2[0]),.si(j0_s[4]),.ci(j0_c[2]));

add3a18(.a(j0[3]),.b(j1[1]),.c(1'

b0),.si(j0_s[3]),.ci(j0_c[1]));

add3a19(.a(j0[2]),.b(j1[0]),