VHDL8位CPU设计包含程序Word格式.docx

《VHDL8位CPU设计包含程序Word格式.docx》由会员分享,可在线阅读,更多相关《VHDL8位CPU设计包含程序Word格式.docx(19页珍藏版)》请在冰豆网上搜索。

ACC-[X]→ACC

JMPGZX

05H

IFACC>

0THENX→PCELSEPC+1→PC

ANDX

06H

ACCand[X]→ACC

ORX

07H

ACCor[X]→ACC

NOTX

08H

Not[X]→ACC

SHIFTRX

09H

SHIFLACCtoRIGHT1bit,LogicShift

SHIFTLX

0AH

SHIFTACCtoLEFT1bit,LogicShift

MPYX

0BH

ACC×

HALT

0CH

HALTAPROGRAM

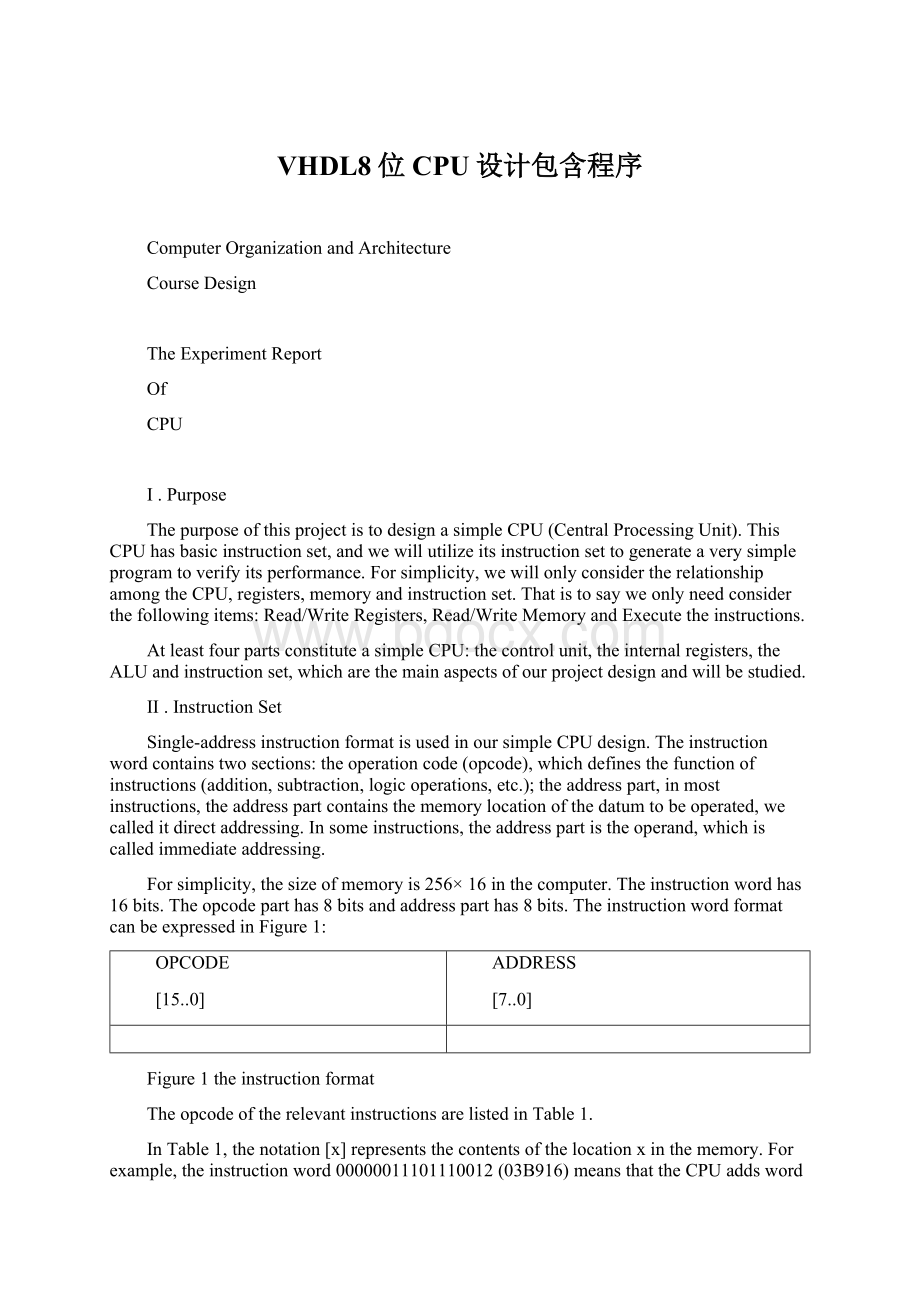

Aprogramisdesignedtotesttheseinstructions:

Calculatethesumofallintegersfrom1to100.

(1),programmingwithClanguage:

sum=0;

temp=100;

loop:

sum=sum+temp;

temp=temp-1;

iftemp>

=0gotoloop;

end

(2),AssumeintheRAM_DQ:

sumisstoredatlocationA4,

tempisstoredatlocationA3,

thecontentsoflocationA0is0,

thecontentsoflocationA1is1,

thecontentsoflocationA2is10010=6416.

WecantranslatetheaboveClanguageprogramwiththeinstructionslistedinTable1intotheinstructionprogramasshowninTable2.

Table2Exampleofaprogramtosumfrom1to100

ProgramwithC

Programwith

instructions

ContentsofRAM_DQinHEX

Address

Contents

LOADA0

00

02A0

STOREA4

01

01A4

temp=100

LOADA2

02

02A2

STOREA3

03

01A3

loop:

LOOP:

LOADA4

04

02A4

ADDA3

05

03A3

06

LOADA3

07

02A3

SUBA1

08

04A1

09

0gotoloop;

JMPGZLOOP

0A

0504

end;

0B

0C00

0C

…

A0

0000

A1

0001

A2

0064

A3

A4

III.InternalRegistersandMemory

MAR(MemoryAddressRegister)

MARcontainsthememorylocationofthewordtobereadfromthememoryorwrittenintothememory.Here,READoperationisdenotedastheCPUreadsfrommemory,andWRITEoperationisdenotedastheCPUwritestomemory.Inourdesign,MARhas8bitstoaccessoneof256addressesofthememory.

MBR(MemoryBufferRegister)

MBRcontainsthevaluetobestoredinmemoryorthelastvaluereadfrommemory.MBRisconnectedtotheaddresslinesofthesystembus.Inourdesign,MBRhas16Bits.

PC(ProgramCounter)

PCkeepstrackoftheinstructionstobeusedintheprogram.Inourdesign,PChas8bits.

IR(InstructionRegister)

IRcontainstheopcodepartofaninstruction.Inourdesign,IRhas8bits.

BR(BufferRegister)

BRisusedasaninputofALU,itholdsotheroperandforALU.Inourdesign,BRhas

16bits.

LPM_RAM_DQ

LPM_RAM_DQisaRAMwithseparateinputandoutputports.Itworksasamemory,anditssizeis256×

16.Althoughit’snotaninternalregisterofCPU,weneedittosimulateandtesttheperformanceofCPU.

LPM_ROM

LPM_ROMisaROMwithoneaddressinputportandonedataoutputport,anditssizeofdatais32bitswhichcontainscontrolsignalstoexecutemicro-operations.

IV.ALU

ALU(ArithmeticLogicUnit)isacalculationunitwhichaccomplishesbasicarithmeticandlogicoperations.Inourdesign,someoperationsmustbesupportedwhicharelistedasfollows:

Table3ALUOperations

ALUcontrolsignal

Operations

Explanations

3H

ADD

ACC←ACC+BR

4H

SUB

ACC←ACC-BR

6H

AND

ACC←ACCandBR

7H

OR

ACC←ACCorBR

8H

NOT

ACC←notACC

9H

SHIFTR

ACC←ShiftACCtoRight1bit

SHIFTL

ACC←ShiftACCtoLeft1bit

V.Micro-programmedControlUnit

IntheMicroprogrammedcontrol,themicroprogramconsistsofsomemicroinstructionandthemicroprogramisstoredincontrolmemorythatgeneratesallthecontrolsignalsrequiredtoexecutetheinstructionsetcorrectly.Themicroinstructioncontainssomemicro-operationswhichareexecutedatthesametime.

Figure2showsthekeyelementsofsuchanimplementation.

Thesetofmicroinstructionsisstoredinthecontrolmemory.Thecontroladdressregistercontainstheaddressofthenextmicroinstructionstoberead.Whenamicroinstructionisreadfromthecontrolmemory,itistransferredtoacontrolbufferregister.Theregisterconnectstothecontrollinesemanatingfromthecontrolunit.Thus,readingamicroinstructionfromthecontrolmemoryisthesameasexecutingthatmicroinstruction.Thethirdelementshowninthefigureisasequencingunitthatloadsthecontroladdressregisterandissuesareadcommand.

Figure2ControlUnitMicro-architecture

(I)Totalcontrolsignalsforinstructionsarelistedasfollows:

Table4Controlsignalsforthemicro-operations

BitsinControlMemory

Micro-operation

Meaning

C0~C7

/

BranchAddresses

C8

PC←0

ClearPC

C9

PC←PC+1

IncrementPC

C10

PC←MBR[7..0]

MBR[7..0]toPC

C11

ACC←0

ClearACC

C12--C15

ALUCONTROL

ControloperationsofALU

C16

R

ReaddatafromMemorytoMBR

C17

W

WritedatatoMemory

C18

MAR←MBR[7..0]

MBR[7..0]toMARasaddress

C19

MAR←PC

PCvaluetoMAR

C20

MBR←ACC

ACCvaluetoMBR

C21

IR←MBR[15..8]

MBR[15..8]toIRasopcode

C22

BR←MBR

CopyMBRtoBR

C23

CAR←CAR+1

IncrementCAR

C24

CAR←C0~C7

C7~C0toCAR

C25

CAR←OPCODE+CAR

AddOPtoCAR

C26

CAR←0

ResetCAR

C27--C31

Notuse

-----------

(II)Thecontentsinrom.mifandthecorrespondingmicroprogramsarelistedasfollows:

0:

00810000;

R←1,CAR←CAR+1

1:

00A00000;

OP←MBR[15..8],CAR←CAR+1

2:

02000000;

CAR←CAR+OP

3:

01000014;

CAR←14H

4:

01000019;

CAR←19H

5:

0100001E;

CAR←1EH

6:

01000023;

CAR←23H

7:

01000041;

CAR←41H

8:

01000028;

CAR←28H

9:

0100002D;

CAR←2DH

a:

01000032;

CAR←32H

b:

01000037;

CAR←37H

c:

0100003C;

CAR←3CH

d:

01000046;

CAR←46H

e:

0100004B;

CAR←4H

f:

00000000;

………

14:

00840000;

MAR←MBR[7..0],CAR←CAR+1------STORE

15:

00920200;

MBR←ACC,PC←PC+1,W←1,CAR←CAR+1

16:

04080000;

CAR←0

17:

18:

19:

MAR←MBR[7..0],CAR←CAR+1------LOAD

1a:

00810A00;

PC←PC+1,R←1,ACC←0,CAR←CAR+1

1b:

00C03000;

BR←MBR,ACC←ACC+BR,CAR←CAR+1

1c:

1d:

1e:

MAR←MBR[7..0],CAR←CAR+1----------ADD

1f:

00810200;

PC←PC+1,R←1,CAR←CAR+1

20:

21:

22:

23:

MAR←MBR[7..0],CAR←CAR+1----------SUB

24:

25:

00C04000;

BR←MBR,ACC←ACC-BR,CAR←CAR+1

26:

27:

28:

MAR←MBR[7..0],CAR←CAR+1---------AND

29:

2a:

00C06000;

BR←MBR,ACC←ACCANDBR,CAR←CAR+1

2b:

2c:

2d:

MAR←MBR[7..0],CAR←CAR+1---------OR

2e:

2f:

00C07000;

BR←MBR,ACC←ACCORBR,CAR←CAR+1

30:

31:

32:

MAR←MBR[7..0],CAR←CAR+1----------NOT

33:

00808200;

PC←PC+1,ACC←NOTACC,CAR←CAR+1

34:

35:

36:

37:

MAR←MBR[7..0],CAR←CAR+1----------SHIFTR

38:

08092000;

PC←PC+1,ACC←SHIFTACCtoRight1bit,CAR←CAR+1

39:

3a:

3b:

3c:

MAR←MBR[7..0],CAR←CAR+1-----------SHIFTL

3d:

0080A200;

PC←PC+1,ACC←SHIFTACCtoLeft1bit,CAR←CAR+1

3e:

3f:

40:

41:

MAR←MBR[7..0],CAR←CAR+1-----------JMPGEZ

42:

00805000;

CAR←CAR+1,

43:

44:

45:

46:

MAR←MBR[7..0],CAR←CAR+1------------MPY

47:

48:

00C0B000;

BR←MBR,ACC←ACC*BR,CAR←CAR+1

49:

4a:

4b:

CAR←4BH------------------------------HALT

4c:

(III)Thesimulationwaveformsofsomeoperates

1,load,add,store,halt(22+10)

ThecontentsinRAM:

0:

022A;

Load2A

032B;

ADD2B

012C;

Store2C

0C00;

Halt

2a:

0016;

2b:

0