DDR与DDRII深刻理解Word文档下载推荐.docx

《DDR与DDRII深刻理解Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《DDR与DDRII深刻理解Word文档下载推荐.docx(24页珍藏版)》请在冰豆网上搜索。

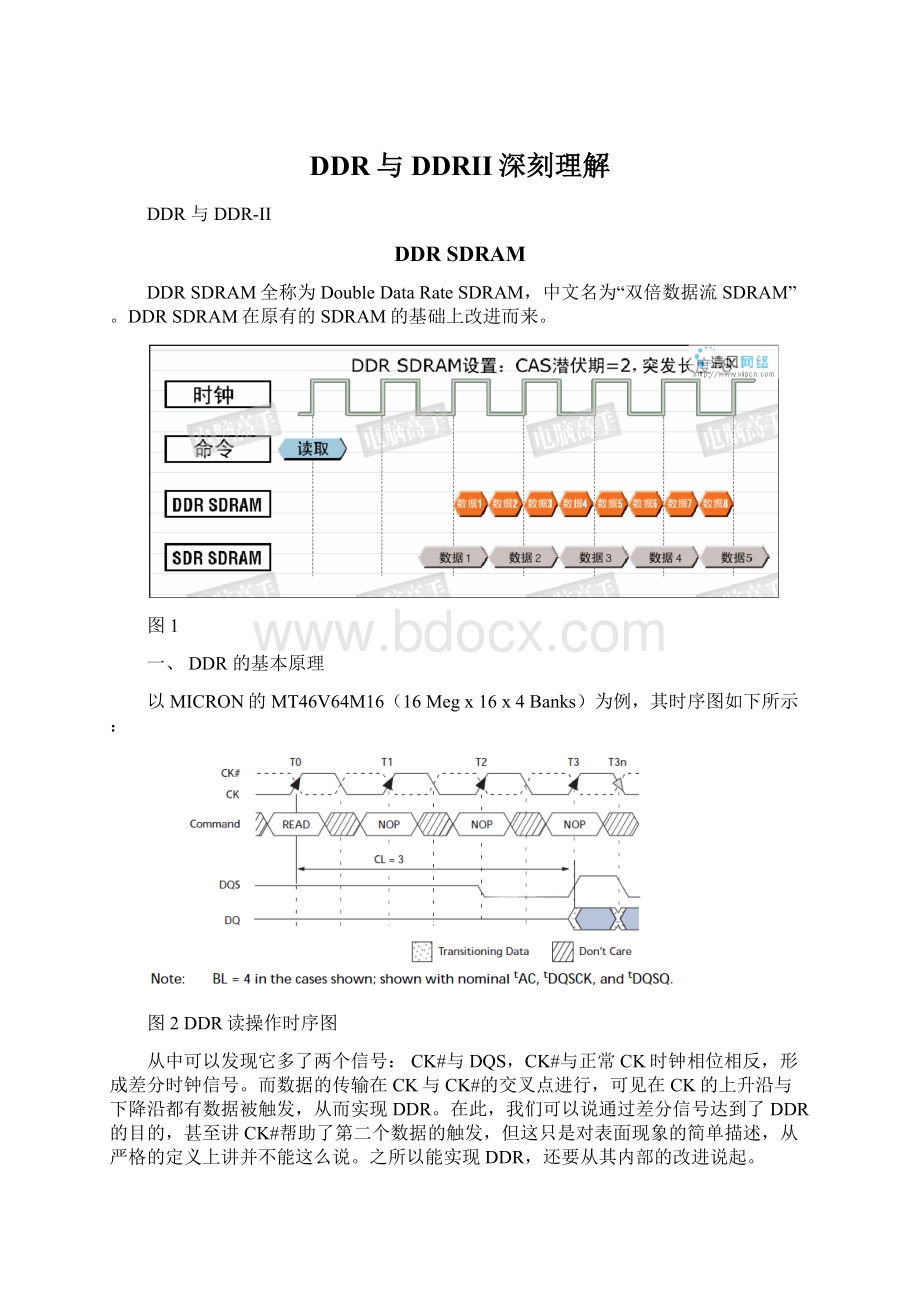

图4差分时钟

2.数据选通脉冲DQS

DQS是DDR中的重要功能,主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。

DQS是双向信号,在写入时用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。

可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。

而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。

注意,这与SDRAM中的tAC的不同。

实际上,DQS生成时,芯片内部的预取已经完毕了,tAC是指上文结构图中红色框图部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

由于是并行传输,DDR内存对tAC也有一定的要求,以本芯片为例,若采用DDR266,tAC的允许范围是±

0.75ns;

若采用DDR333,则是±

0.7ns,有关它们的时序图示见前文,其中CL里包含了一段DQS的导入期。

DQS是了保证接收方的选择数据,DQS在读取时与数据同步传输。

但由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是要有一个tAC规定的原因。

而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。

这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。

这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,如图5所示;

但数据的读取触发仍为DQS的上/下沿,如图6所示。

图5数据写入时序图

图6数据读取时序图

3.写入延时

在上面的DQS写入时序图(图5)中可以发现,在发出写入命令后,DQS与写入数据要等一段时间才会送达。

这个周期被称为DQS相对于写入命令的延迟时间(tDQSS)。

tDQSS是DDR内存写入操作的一个重要参数,太短的话恐怕接受有误,太长则会造成总线空闲。

tDQSS最短不能小于0.75个时钟周期,最长不能超过1.25个时钟周期。

正常情况下,tDQSS是一个时钟周期,但写入时接受方的时钟只用来控制命令信号的同步,而数据的接受则完全依靠DQS进行同步,所以DQS与时钟不同步也无所谓。

4.突发长度与写入掩码

在DDRSDRAM中,突发长度只有2、4、8三种选择,没有了随机存取的操作(突发长度为1)和全页式突发。

因为L-Bank一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输。

但是,突发长度的定义也与SDRAM的不一样了(见图1),它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。

对于突发写入,如果其中有不想存入的数据,仍可以运用DM信号进行屏蔽。

DM信号和数据信号同时发出,接收方在DQS的上升与下降沿来判断DM的状态,如果DM为高电平,那么之前从DQS中部选取的数据就被屏蔽了。

5.延迟锁定回路(DLL)

DDRSDRAM对时钟的精确性有着很高的要求,而DDRSDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDRSDRAM这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM也内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

DDRSDRAM的tAC(data-outtransitionskewtoCK)就是因为内部时钟与外部时钟有偏差而引起的,它很可能造成因数据不同步而产生错误的恶果。

实际上,不同步就是一种正/负延迟,如果延迟不可避免,那么若是设定一个延迟值,如一个时钟周期,那么内外时钟的上升与下降沿还是同步的。

鉴于外部时钟周期也不会绝对统一,所以需要根据外部时钟动态修正内部时钟的延迟来实现与外部时钟的同步,这就是DLL的任务。

DLL不同于主板上的PLL,它不涉及频率与电压转换,而是生成一个延迟量给内部时钟。

目前DLL有两种实现方法,一个是时钟频率测量法(CFM,ClockFrequencyMeasurement),一个是时钟比较法(CC,ClockComparator)。

CFM是测量外部时钟的频率周期,然后以此周期为延迟值控制内部时钟,这样内外时钟正好就相差了一个时钟周期,从而实现同步。

DLL就这样反复测量反复控制延迟值,使内部时钟与外部时钟保持同步。

CC的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到下一个内部时钟周期里,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延迟从下一个内部时钟中刨除,如此往复,最终使内外时钟同步。

图7

DDR-IISDRAM

DDR-Ⅱ相对于DDR的主要改进如下:

DDRSDAMR

DDRIISDRAM

时钟频率

100/133/166/200MHz

200/266/333MHz

数据传输率

200/266/333/400MBPS

400/533/667MBPS

工作电压

2.5V

1.8V/1.5V/1.35V

预取设计

2Bit

4Bit

突发长度

2/4/8

4/8

L-BANK数量

最多4个

最多8个

CL值

1.5、2.5、3.5、3

3~11

AL值

无

0~CL-1

接口标准

SSTL_2

SSTL_18

系统最高P-BANK数量

8

4

新增特性

COD、ODT、POSTEDCAS

一、DDR-Ⅱ内存结构

DDR-IISDRAM内存结构图如下所示:

图8DDR-IISDRAM内存结构图

SDRAM有两个时钟,一个是内部时钟,一个是外部时钟。

在SDRAM与DDR时代,这两个时钟频率是相同的,而在DDR-II中,核心频率和时钟频率已经不一样了,由于DDR-II采用了4bitPrefetch技术。

Prefetch可以意译为"

数据预取"

技术,可以认为是端口数据传输率和内存Cell之间数据读/写之间的倍率,如DDR为2bitPrefetch,因此DDR的数据传输率是核心Cell工作频率的2倍。

DDR-II采用了4bitPrefetch架构,也就是它的数据传输率是核心工作频率的4倍。

实际上数据先输入到I/O缓冲寄存器,再从I/O寄存器输出。

DDR-II400的核心频率/时钟频率/数据传输率分别是100MHz/200MHz/400Mbps。

DDR-II400的核心频率和DDR200是一样的,但是DDR-II400的数据传输率是DDR200的2倍。

因此,DDR-Ⅱ虽然实现了4-bit预取,但在实际效能上,与DDR是一样的。

因此在相同的核心频率下,DDR-Ⅱ达到了2倍于DDR的的带宽的水平有一个前提条件,那就是DDR-Ⅱ的外部时钟频率也是DDR的2倍。

图9时钟频率示意图

如前文所述,DDR在写入数据时,以DQS的高/低电平期中部为数据周期分割点;

但在数据的读取触发仍为DQS的上/下沿。

为保证DQS信号的准确,在DDR-II中,增加了差分DQS信号。

图10CK与CK#、DQS与DQS#

二、DDR-Ⅱ的新操作与新时序设计

1.OCD(Off-ChipDriver,片外驱动调校)

DDR-II加入了可选的OCD功能,OCD的主要用意在于调整I/O接口端的电压,来补偿上拉与下拉电阻值,从而可以提高信号的完整性。

调校期间,分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ高电平的同步情况。

如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级,从而减少DQ、DQS的倾斜来提高信号的完整性及控制电压来提高信号品质。

不过,由于在一般情况下对应用环境稳定程度要求并不太高,只要存在差分DQS时就基本可以保证同步的准确性,因此OCD功能在普通台式机上并没有什么作用,其优点主要体现在服务器领域。

图11OCD

2.ODT(On-DieTermination,片内终结)

所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后面信号的影响。

在进入DDR时代,DDR内存对工作环境提出更高的要求,如果先前发出的信号不能被电路终端完全吸收掉而在电路上形成反射现象,就会对后面信号的影响从而造成运算出错。

因此目前支持DDR主板都是通过采用终结电阻来解决这个问题。

由于每根数据线至少需要一个终结电阻,这意味着每块DDR主板需要大量的终结电阻,这也无形中增加了主板的生产成本,而且由于不同的内存模组对终结电阻的要求不可能完全一样,也造成了所谓的“内存兼容性问题”。

而在DDR-II中加入了ODT功能,即是将终结电阻设于内存芯片内(参见图8红色方框部分),当在DRAM模组工作时把终结电阻器关掉,而对于不工作的DRAM模组则进行终结操作,起到减少信号反射的作用(注:

ODT的功能与禁止由北桥芯片控制,在开机进行EMRS时进行设置,ODT所终结的信号包括DQS、DQS#、DQ等等。

),这样可以产生更干净的信号品质,从而产生更高的内存时钟频率速度。

而将终结电阻设计在内存芯片之上还可以简化了主板的设计,降低了主板的成本,而且终结电阻器可以和内存颗粒的“特性”相符,从而减少内存与主板的兼容问题的出现。

图12ODT

3.PostedCAS、附加潜伏期与写入潜伏期

前置CAS(PostedCAS)是为了解决DDR内存中指令冲突,提高DDR-II内存的利用效率而设计的功能。

它允许CAS信号紧随RAS发送,相对于以往的DDR等于将CAS前置了。

这样,地址线可以立刻空出来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生,但读/写操作并没有因此而提前,仍有要保证有足够的延迟/潜伏期,为被定义为读取潜伏期(RL,ReadLatency),见图13。

相应的,DDR-Ⅱ还对写入潜伏期(WL,WriteLatency)制定了标准,WL是指从写入命令发出到第一笔数据输入的潜伏期,见图14。

图13RL示意图

图14WL示意图

图14

在没有前置CAS功能时,对其他L-Bank的寻址操作可能会因当前行的CAS命令占用地址线而延后,并使数据I/O总线出现空闲,当使用前置CAS后,消除了命令冲突并使数据I/O总线的利率提高。

设置PostedCAS后,必须附加潜伏期以保证应有延迟,此时读取潜伏期(RL)就等于AL+CL。

DDR-Ⅱ中CL最低值为3,最高为11,并且不再有x.5的设计,而AL值则为0,CL-1,CL-2。

当AL设为0时,前置CAS无效,即为传统DDR模式的操作。

PostedCAS其本质就是将CAS信号的使能时间段(即RDAP命令)直接插入到紧跟RAS信号的使能时间段(即ACT命令)之后,虽然读和写操作并没有得到提前,总的延迟时间也没有发生改变,但引入这种技术后,可以避免在多Bank操作中的一个Bank的CAS信号和其他Bank的RAS信号发生冲突,从而提高了存储芯片的使用效率。

二、DDR的测试

EDEC(电子工程设计发展联合协会)已经明确规定存储设备详细测试要求,需要对抖动、定时和电气信号质量进行验证。

测试参数:

如时钟抖动、建立和保持时间、信号的过冲、信号的下冲、过渡电压等列入了JEDEC为存储器技术制定的测试规范。

三、DDR

DQS信号的处理

摘要

现在不论做主板设计或测试的工程师,还是做内存或DDR芯片设计或测试的工程师都会面临这样一个问题:

如何能够分离出“读”和“写”眼图以发现有无信号品质问题?

因为简单测试一段波形很难确定你的设计或产品是否满足规范要求。

而因为DDR的数据总线信号存在三态,“读”时序和“写”时序不同的情况,我们很难直接用示波器把“读”眼图和“写”眼图分离出来。

本文根据自己设计的DDR“读”“写”分离软件,介绍一种把“读”眼图和“写”眼图分离开的方法,并创新地引入模板测试的方法。

DDR

1&

2&

3总线概览

DDR全名为Double

Data

Rate

SDRAM

,简称为DDR。

现在DDR技术已经发展到了DDR

3,理论上速度可以支持到1600MT/s。

DDR总线走线数量多,速度快,操作复杂,探测困难,给测试和分析带来了巨大的挑战。

DDR本质上不需要提高时钟频率就能加倍提高SDRAM的速度,它允许在时钟的上升沿和下降沿读出数据,因而其速度是标准SDRAM的两倍。

至于地址与控制信号则与传统SDRAM相同,仍在时钟上升沿进行数据判断。

目前,许多计算机使用时钟频率为533MHz的DDR2内存,更先进的DDR2内存正在日益普及,它的时钟频率在400

MHz-800

MHz之间,新的DDR3内存的时钟频率则可以工作在800MHz-16OOMHz之间。

DDR3内存芯片还有另外一个长处:

更低的能耗,它的运行电压是1.5伏,低于DDR2内存芯片的1.8伏和DDR1内存芯片的2.5伏。

在使用电池的设备中能够延长电池续航时间,因为能耗低,产生的热量也就少,从而对冷却的要求也就低一些。

3几个新增特性的含义是:

ODT(

On

Die

Termination),DDR1

匹配放在主板上,DDR2&

3把匹配直接设计到DRAM芯片内部,用来改善信号品质。

OCD(Off

Chip

Driver)是加强上下拉驱动的控制功能,通过减小DQS与/DQS(DQS是数据Strobe,源同步时钟,数据的1和0由DQS作为时钟来判断)

Skew(时滞)来增加信号的时序容限(Timing

Margin)。

Posted

CAS是提高总线利用率的一种方法。

AL(Additive

Latency)技术是相对于外部CAS,内部CAS执行一定的延时。

图1是DDR总线的体系结构。

其中DQS是源同步时钟,在接收端使用DQS来读出相应的数据DQ,上升沿和下降沿都有效。

DDR1总线,DQS是单端信号,而DDR2&

3,

DQS则是差分信号。

DQS和DQ都是三态信号,在PCB走线上双向传输,读操作时,DQS信号的边沿在时序上与DQ的信号边沿处对齐,而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐,参考图2,这就给测试验证带来了巨大的挑战:

把“读”信号与“写”信号分开是非常困难的!

图2中,Addr/Cmd

Bus意思是地址/命令总线,都是时钟的上升沿有效,其中命令由:

/CS(片选),/RAS,

/CAS,/WE(写使能)决定,比如:

“读”命令为:

LHLH,“写”命令为:

LHLL等。

操作命令很多,主要是NOP(空超作),Active(激活),Write,Read,Precharge

(Bank关闭),Auto

Refresh或Self

Refresh(自动刷新或自刷新)等(细节请参考:

Jedec规范JESD79)。

Bus是数据总线,由DQS的上升沿和下降沿判断数据DQ的0与1。

3总线的信号完整性测试

DDR总线PCB走线多,速度快,操作时序复杂,很容易出现失效问题,为此我们经常用示波器进行DDR总线的信号完整性测试和分析,通常的测试内容包括:

1,命令信号的波形和时序参数:

需要测试/RAS,/CAS,/WE,/CS的信号品质,如Vmax(最大电压值),Vmin(最小电压值),Slew

Rate(斜率),Ringback(回沟)等;

还需要测试相对于时钟边沿的Setup

Time(建立时间)和Hold

Time(保持时间)。

测试相对于时钟边沿的建立时间和保持时间时,需要注意参考电平的位置和最差情况波形的捕获。

如图3的/CS建立时间和保持时间的测试就没有测试出最差的建立时间和保持时间值,为此,我们需要用眼图累积的方式设法找到最差情况下的建立时间和保持时间。

2,地址信号的波形和时序参数:

测试内容和测试方质和相对于时钟边沿的建立时间和保持时间的测试。

3,时钟信号的波形和抖动参数:

测试建议用差分探头。

波形参数包括overshoot(过冲),undershoot(下冲),Slew

Rate(斜率)或Rise

Time(上升时间)和Fall

Time(下降时间),高低时间和Duty

Cycle(占空比失真)等。

时钟抖动一般只是测试Cycle-Cycle

Jitter(周期到周期抖动),但是当速率超过533MT/s的DDR2&

3时,则测试内容相当多,不可忽略,下表1是DDR2

667的规范参数。

这些抖动参数的测试需要用专用软件实现,比如Agilent的N5413A

DDR2时钟表征工具。

4,速据信号的波形和时序参数:

DQS(源同步时钟)和DQ(数据)波形参数与命令地址测试类似,测试起来比较简单,但是探测却比较复杂和困难。

DDR1,DQS是单端信号,可以用单端探头测试,DDR2&

3

DQS则是差分信号,建议用差分探头测试,减小探测难度。

DQS和DQ的时序关系,即相对的在不同操作条件下的建立时间和保持时间关系则非常复杂,分析比较困难,图4是实际捕获的DDR2

533

DQS和DQ的波形。

从图中可以看出DQS和DQ的三态(Tri-state)特征,读数据(Read

Burst)和写数据(Write

Burst)的DQS和DQ的相对时序特征。

在我们测试时,只是捕获了这样的波形,然后测试出在“读”“写”操作时的建立时间和保持时间参数是不够的,因为数据码型是变化的,猝发长度也是变化的,只测了几个时序参数很难覆盖各种情况,更难测出最差情况。

很多工程师花了一周去测试DDR,仍然测不出问题的关键点就在此处。

因此我们应该用眼图的方式去测试DDR的读写时序,确保反映整体时序情况和捕获最差情况下的波形,最好能够套用串行数据的分析方法,调用模板帮助判断。

“读”“写”眼图测试

基于DDR“读”“写”信号相位不同的特征,本人设计了一个软件进行“读”“写”眼图的测试分析,软件使用VEE

Pro

7.5设计界面,使用VEE

Pro内嵌的Matlab脚本分析数据,基于规范的AC参数设计模板,帮助工程师进行DDR信号完整性测试分析的最复杂部分即“读”

“写”数据眼图的测试分析。

图5是软件界面和分析结果的一个示例,上面两福图形是用户界面。

左边的是离线分析软件,用示波器同时采集DQS和DQ信号,并且存为*.CSV文件。

采集时,采样率设置为20GSa/s,存储深度设置为200k以上,确保捕获足够的数据,同时被测系统运行大型的软件或MemoryTest.exe工具(此内存测试软件能够进行内存总线的加压测试,一般做系统设计的或内存设计的都有),以让总线上有足够多的数据,来增加捕获各种码型和最差情况的可能性。

离线软件调用采集的波形,自动去掉三态数据,把“读”数据放在一起,把“写”数据放在一起,基于DQS的有效边沿(去掉预调整和后调整后的上升边沿和下降边沿),累积在一起形成眼图,调用模板判断信号的优劣和是否满足规范要求。

图5右上图是基于Agilent的DSO80000和54850系列示波器的在线实时分析软件界面。

需要把软件安装在示波器内部,或安装在外部电脑上用LAN或GPIB到USB适配器(82357A)连接到示波器。

示波器的通道1探测DQS,通道3探测DQ,被测系统上运行大型的软件或MemoryTest.exe工具。

在在线软件上输入想重复捕获波形的次数,然后按“starting”进行实时数据的捕获和实时眼图的分析,软件会控制示波器捕获波形,然后分析数据,形成眼图,调用模板判断信号是否满足规范要求,然后重复下一次捕获和分析,同时把新捕获的波形累积到前面捕获的波形上面。

在线软件执行的算法与离线软件类似,只是可以自动控制示波器,进行波形的多次捕获和分析,并同时把实时捕获的波形的分析结果连同以前的结果一同显示出来。

图5下面的两个波形是实际的分析结果示例,分析的是DDR2

667,测试点是在DIMM内存条上。

对我们比较有意义的是左边的“写”眼图,它反映的是信号从北桥发出,通过主板较长距离传输到达DRAM接收芯片的波形,这是我们做系统设计和测试时需要得到的眼图。

右图则是直接从DRAM芯片发出的信号的波形,因为测试点是在DIMM上,所以对我们只有参考价值:

当在北桥测试出时序问题时,通过此波形的观察确定是主板设计的问题,还是DIMM或DRAM芯片本身的问题。

如果测试点在北桥,则我们需要关注“读”眼图,而此时“写”眼图一般只有参考价值。

这个DDR“读”“写”眼图分析软件的算法是什么呢?

其实很简单,如图6所示,如果直接用DQS触发DQ,则会形成比较乱的眼图,但是中间又包括需要的信息,如图中的红色圆圈周围的是“写”眼