最新CD4094位移位存储总线寄存器Word文件下载.docx

《最新CD4094位移位存储总线寄存器Word文件下载.docx》由会员分享,可在线阅读,更多相关《最新CD4094位移位存储总线寄存器Word文件下载.docx(13页珍藏版)》请在冰豆网上搜索。

QS

↑

X

三态

Q7

不变

↓

1

QN-1

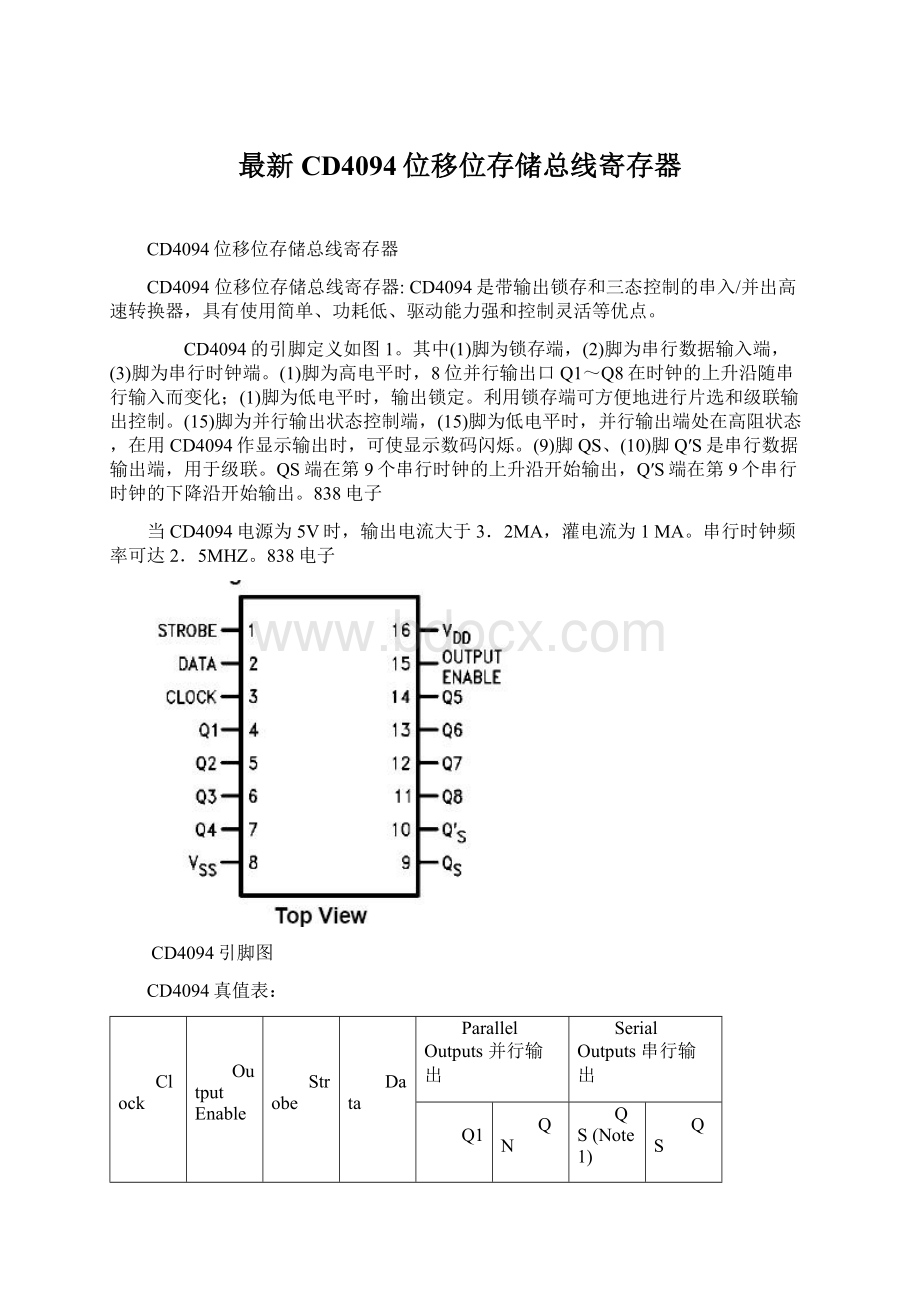

CD4094内部电路方框图

AbsoluteMaximumRatings绝对最大额定值:

SupplyVoltage电源电压(VDD)

-0.5to+18VDC

InputVoltage输入电压(VIN)838电子

-0.5toVDD+0.5VDC

StorageTemperatureRange储存温度范围(TS)

-65℃to+150℃

PowerDissipation功耗(PD)

Dual-In-Line普通双列封装新艺图库

700mW

SmallOutline小外形封装

500mW

LeadTemperature焊接温度(TL)

Soldering,10seconds)(焊接10秒)

260℃

RecommendedOperatingConditions建议操作条件:

DCSupplyVoltage直流供电电压(VDD)

+3.0to+15VDC

0toVDDVDC

OperatingTemperatureRange工作温度范围(TA)

-40℃to+85℃

DCElectricalCharacteristics直流电气特性:

Symbol符号

Parameter参数

Conditions条件

-40°

C

+25°

+85°

Units单位

最小

最大

典型

IDD

QuiescentDeviceCurrent静态电流

VDD=5.0V

20

150

μA

VDD=10V

40

300

VDD=15V

80

600

VOL

LOWLevelOutputVoltage输出低电平电压

VDD=5.0V

|IO|≤1.μA

0.05

V

VDD=10V

VDD=15V

VOH

HIGHLevelOutputVoltage输出高电平电压

|IO|≤1μA

4.95

5.0

9.95

10.0

14.95

15.0

VIL

LOWLevelInputVoltage输入低电平电压

VDD=5.0V,VO=0.5Vor4.5V

1.5

VDD=10V,VO=1.0Vor9.0V

3.0

VDD=15V,VO=1.5Vor13.5V

838电子

4.0

VIH

HIGHLevelInputVoltage输入高电平电压

3.5

7.0

11.0

IOL

LOWLevelOutputCurrent输出低电平电流(Note4)

VDD=5.0V,VO=0.4V

0.52

0.44

0.88

0.36

mA

VDD=10V,VO=0.5V

1.3

1.1

2.25

0.9

VDD=15V,VO=1.5V

3.6

8.8

2.4

IOH

HIGHLevelOutputCurrent输出高电平电流(Note4)

VDD=5.0V,VO=4.6V

-0.52

-0.44

-0.36

VDD=10V,VO=9.5V

-1.3

-1.1

-0.9

VDD=15V,VO=13.5V

-3.6

-3.0

-2.4

IIN

InputCurrent输入电流

VDD=15V,VIN=0V

-0.3

-1.0

μA

VDD=15V,VIN=15V

0.3

1.0

IOZ

3-STATEOutputLeakageCurrent3态输出漏电流

VDD=15V,VIN=0Vor15V

10

ACElectricalCharacteristics交流电气特性:

Symbol符号

Parameter参数838电子

tPHL,tPLH

PropagationDelayClocktoQS

ns

125

250

95

190

PropagationDelayClocktoQ¢

S

VDD=5.0V

230

460

110

220

75

PropagationDelayClocktoParallelOut

420

840

195

390

135

270

PropagationDelayStrobetoParallelOut

290

580

145

100

200

tPHZ

PropagationDelayHIGHLeveltoHIGHImpedance

140

280

55

tPLZ

PropagationDelayLOWLeveltoHIGHImpedance

tPZH

PropagationDelayHIGHImpedancetoHIGHLevel

tPZL

PropagationDelayHIGHImpedancetoLOWLevel

tTHL,tTLH

TransitionTime过渡时间

50

tSU

Set-UpTimeDatatoClock建立时间数据时钟

tr,tf

MaximumClockRiseandFallTime最大时钟上升和下降时间

ms

tPC

MinimumClockPulseWidth最小时钟脉冲宽度

83

tPS

MinimumStrobePulseWidth

ns

70

35

fmax

MaximumClockFrequency最大时钟频率

MHz

6.0

8.0

CIN

InputCapacitance输入电容

AnyInput

7.5

pF

测试电路和3态时序图

时序图

3.串入/并入-串出移位寄存器CD4014、CD4021CD4014是8位移位寄存器。

图4是其逻辑图和引脚功能图。

CD4014有一公共的时钟输入端CP、一个并入/串入控制端P/S、一个串行数据输入端DS和8个并行数据输入端P1~P8、另外还有3个输出端Q6、Q7、Q8。

表3

CP

DS

Cr

Q0

Q2

Q3

保持

Q0n

Q1n

Q2n

表4

P/S

P1

Pn

Qn

Qn-1

表5

表4是CD4014的真值表。

并行或串行输入数据,是在P/S端控制下,随时钟的上升沿同步地输入寄存器。

当P/S为“0”时,串行输入数据随时钟的上升沿同步地送入寄存器中;

当P/S为“1”时,加在并行输入P1~P3的数据与时钟的上升沿同步地送入寄存器。

CD4014可以很方便地扩展位数,因此使用N个CD4014,就可将寄存器位数扩展为8×

N位。

54/7402

四2输入或非门(OC)

简要说明

02为四组2输入端或非门(正逻辑),共有54/7402、54/74S02、54/74LS02三种线路结构型式,其主要电特性的典型值如下:

型号

tPLH

tphl

PD

12ns

8ns

85mW

54/74S02

3.6ns

3.5ns

108mW

54/74LS02

10ns

11mW

引出端符号

1A-4A输入端

1B-4B输入端

1Y-4Y输出端