完整版基于EDA四位智能竞赛抢答器Word格式.docx

《完整版基于EDA四位智能竞赛抢答器Word格式.docx》由会员分享,可在线阅读,更多相关《完整版基于EDA四位智能竞赛抢答器Word格式.docx(12页珍藏版)》请在冰豆网上搜索。

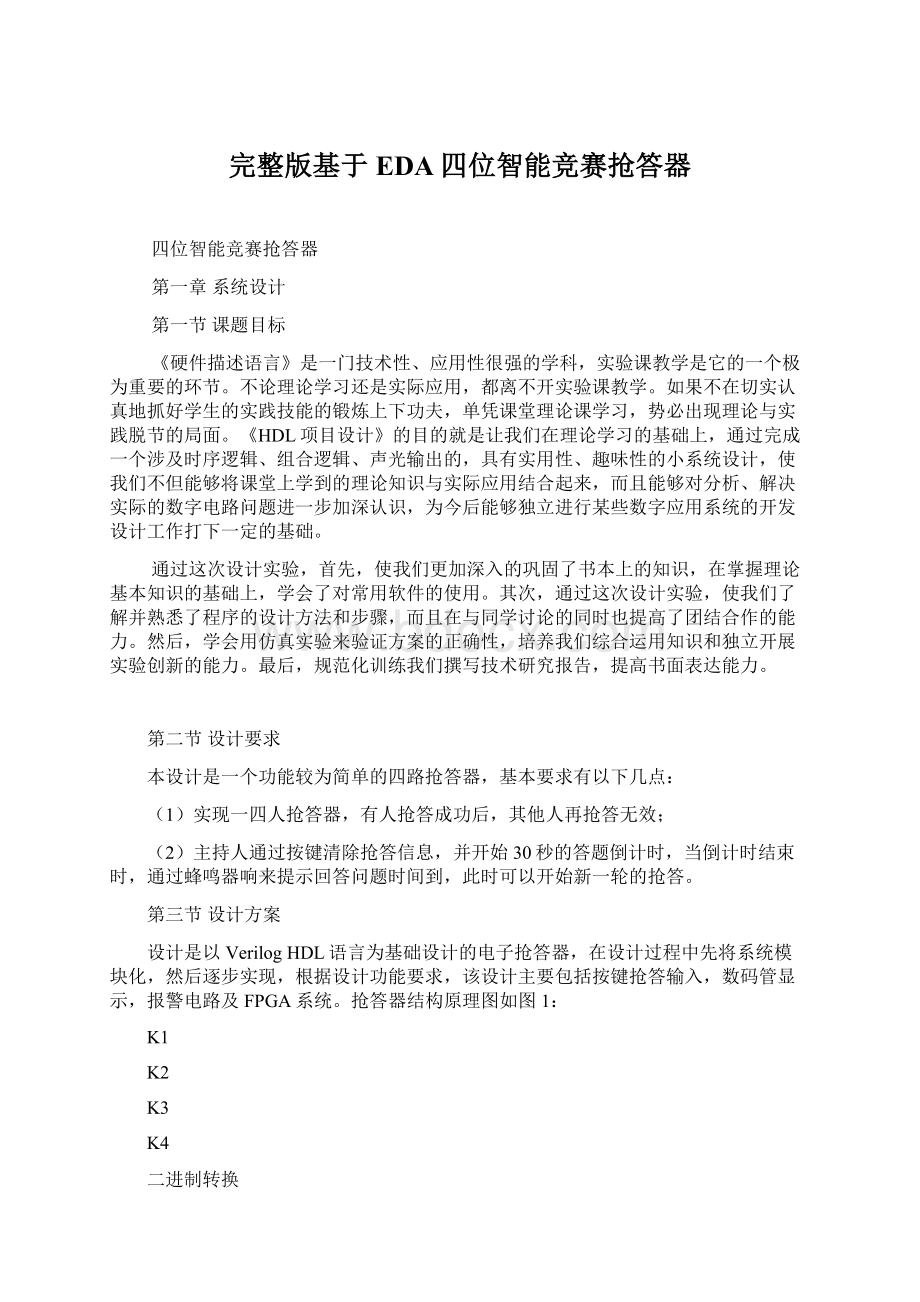

K4

二进制转换

数码管片选信号

倒计时模块

数码管译码电路

蜂鸣器

同步信号

数码管

显示模块

锁存电路

按键1

按键2

图1抢答器结构原理图

第二章系统分析与实现

第一节系统分析

该系统可实现要求中的最基本功能,除此之外还可以实现抢答时间限制的功能,其中,抢答成功者组号由静态显示的方法使用,使四个数码管同时显示其组号,同时,该抢答者对应的led灯亮。

若还有其他抢答者在其后按下按键,抢答无效,只取第一个抢答者信息。

第二节程序及程序功能介绍

一、端口定义部分

modulemain(reset,clock,din1,din2,din3,din4,judge,beep,wei,duan,beep,wei1,duan1);

inputreset,clock;

inputdin1,din2,din3,din4,judge;

output[3:

0]wei;

output[7:

0]duan;

outputbeep;

0]wei1;

0]duan1;

wireclk1k;

wireclk1hz;

fenpinuut1(reset,clock,clk1k,clk1hz);

qiangdeuut2(clock,din1,din2,din3,din4,judge,clk1hz,wei,duan);

daojishiuut3(reset,clk1k,clk1hz,beep,wei1,duan1);

Endmodule

二、抢答部分

本段程序实现基本的抢答功能,block为锁存信号,当有一组按下抢答按钮后,系统锁存,其他组别抢答无效;

同时通过f1向蜂鸣器发出信号,蜂鸣器1s表示抢答成功;

于此同时信号out输送给led灯,抢答成功者对应led灯亮;

seg_figure4为静态显示抢答成功的组号,预置数为”_”;

一组抢答成功后若其他组再抢答,数码管熄灭示警。

moduleqiangde(clock,din1,din2,din3,din4,judge,clk1_hz,wei,duan);

inputclock,judge;

inputdin1,din2,din3,din4;

inputclk1_hz;

reg[3:

reg[7:

regblock;

always@(posedgeclock)

begin

if(!

judge)

begin

block=0;

wei=4'

b1111;

duan=8'

hff;

end

else

if(!

din1)

begin

if(!

block)

begin

wei<

=4'

b1101;

duan<

=8'

hf9;

block=1;

end

end

elseif(!

din2)

block)

wei<

duan<

ha4;

block=1;

din3)

hb0;

din4)

h99;

end

endmodule

3、分频

modulefenpin(reset,clock,clk1k,clk1hz);

outputclk1k,clk1hz;

regclk1k;

regclk1hz;

reg[24:

0]count1;

reg[14:

0]count2;

always@(posedgeclockorposedgereset)

begin

if(reset)

count1<

=0;

elseif(count1==25'

d25000000)

begin

clk1hz<

=~clk1hz;

end

=count1+1;

count2<

elseif(count2==15'

d25000)

clk1k<

=~clk1k;

=count2+1;

四、抢答时限30s,倒计时到,蜂鸣器响

该部分功能:

当抢答倒计时30s结束时,若没有任何一组抢答成功,则向蜂鸣器发出信号,蜂鸣器响作为警报,提示此次抢答结束且该题作废。

moduledaojishi(reset,clk1_k,clk1_hz,beep,wei1,duan1);

inputreset,clk1_k,clk1_hz;

output[3:

output[7:

reg[5:

0]shi,ge;

0]data;

reg[4:

0]count;

reg[3:

reg[7:

regbeep;

regstate;

always@(posedgeclk1_hzorposedgereset)

count<

elseif(count>

=5'

d30)

=count;

=count+1;

always@(count)

if(count>

b10101)//21~30

begin

shi<

b00000;

ge<

b11110-count;

b01011)//11~20

b00001;

b10100-count;

elseif(count>

b00001)//1~10

b00010;

b01010-count;

else//0

b00011;

if(shi==0&

&

ge==0)

beep<

end

elsebeep<

=1;

always@(posedgeclk1_k)

wei1<

b0000;

elseif(state==1'

b1)

state<

=1'

b0;

=state+1'

b1;

case(state)

1'

b0:

beginwei1<

b0111;

data<

=ge;

b1:

b1011;

=shi;

default:

wei1<

endcase

always@(data)

case(data)

6'

b000000:

duan1=8'

b1100_0000;

b000001:

b1111_1001;

b000010:

b1010_0100;

b000011:

b1011_0000;

b000100:

b1001_1001;

b000101:

b1001_0010;

b000110:

b1000_0010;

b000111:

b1111_1000;

b001000:

b1000_0000;

b001001:

b1001_0000;

duan1=8'

b1111_1111;

第三章编译调试

第一节QuartusII的使用

(1)双击QuartusII软件快捷图标进入QuartusII集成开发环境,新建工程项目文件traffic.pof,并在该项目下新建Verilog源程序文件traffic.v,输入上面的程序代码并保存。

(2)然后为该工程项目选择一个目标器件并对相应的管脚进行锁定。

(3)对该工程文件进行编译处理,若在编译过程中发现错误,找出并更正错误直至成功为止。

(4)将CCITCPLD/FGPAJTAG下载电缆的两端分别接到PC机和CCITCPLD/FGPA实验仪上,再打开工作电源,执行下载命令把程序下载到CCITCPLD/FGPA实验仪的EPM1270T144C