八位七段数码管动态显示电路设计方案Word文档下载推荐.docx

《八位七段数码管动态显示电路设计方案Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《八位七段数码管动态显示电路设计方案Word文档下载推荐.docx(22页珍藏版)》请在冰豆网上搜索。

七段显示器之常见应用如下

Ø

可作为与数值显示相关之设计。

⏹电子时钟应用显示

⏹倒数定时器

⏹秒表

⏹计数器、定时器

⏹算数运算之数值显示器

二七段显示器显示原理

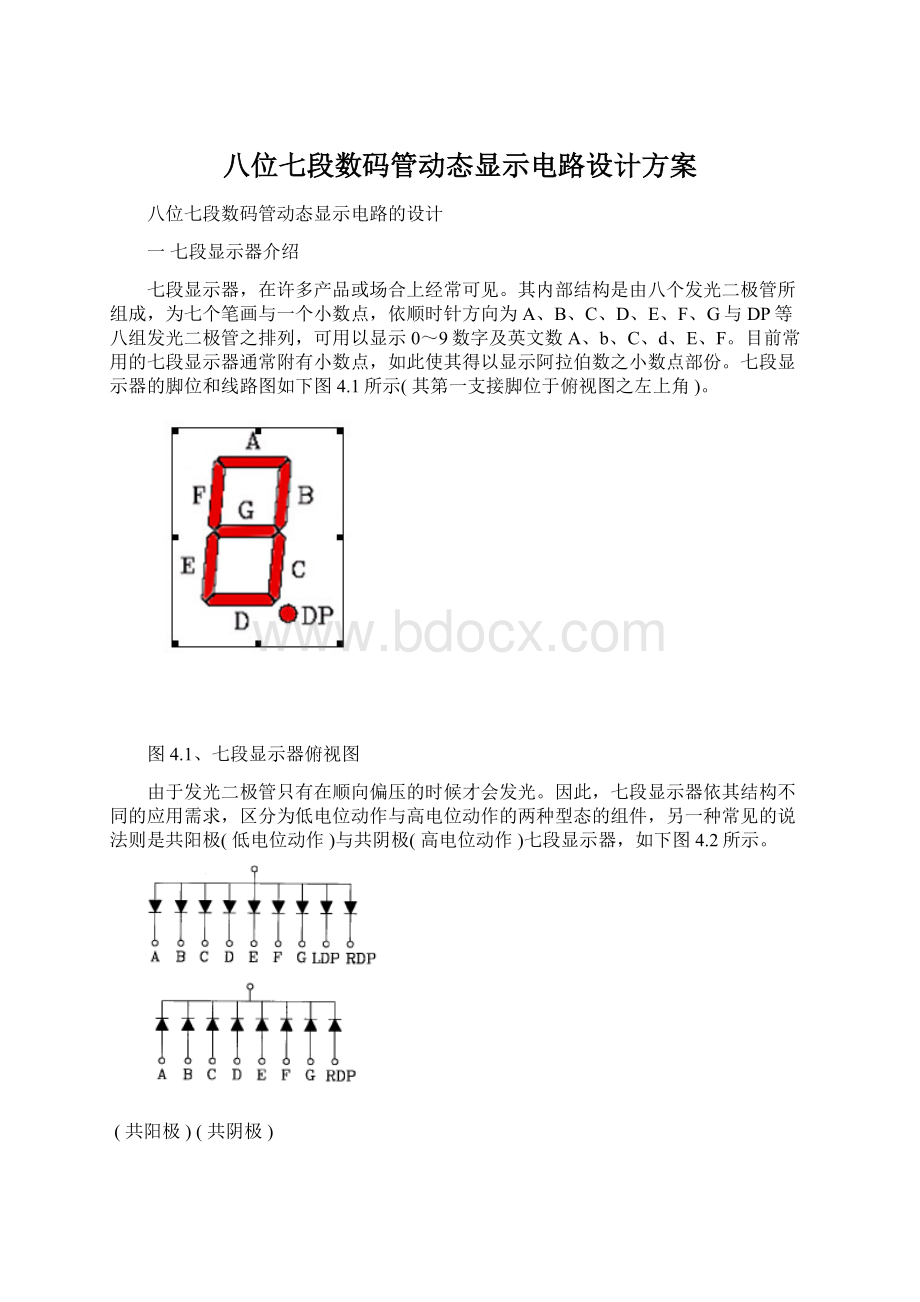

七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的(每一个二极管依位置不同而赋予不同的名称,请参见图4.1)。

我们可以简单的说,要产生数字,便是点亮特定数据的发光二极管。

例如要产生数字「0」,须只点亮A、B、C、D、E、F等节段的发光二极管;

要产生数字「5」,则须点亮A、C、D、F、G等节段发光二极管,以此类推,参见图4.6。

因此,以共阳极七段显示器而言,要产生数字「0」,必须控制CycloneIIFPGA芯片接连至A、B、C、D、E、F等接脚呈现“低电位”,使电路形成通路状态。

表4.1则为共阳极七段显示器显示之数字编码。

图4.6、七段显示器显示阿拉伯数字

表4.1、共阳极七段显示器显示数字编码

资料

DP

G

F

E

D

C

B

A

16进制

1

C0

F9

2

A4

3

B0

4

99

5

92

6

82

7

F8

8

80

本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验中时,数字时钟选择1KHZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

实验箱中的拨动开关与FPGA的接口电路,以及拨动开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数码管显示模块的电路原理如图4-2所示,

图4-2数字时钟信号模块电路原理

三实验步骤

(本实验用VHDL文本语言实现八位七段数码管动态显示,当然也可用Quartus的图形输入法实现八位七段数码管动态显示)

1.下面我们建立一个八位七段数码管动态显示的VHDL工程

1)选择开始>

程序>

Altera>

QuartusII5.1,运行QUARTUSII软件。

或者双击桌面上的QUARTUSII的图标运行QUARTUSII软件,出现如图1-3所示。

图1-3QUARTUSII软件运行界面

2)选择软件中的菜单File>

NewProjectWizard,新建一个工程。

如图1-4所示。

图1-4新建工程对话框

3)点击图1-4中的NEXT进入工作目录,工程名的设定对话框如图1-5所示。

第一个输入框为工程目录输入框,用户可以输入如e:

/eda等工作路径来设定工程的目录,设定好后,所有的生成文件将放入这个工作目录。

第二个输入框为工程名称输入框,第三个输入框为顶层实体名称输入框。

用户可以设定如EXP1,一般情况下工程名称与实体名称相同。

使用者也可以根据自已的实际情况来设定工程名和顶层文件名。

注:

本处的顶层文件名必须和程序的实体名一致,否则编译会出错。

图1-5指定工程名称及工作目录

4)点击NEXT,进入下一个设定对话框,按默认选项直接点击NEXT进行器件选择对话框。

如图1-6所示。

这里我们以选用CycloneII系列芯片EP2C35F672C8为例进行介绍。

用户可以根据使用的不同芯片来进行设定。

图1-6器件选择界面

首先在对话框的左上方的Family下拉菜单中选取CycloneII,在中间右边的Speedgrade下拉菜单中选取8,在左下方的Availabledevices框中选取EP2C35F672C8,点击NEXT完成器件的选取,进入EDATOOL设定界面如图1-7所示。

图1-7EDATOOL对话框

5)按默认选项,点击Next出现新建工程以前所有的设定信息,如图1-8所示,点击Finish完成新建工程的建立。

图1-8新建工程信息

2、建立VHDL设计文件

1)在创建好设计工程后,选择File>

NEW…菜单,出现图1-9所示的新建设计文件类型选择窗口。

这里我们以建立VHDL设计文件为例进行说明。

图1-9新建设计文件选择窗口

2)在New对话框(图1-9)中选择DeviceDesignFiles页下的VHDLFile,点击OK按钮,打开图形编辑器对话框,如图1-10所示。

图中标明了常用的每个按钮的功能

3)在文本编辑器中输入如下VHDL程序:

--下面是引用库-------------------------------------

libraryieee;

--库函数

useieee.std_logic_1164.all;

--定义了std_logic数据类型及相应运算

useieee.std_logic_arith.all;

--定义了signed和unsigned数据类型、相应运算和相关类型转换函数

useieee.std_logic_unsigned.all;

--定义了一些函数,可以使std_logic_vector类

--型被当作符号数或无符号数一样进行运算

--------------------------------------------------------------------

--下面是构造实体

entityexp4is--exp4为实体名

port(clk:

instd_logic;

--定义动态扫描时钟信号

key:

instd_logic_vector(3downto0);

--定义四位输入信号

ledag:

outstd_logic_vector(6downto0);

--定义七位输出信号

del:

outstd_logic_vector(2downto0)--定义八位数码管位置显示信号

);

endexp4;

--结束实体

architecturewhbkrcofexp4is--whbkrc为结构体名

begin--以begin为标志开始结构体的描述

process(clk)--进程,clk变化时启动进程

variabledount:

std_logic_vector(2downto0);

--变量,计数

begin

ifclk'

eventandclk='

1'

then--检测时钟上升沿

dount:

=dount+1;

--计数器dount累加

endif;

del<

=dount;

--片选信号

endprocess;

--结束进程

process(key)--进程,key变化时启动进程

casekeyis

when"

0000"

=>

ledag<

="

0111111"

;

--七段数码管显示0

0001"

0000110"

--1

0010"

1011011"

--2

0011"

1001111"

--3

0100"

1100110"

--4

0101"

1101101"

--5

0110"

1111101"

--6

0111"

0000111"

--7

1000"

1111111"

--8

1001"

1101111"

--9

1010"

1110111"

--R

1011"

1111100"

--b

1100"

0111001"

--C

1101"

1011110"

--d

1110"

1111001"

--E

1111"

1110001"

--F

whenothers=>

null;

endcase;

--结束进程

endwhbkrc;

--结束结构体

关于VHDL,我们以上面八位七段数码管显示程序为例来解释VHDL的语法构成,以使大家对VHDL有个整体的把握。

一个VHDL程序有三部分构成,其为:

1.库和包library(设计资源);

2.实体entity(外部端口)

3.结构体architecture(内部结构)

①库和包library(设计资源)的介绍

1.1useieee.std_logic_1164.all;

1.2useieee.std_logic_arith.all;

--定义了signed和unsigned数据类型、相应运算

--和相关类型转换函数

1.3