EDA技术实验报告Word文档下载推荐.docx

《EDA技术实验报告Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《EDA技术实验报告Word文档下载推荐.docx(31页珍藏版)》请在冰豆网上搜索。

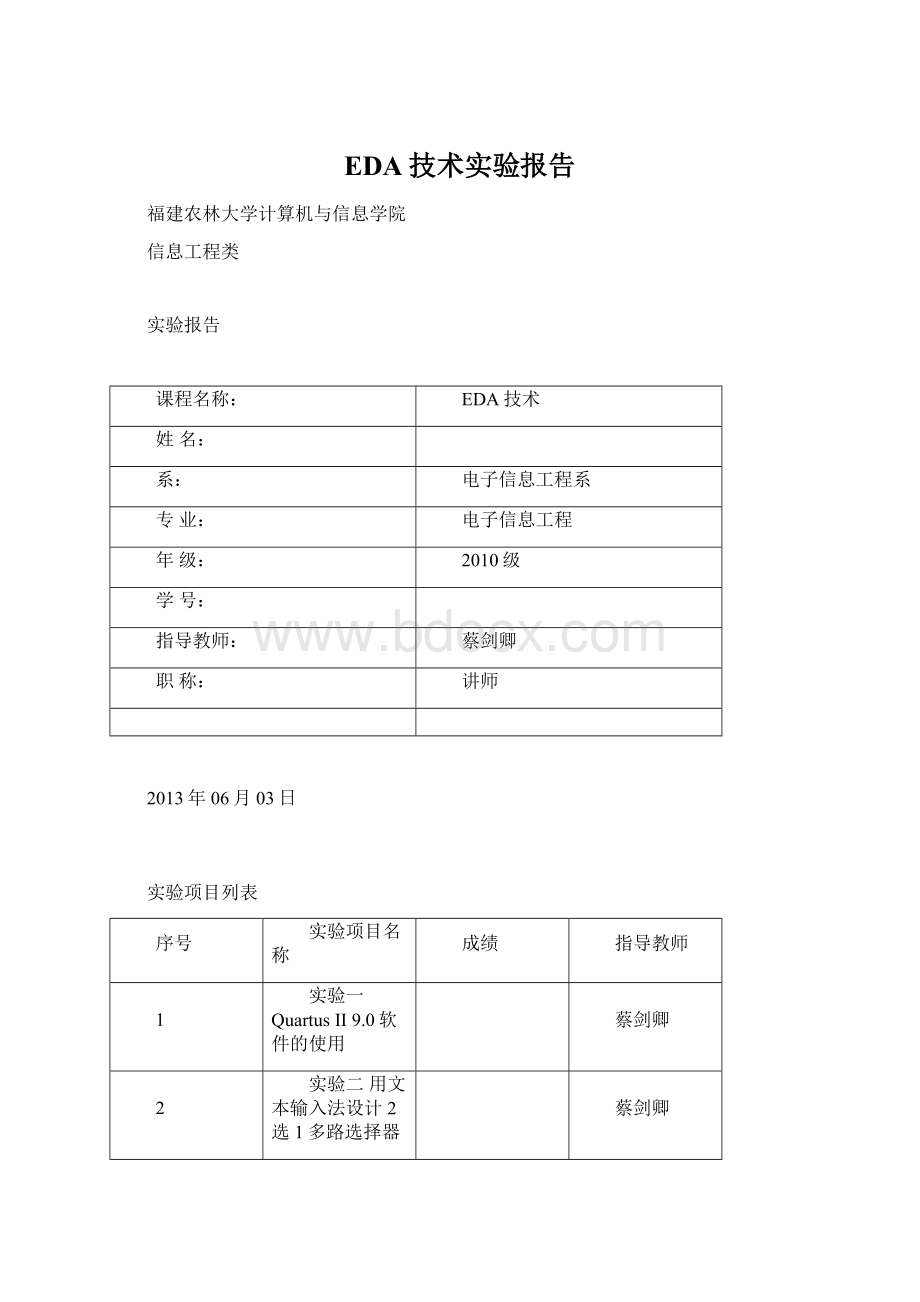

实验项目列表

序号

实验项目名称

成绩

指导教师

1

实验一 QuartusII9.0软件的使用

2

实验二用文本输入法设计2选1多路选择器

3

实验三用文本输入法设计7段数码显示译码器

4

实验四用原理图输入法设计8位全加器

5

实验五乐曲硬件演奏电路的设计

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

福建农林大学计算机与信息学院信息工程类实验报告

电子信息工程专业:

电子信息工程年级:

2010级

姓名:

学号:

实验课程:

EDA技术

实验室号:

__田实405实验设备号:

实验时间:

2013年5月18日

指导教师签字:

成绩:

实验一QuartusII9.0软件的使用

1.实验目的和要求

本实验为验证性实验,其目的是熟悉QuartusII9.0软件的使用,学会利用QuartusII9.0软件来完成整个EDA开发的流程。

2.实验原理

利用VHDL完成电路设计后,必须借助EDA工具中的综合器、适配器、时序仿真器和编程器等工具进行相应的处理后,才能使此项设计在FPGA上完成硬件实现,并得到硬件测试,从而使VHDL设计得到最终的验证。

QuartusII是Altera提供的FPGA/CPLD开发集成环境,包括模块化的编译器,能满足各种特定设计的需要,同时也支持第三方的仿真工具。

3.主要仪器设备(实验用的软硬件环境)

实验的硬件环境是:

微机一台

GW48EDA实验开发系统一套

电源线一根

十芯JTAG口线一根

USB下载线一根

USB下载器一个

实验的软件环境是:

QuartusII9.0软件

4.操作方法与实验步骤

利用QuartusII9.0软件实现EDA的基本设计流程:

创建工程、编辑文本输入设计文件、编译前设置、全程编译、功能仿真。

利用QuartusII9.0软件实现引脚锁定和编译文件下载。

利用QuartusII9.0软件实现原理图输入设计文件的编辑和产生相应的原理图符号元件。

5.实验内容及实验数据记录

6.实验数据处理与分析

从而学会使用QuartusII9.0软件。

7.质疑、建议、问题讨论

QuartusII和Modelsim软件环境设置比较多,学习时要认真细心。

VHDL语言是硬件语言,一般是并行执行,与C语言等软件语言不太一样,这点学习时要注意。

VHDL有些关键词也比较特别,例如eslif不能错写成elseif。

通过本实验编写的16进制加法器和仿真结果,我们能清楚和直观地看到16进制加法器的基本功能。

在调试过程中出现的error信息要特别关注,根据错误提示信息,对其进行正确改正。

通过这次实验,我掌握EDA工具QuartusII软件的基本使用方法,能够建立项目并编写程序和调试、仿真,也加强了VHDL程序的编写能力。

_田实405实验设备号:

2013年5月18日

本实验为综合性实验,综合了简单组合电路逻辑、QuartusII的使用方法、多层次电路设计、仿真和硬件测试等内容。

其目的是熟悉QuartusII的VHDL文本设计流程全过程。

2选1多路选择器真值表

s

a

b

y

L

×

H

首先利用QuartusII完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,然后进行仿真。

最后在实验系统上进行硬件测试,实际验证本项实验的功能。

将设计好的2选1多路多路选择器看成是一个元件mux21a,利用元件例化语句描述下图,并将此文件放在同一目录E:

\muxfile中。

程序设计:

ENTITYmux21aIS

PORT(a,b,s:

INBIT;

y:

OUTBIT);

ENDENTITYmux21a;

ARCHITECTUREoneOFmux21aIS

BEGIN

PROCESS(a,b,s)

BEGIN

IFs='

0'

THEN

y<

=a;

ELSE

y<

=b;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREone;

软件编译:

仿真分析:

硬件测试和实验过程:

仿真结果出现延时,应该将a,b,s的周期增大些,且要保证单位为us,刚开始做实验内容时,文件夹名字与程序中所用的实体名不一致,导致程序运行时无法找到文件夹,无法正常工作,经更改后,正常运行,同时文件夹名字不用汉字和数字,以免出错。

每次修改过程都应该注意保存,才能将修改的结果反映到所输出的波形中,刚开始常常忘记,经过多次操作后才能够熟练运用。

本实验为综合性实验,综合了简单组合电路逻辑,QuartusII的使用方法,多层次电路设计、仿真和硬件测试等内容。

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

7段数码显示译码器的输出信号LED7S的7位分别接共阴7段数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:

g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;

接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,此时实体说明中的LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0)应改为…(7DOWNTO0)。

利用QuartusII完成7段数码显示译码器的文本编辑输入(decl7s.vhd)和仿真测试等步骤,最后在实验系统上进行硬件测试,实际验证本项实验的功能。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDECL7SIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

END;

ARCHITECTUREoneOFDECL7SIS

PROCESS(A)

BEGIN

CASEAIS

WHEN"

0000"

=>

LED7S<

="

0111111"

;

0001"

0000110"

WHEN"

0010"

1011011"

0011"

1001111"

0100"

1100110"

0101"

1101101"

0110"

1111101"

0111"

0000111"

1000"

1111111"

1001"

1101111"

WHEN"

1010"

1110111"

1011"

1111100"

1100"

0111001"

1101"

1011110"

1110"

1111001"

1111"

1110001"

WHENOTHERS=>

NULL;

ENDCASE;

ENDPROCESS;

END

仿真分析

本实验通过按键8、键7、键6和键5,来观察数码8的输出。

实验内容较多,但不复杂,重要的是熟练。

对于程序语言不大会写,立化操作更是不会,幸亏在同学的帮助下,理解了实验的操作思路,圆满完成了实验。

今后还得倍加努力,多写多练,孰能生巧。

福建农林大学计算机与信息学院信息工程类实验报告

__田实405实